本实验基于xilinx ARTIX-7芯片验证实现,有时间有兴趣的朋友可在其他FPGA芯片上实现验证。

当大家看到《xilinx verilog语法技巧(三)–RAM的初始化》文章的时候很多人认为initial语句,$readmemb语句均是不可综合语句(只能用来写测试文件),但是xilinx的综合器已经悄然改变了这一点。

rams_init_file源码:

// Initializing Block RAM from external data file // Binary data // File: rams_init_file.v module rams_init_file (clk, we, addr, din, dout); input clk; input we; input [5:0] addr; input [31:0] din; output [31:0] dout; reg [31:0] ram [0:63]; reg [31:0] dout; initial begin $readmemb("rams_init_file.data",ram); end always @(posedge clk) begin if (we) ram[addr] <= din; dout <= ram[addr]; end endmodule

rams_init_file.data源文件:

00001110110000011001111011000110 00101011001011010101001000100011 01110100010100011000011100001111 01000001010000100101001110010100 00001001101001111111101000101011 00101101001011111110101010100111 11101111000100111000111101101101 10001111010010011001000011101111 00000001100011100011110010011111 11011111001110101011111001001010 11100111010100111110110011001010 11000100001001101100111100101001 10001011100101011111111111100001 11110101110110010000010110111010 01001011000000111001010110101110 11100001111111001010111010011110 01101111011010010100001101110001 01010100011011111000011000100100 11110000111101101111001100001011 10101101001111010100100100011100 01011100001010111111101110101110 01011101000100100111010010110101 11110111000100000101011101101101 11100111110001111010101100001101 01110100000011101111111000011111 00010011110101111000111001011101 01101110001111100011010101101111 10111100000000010011101011011011 11000001001101001101111100010000 00011111110010110110011111010101 01100100100000011100100101110000 10001000000100111011001010001111 11001000100011101001010001100001 10000000100111010011100111100011 11011111010010100010101010000111 10000000110111101000111110111011 10110011010111101111000110011001 00010111100001001010110111011100 10011100101110101111011010110011 01010011101101010001110110011010 01111011011100010101000101000001 10001000000110010110111001101010 11101000001101010000111001010110 11100011111100000111110101110101 01001010000000001111111101101111 00100011000011001000000010001111 10011000111010110001001011100100 11111111111011110101000101000111 11000011000101000011100110100000 01101101001011111010100011101001 10000111101100101001110011010111 11010110100100101110110010100100 01001111111001101101011111001011 11011001001101110110000100110111 10110110110111100101110011100110 10011100111001000010111111010110 00000000001011011111001010110010 10100110011010000010001000011011 11001010111111001001110001110101 00100001100010000111000101001000 00111100101111110001101101111010 11000010001010000000010100100001 11000001000110001101000101001110 10010011010100010001100100100111

tb_rams_init_file测试顶层文件:

`timescale 1ns / 1ps

module tb_rams_init_file(

input clk,

input reset,

output [2:0] led_rgb0,

output [2:0] led_rgb1,

output [2:0] led_rgb2,

output [2:0] led_rgb3

);

reg [5:0] addr;

wire [31:0] dout;

reg [27:0] cnt;

assign led_rgb0 = dout[2:0];

assign led_rgb1 = dout[5:3];

assign led_rgb2 = dout[8:6];

assign led_rgb3 = dout[11:9];

always @(posedge clk ) begin

if(reset==1'b1) begin

cnt <= 28'd0;

addr <= 0;

end

else if(cnt == 28'd100000000)begin//1s

cnt <= 28'd0;

addr <= addr +1;

end

else begin

cnt <= cnt + 1;

addr <= addr;

end

end

rams_init_file u_rams_init_file(

.clk(clk),

.we(1'b0),

.addr(addr),

.din(32'b0),

.dout(dout));

endmodule

约束文件(根据自己板卡):

set_property PACKAGE_PIN E3 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports clk] set_property PACKAGE_PIN D9 [get_ports reset] set_property IOSTANDARD LVCMOS33 [get_ports reset] set_property PACKAGE_PIN E1 [get_ports led_rgb0[0]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb0[0]] set_property PACKAGE_PIN G6 [get_ports led_rgb0[1]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb0[1]] set_property PACKAGE_PIN F6 [get_ports led_rgb0[2]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb0[2]] set_property PACKAGE_PIN G4 [get_ports led_rgb1[0]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb1[0]] set_property PACKAGE_PIN G3 [get_ports led_rgb1[1]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb1[1]] set_property PACKAGE_PIN J4 [get_ports led_rgb1[2]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb1[2]] set_property PACKAGE_PIN H4 [get_ports led_rgb2[0]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb2[0]] set_property PACKAGE_PIN J3 [get_ports led_rgb2[1]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb2[1]] set_property PACKAGE_PIN J2 [get_ports led_rgb2[2]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb2[2]] set_property PACKAGE_PIN K2 [get_ports led_rgb3[0]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb3[0]] set_property PACKAGE_PIN K1 [get_ports led_rgb3[1]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb3[1]] set_property PACKAGE_PIN H6 [get_ports led_rgb3[2]] set_property IOSTANDARD LVCMOS33 [get_ports led_rgb3[2]]

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RAM

+关注

关注

8文章

1398浏览量

119798 -

Xilinx

+关注

关注

73文章

2192浏览量

129881 -

Verilog

+关注

关注

30文章

1370浏览量

114107 -

FPGA芯片

+关注

关注

3文章

250浏览量

40851

原文标题:RAM初始化的下板验证(Xilinx)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

电源关闭几秒后,Ram数据不会初始化

电源关闭几秒后,Ram数据不会初始化以上来自于谷歌翻译以下为原文 Ram data not init after power off for seconds

发表于 07-10 14:03

s32k146如何初始化RAM?

我在当前项目中使用 s32k146。因为我需要初始化 RAM,除了上电复位之外的每次复位的特定部分。(On Power On Reset 应初始化所有数据)。有什么办法可以做到这一点吗?

发表于 03-31 07:36

手机模块初始化向导

手机模块初始化向导:为了刚好的对手机模块进行初始化,所以把最基本的向导写下来.本向导适用于本公司的西门子TC35I和华为GT9000模块。一、在初始化手机模块前,请先确定DT

发表于 09-18 09:41

•17次下载

uboot和内核里phy的初始化_内核里的双网络配置及phy的初始化

uboot 和内核里 phy 的初始化,以及内核里的双网络配置及 phy 的初始化。 本文以盈鹏飞嵌入式的CoM-335x(基于AM335x)核心板及网络芯片LAN8720 为例,说明修改步骤

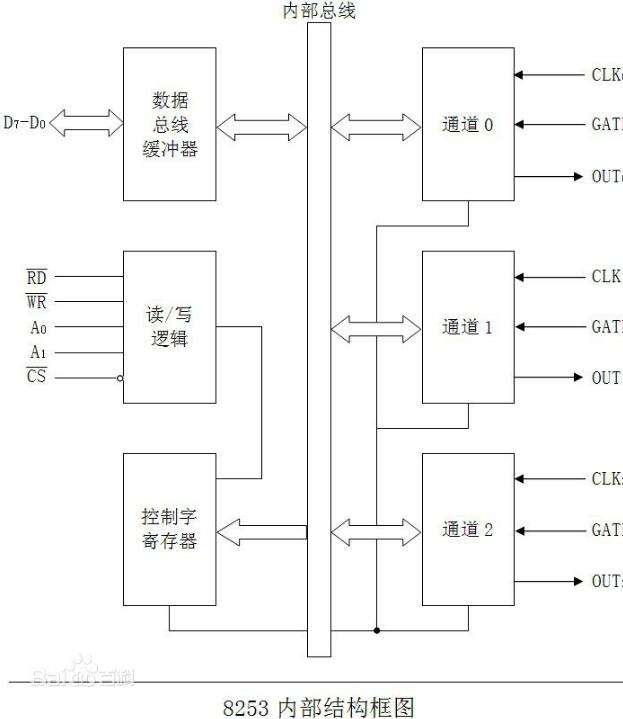

8253初始化程序分享_8253应用案例

本文首先介绍了8253概念及8253各通道的工作方式,其次详细介绍了8253初始化要求及编程,最后用一个例子介绍了8253的初始化程序。

发表于 05-23 15:52

•2.3w次阅读

如何设置STM32单片机非初始化数据变量不被零初始化

一些产品,当系统复位后(非上电复位),可能要求保持住复位前RAM中的数据,用来快速恢复现场,或者不至于因瞬间复位而重启现场设备。而keil mdk在默认情况下,任何形式的复位都会将RAM区的非

发表于 01-02 15:56

•8988次阅读

在51平台下初始化文件的引入导致全局变量无法初始化的问题如何解决

本文档的主要内容详细介绍的是在51平台下初始化文件的引入导致全局变量无法初始化的问题如何解决。

发表于 08-20 17:31

•0次下载

想要对RAM初始化该怎么操作

RAM的初始化并没有那么神秘,如果是采用Xilinx的IP Core,只需提供一个.coe文件,其内容就是RAM的初始值,只需要注意coe文件的格式就好,这里就不再赘述。

GraniStudio:初始化例程

1.文件运行 导入工程 双击运行桌面GraniStudio.exe。 通过引导界面导入初始化例程,点击导入按钮。 打开初始化例程所在路径,选中初始化.gsp文件,点击打开,完成导入。 2.功能

RAM初始化的下板验证

RAM初始化的下板验证

评论