》ROM的初使化

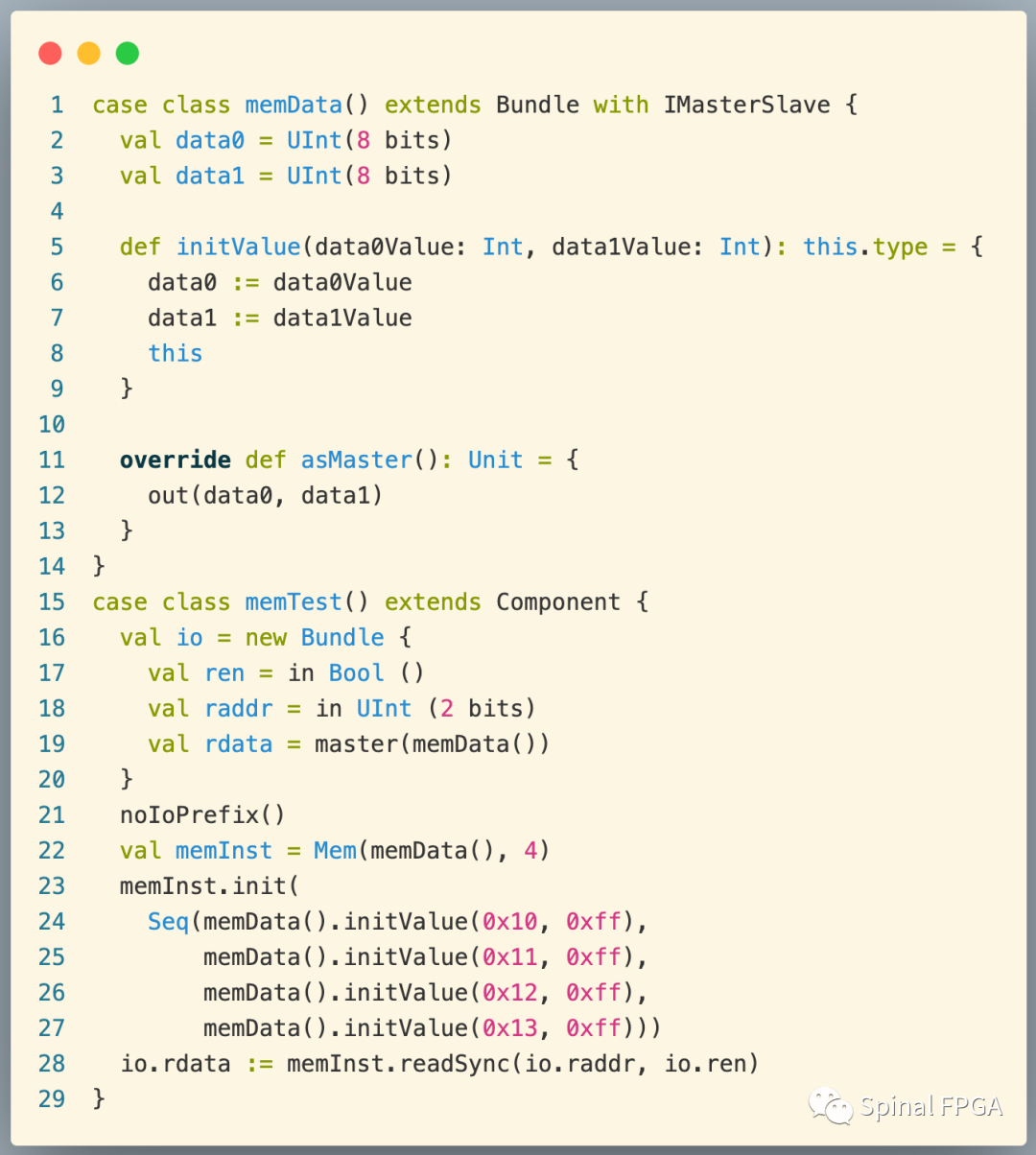

在之前的文章《Mem初始化太复杂?》中曾提到在SpinalHDL中如何对Mem进行初始化。以下面的代码为例:

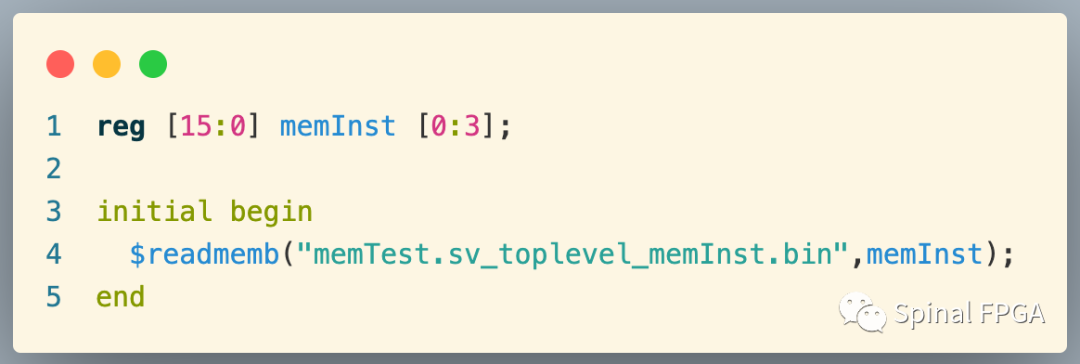

在默认情况下,SpinalHDL在生成代码时会同时生成一个bin文件及一个RTL代码文件。在RTL代码中,会通过readmemb函数来载入初始化内容:

这么做没什么问题,平常我们这么做也较为经常。

这里面唯一不便的就是当我们用于跑仿真(直接用SpinalHDL仿真框架)或者用于制作工程时需要自己注意调整工程里所用到的bin文件的位置。

》inlineRom

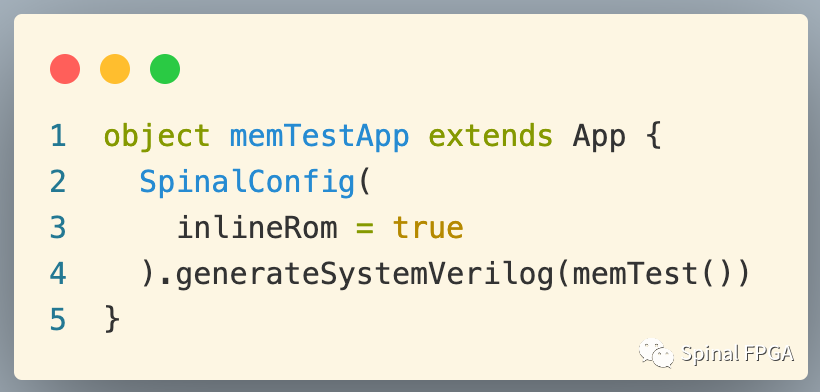

在SpinalHDL中我们也可以通过SpinalConfig指定在生成RTL代码时直接将ROM初始化的设置放置在RTL文件中,通过设置inlineRom为true:

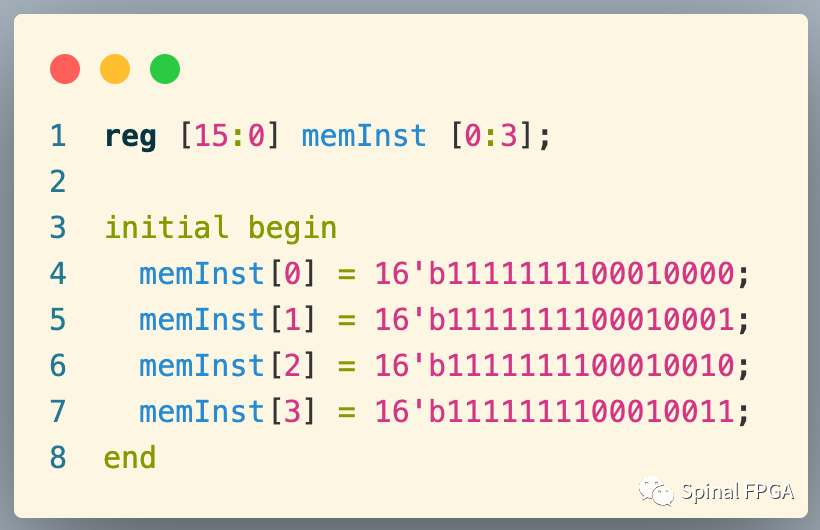

这时生成RTL代码时将不会再生成单独的bin文件,而是直接将ROM初始化放置在RTL代码中:

如此,无论是制作工程还是在跑仿真时,只需关注RTL代码的位置即可。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ROM

+关注

关注

4文章

579浏览量

89372 -

HDL

+关注

关注

8文章

332浏览量

49041 -

RTL

+关注

关注

1文章

395浏览量

62875 -

BIN文件

+关注

关注

0文章

27浏览量

9052

原文标题:二合一:ROM初始化放置到RTL中

文章出处:【微信号:Spinal FPGA,微信公众号:Spinal FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

关于Quartus II中ROM初始化数据.mif格式文件,在Modelsim中仿真...

各位大哥;小弟最近刚学FPGA,有个问题不懂,希望各位路过的大哥不吝赐教!我在Quartus II中调用了一个lpm_rom,用存放正弦波数值的.mif 格式文件去

发表于 03-24 18:02

FPGA片内ROM初始化文档创建

文档创建既然是ROM,那么我们就必须实现给它准备好数据,然后在FPGA实际运行时,我们直接使用这些预存储好的数据就行。Xilinx FPGA的片内ROM支持初始化数据配置。如图所示,我

发表于 04-08 09:34

在SpinalHDL的设计中集成现有RTL设计(IP)的渠道——BlackBox

,在SpinalHDL例例化一个带层次结构的RTL代码(RTL代码本身没什么意义,主要展示带层次结构的R

发表于 06-22 14:59

在SpinalHDL中关于casez的使用

SpinalHDL中的switch在之前的文章中曾提到过SpinalHDL中switch的使用:通常情况下,switch对应着我们日常Ver

发表于 07-06 10:59

就Bits数据类型的初始化及使用方式做一个总结

Bits:初始化Bits意味这一组有Bool类型组成的向量,类似与我们在Verilog中的多比特位宽变量。在SpinalHDL

发表于 07-12 16:31

在SpinalHDL中的代码组织结构如何实现Component参数化设计呢

,SpinalHDL在生成RTL时,会检测在Bundle中的所有元素是否都声明了端口方向。有一点是像上面的MyAdder将端口声明放在Bun

发表于 07-21 14:20

FPGA的ROM初始化问题讨论

本文讨论FPGA的ROM初始化问题,详细介绍mit文件的创建与使用。利用FPGA实现的ROM只能认为器件处于用户状态时具备ROM功能。使用时

发表于 02-08 14:24

•5962次阅读

objc源码中NSObject如何进行初始化

+ alloc 和 - init 这一对我们在 iOS 开发中每天都要用到的初始化方法一直困扰着我, 于是笔者仔细研究了一下 objc 源码中 NSObject 如何进行

发表于 09-26 09:58

•0次下载

在51平台下初始化文件的引入导致全局变量无法初始化的问题如何解决

本文档的主要内容详细介绍的是在51平台下初始化文件的引入导致全局变量无法初始化的问题如何解决。

发表于 08-20 17:31

•0次下载

根据MATLAB中的伪随机交织器产生的交织图案初始化到ROM的实验

根据MATLAB中的伪随机交织器产生的交织图案初始化到ROM的实验(嵌入式开发工程师报名)-根据MATLAB中的伪随机交织器产生的交织图案初始化

发表于 07-30 16:19

•13次下载

labview运行后如何初始化

LabVIEW是一款强大的图形化编程软件,在运行之前通常需要进行一些初始化操作。本文将详细介绍LabVIEW运行前的初始化过程,并提供了一些常用的初

在SpinalHDL中如何将ROM的初始化放置在RTL文件中?

在SpinalHDL中如何将ROM的初始化放置在RTL文件中?

评论