芯片在互连完成之后就到了封装的步骤,即将芯片与引线框架“包装”起来。这种成型技术有金属封装、塑料封装、陶瓷封装等,从成本的角度和其他方面综合考虑,塑料封装是最为常用的封装方式,它占据了90%左右的市场。

塑料封装的成型技术有多种,包括转移成型技术(Transfer Molding)、喷射成型技术(Inject Molding)、预成型技术(Premolding)等,但最主要的成型技术是转移成型技术。转移成型使用的材料一般为热固性聚合物(Thermosetting Polymer)。今天 【科准测控】 小编就来介绍一下半导体芯片封装的转移成型技术以及芯片去飞边毛刺、上焊锡流程,一起往下看吧!

1、成型技术

所谓的热固性聚合物是指低温时聚合物是塑性的或流动的,但将其加热到一定温度时,即发生所谓的交联反应(Cross-Linking),形成刚性固体。若继续将其加热,则聚合物只能变软而不可能熔化、流动。

在塑料封装中使用的典型成型技术的工艺过程如下,将已贴装芯片并完成引线键合的框架带置于模具中,将塑封的预成型块在预热炉中加热(预热温度9095℃之间),然后放进转移成型机的转移罐中。在转移成型活塞的压力下,塑封料被挤压到浇道中,经过浇口注人模腔(在整个过程中,模具温度保持在170175℃)。塑封料在模具中快速固化,经过一段时间的保压,使得模块达到一定硬度,然后用顶杆顶出模块,成型过程就完成了。

用转移成型法密封IC芯片有许多优点技术和设备都比较成熟,工艺周期短,成本低,几乎没有后整理方面的问题,适合于大批量生产。当然,它也有一些明显的缺点塑封料的利用率不高(在转移罐、壁和浇道中的材料均无法重复利用,约有20%~40%的塑封料被浪费),使用标准的框架材料,对于扩展转移成型技术至较先进的封装技术(如TAB)不利,对于高密度封装有限制。

转移成型技术的设备包括加热器、压机、模具和固化炉。在高度自动化的生产设备中,产品的预热、模具的加热和转移成型操作都在同一台机械设备中完成,并由计算机实施控制。目前,转移成型技术的自动化程度越来越高,预热、框架带的放置、模具放置等工序都可以达到完全自动化,塑封料的预热控制、模具的加热和塑封料都由计算机自动编程控制完成,劳动生产率大大提高。

对于大多数塑封料而言,在模具中保压几分钟后,模块的硬度足可以达到要求并顶出,但是,聚合物的固化(聚合)并未全部完成。由于材料的聚合度(固化程度)强烈影响材料的玻璃化转变温度及热应力,所以,促使材料全部固化以到达一个稳定的状态,对于提高元器件可靠性是十分重要的。后固化是提高塑封料聚合度必需的工艺步骤,一般后固化条件为170175℃,24h。目前,也发展了一些快速固化的塑封料,在使用这些材料时可以省去后固化工序,提高生产效率。

2、去飞边毛刺

封胶完后需先将引线架上多余的残胶去除,并且经过电镀以增加外引脚的导电性及抗氧化性,而后再进行剪切成型。若是塑封料只在模块外的引线架上形成薄薄的一层,面积也很小,通常称为树脂溢出。若渗出部分较多、较厚,则称为毛刺(Flash)或是飞边毛刺(Flash and Strain)。造成溢料或毛刺的原因很复杂,一般认为是与模具设计、注模条件及塑封料本身有关。毛刺的厚度一般要薄于10μm,它给后续工序如切筋打弯等工序带来麻烦,甚至会损坏机器。因此,在切筋打弯工序之前,要进行去飞边毛刺(Deflash)工序。

随着模具设计的改进以及严格控制注模条件,毛刺问题越来越少了。在一些比较先进的封装工艺中,已不需要再进行去飞边毛刺的工序了。

去飞边毛刺工序工艺主要有介质去飞边毛刺(Media Deflash)、溶剂去飞边毛刺(Solvent Deflash)、水去飞边毛刺(Water Deflash)。另外,当溢出塑封料发生在引线架堤坝(Dam Bar)背后时,可用切除(Dejunk)工艺。其中,介质和水去飞边毛刺的方法用得最多。用介质去飞边毛刺时,是将研磨料如粒状塑料球和高压空气一起冲洗模块。在去飞边毛刺过程中,介质会将引线架引脚的表面轻微擦毛,这将有助于焊料和金属引线架的粘连。在以前曾用天然的介质,如粉碎的胡桃壳和杏仁核,但由于它们会在引线架表面残留油性物质而被放弃。

用水去飞边毛刺工艺是利用高压的水流来冲击模块,有时也会将研磨料和高压水流一起使用。用溶剂来去飞边毛刺通常只适用于很薄的毛刺。溶剂包括N-甲基吡咯烷酮(NMP)或双甲基呋喃(DMF)。

3、上焊锡

封装后引线架外引脚的后处理可以是电镀(Solder Plating)或是浸锡(Solder Dipping)工艺,该工序是在引线架引脚上做保护性镀层,以增加其可焊性。

电镀目前都是在流水线式的电镀槽中进行,包括首先进行清洗,再在不同浓度的电镀槽中进行电镀,然后冲洗、吹干,最后放入烘箱中烘干。浸锡首先也是清洗工序,然后将预处理后的器件在助焊剂中浸泡,再浸入熔融铅锡合金镀层(63%Sn-37%Pb)。工艺流程为:去飞边→去油→去氧化物→浸助焊剂→热浸锡→清洗→烘干。

比较这两种方法,浸锡容易引起镀层不均匀,一般是由于熔融焊料的表面张力的作用使得浸锡部分中间厚、边上薄。而电镀的方法会造成所谓“狗骨头”(Dog-Bone)的问题,即角周围厚、中间薄,这是因为在电镀的时候容易造成电荷聚集效应。更大的问题是电镀液容易造成离子污染。

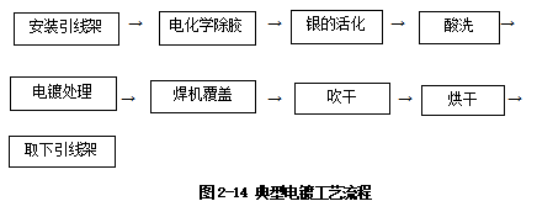

焊锡的成分一般是63%Sn-37%Pb,这是一种低共熔合金,其熔 银的活化点在183~184℃之间。也有用成分为85%Sn-15%Pb、90%Sn-10%Pb、95%Sn-5%Pb的,有的日本公司甚至用98%Sn-2%Pb的焊料。减少铅的用量,主要是对于环境的考虑,因为铅对环境的影响正日益引起人们的高度重视。而镀钯工艺则可以避免铅对环境污染的问题。但是,由于通常钯的黏性不太好,需要先镀一层较厚的、较密的、富镍的阻挡层,钯层的厚度仅为76μm(3mil)。由于钯层可以承受成型温度,因此可以在成型之前完成引线架的上焊锡工艺。并且,钯层对于芯片粘结和引线键合都适用,可以避免在芯片粘结和引线键合之前必须对芯片焊盘和引线架内引脚进行选择性镀银(以增加其粘结性),因为镀银时所用的电镀液中含有氰化物,给安全生产和废物处理带来麻烦。(典型电镀工艺流程如图2-14所示。)

科准测控W260推拉力测试机

好了,以上就是小编分享的半导体集成电路封装成型技术及去飞边毛刺、上焊锡流程介绍了!希望对大家能有所帮助。关于半导体集成电路芯片、推拉力机、封装、焊接强度等如果您还有不明白的,欢迎给我们私信或留言,科准的技术团队也会为您解答疑惑!

审核编辑 黄宇

-

集成电路

+关注

关注

5464文章

12688浏览量

375744 -

封装

+关注

关注

128文章

9333浏览量

149052 -

焊锡

+关注

关注

0文章

330浏览量

20028

发布评论请先 登录

硅片划片机破解硬脆材料崩边难题,助力半导体器件封装降本增效

半导体“封装过程”工艺技术的详解;

奥芯明:AI驱动半导体产业迎来“异构集成”新纪元,先进封装成破局关键

现代集成电路半导体器件

【展会预告】2025 中国西部半导体展重磅来袭,华秋邀您 7 月 25-27 日西安共探集成电路新未来!

半导体集成电路封装成型技术及去飞边毛刺、上焊锡流程介绍!

半导体集成电路封装成型技术及去飞边毛刺、上焊锡流程介绍!

评论