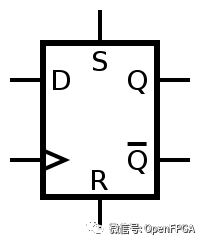

D 触发器

D 触发器符号D触发器被广泛使用。它也被称为“data”或“delay”触发器。

D 触发器在时钟周期的特定部分(例如时钟的上升沿)捕获 D 输入的值。捕获的值成为 Q 输出。在其他时候,输出 Q 不会改变。D触发器可以看作是一个存储单元、一个零阶保持器或一条延迟线。

D 触发器真值表

(X表示无关条件,表示信号无关)

IC 中的大多数 D 型触发器都具有强制 set 或者 reset状态(忽略 D 和时钟输入)的能力,就像 SR 触发器一样。通常,非法 S = R = 1 条件在 D 型触发器中得到解决。设置 S = R = 0 使触发器的行为如上所述。以下是其他可能的 S 和 R 配置的真值表:

4 位串行输入并行输出 (SIPO) 移位寄存器这些触发器非常有用,因为它们构成了移位寄存器的基础,而移位寄存器是许多电子设备的重要组成部分。D触发器相对于D型“透明锁存器”的优势在于D输入引脚上的信号在触发器被计时的那一刻被捕获,并且D输入上的后续变化将被忽略,直到下一个时钟事件。一个例外是一些触发器有一个“复位”信号输入,它会将 Q 复位(为零),并且可能与时钟异步或同步。

上述电路将寄存器的内容向右移动,在时钟的每个有效转换上移动一位。输入 X 被移到最左边的位位置。

经典的正边沿触发 D 触发器

几种不同类型的边沿触发 D 触发器

一个上升沿触发的 D 触发器

一个上升沿触发的 D 触发器## 主从边沿触发 D 触发器

主从 D 触发器。它在使能输入的下降沿响应(通常是时钟)

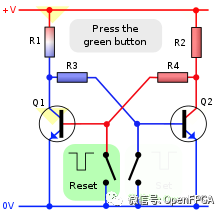

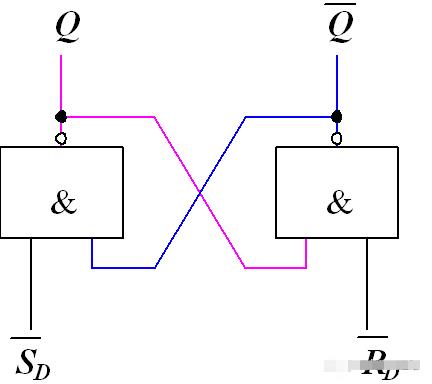

在时钟上升沿触发的主从 D 触发器的实现通过串联两个门控 D 锁存器并将使能输入反相到其中一个来创建主从 D 触发器。之所以称为主从锁存器,是因为主锁存器控制从锁存器的输出值 Q 并在从锁存器启用时强制从锁存器保持其值,因为从锁存器总是从主锁存器复制其新值并更改其值仅响应主锁存器和时钟信号值的变化。

对于上升沿触发的主从 D 触发器,当时钟信号为低电平(逻辑 0)时,第一个或“主”D 锁存器(反相时钟信号)看到的“使能”为高电平(逻辑 1) . 这允许“主”锁存器在时钟信号从低电平转换为高电平时存储输入值。随着时钟信号变高(0 到 1),第一个锁存器的反相“启用”变低(1 到 0),并且在主锁存器的输入处看到的值被“锁定”。几乎同时,第二个或“从”D 锁存器的两次反相“启用”随着时钟信号从低电平变为高电平(0 到 1)。这允许现在“锁定”的主锁存器在时钟上升沿捕获的信号通过“从属”锁存器。

移除电路中最左边的反相器会创建一个 D 型触发器,该触发器在时钟信号的下降沿触发。这有一个像这样的真值表:

双沿触发 D 触发器

双边沿触发 D 触发器的实现在时钟的上升沿和下降沿读入新值的触发器称为双边沿触发触发器。如图所示,可以使用两个单边触发 D 型触发器和一个多路复用器来构建这种触发器。

双边沿触发 D 触发器的电路符号## 边沿触发的动态 D 存储元件

具有复位功能的动态边沿触发触发器的 CMOS IC 实现只要时钟足够频繁,就可以使用动态电路(其中信息存储在电容中)来制作 D 触发器的有效功能替代方案;虽然不是真正的触发器,但由于其功能作用,它仍然被称为触发器。虽然主从 D 元件在时钟边沿触发,但其组件均由时钟电平触发。所谓的“边沿触发 D 触发器”,尽管它不是真正的触发器,但它不具有主从属性。

边沿触发的 D 触发器通常在使用动态逻辑的集成高速操作中实现。这意味着数字输出存储在寄生器件电容上,而器件不转换。这种动态触发器的设计还可以实现简单的复位,因为复位操作可以通过简单地对一个或多个内部节点进行放电来执行。一种常见的动态触发器种类是真正的单相时钟 (TSPC) 类型,它以低功率和高速执行触发器操作。然而,动态触发器通常不会在静态或低时钟速度下工作:如果有足够的时间,泄漏路径可能会使寄生电容放电到足以导致触发器进入无效状态的程度。

T 触发器

T型触发器的电路符号如果 T 输入为高电平,则只要时钟输入被选通,T 触发器就会改变状态(“toggles”) 。如果 T 输入为低电平,则触发器保持先前的值。这种行为由特征方程描述:

并且可以用真值表来描述:

T触发器真值表

当 T 保持高电平时,触发触发器将时钟频率除以 2;也就是说,如果时钟频率为 4 MHz,则从触发器获得的输出频率将为 2 MHz。这种“除法”功能适用于各种类型的数字计数器。AT 触发器也可以使用 JK 触发器(J 和 K 引脚连接在一起并充当 T)或 D 触发器(T 输入 XOR Q驱动 D 输入)构建。

JK 触发器

正沿触发 JK 触发器的电路符号

JK触发器时序图JK 触发器通过将 J = K = 1 条件解释为“翻转”或切换命令来增强 SR 触发器的行为(J: Set, K: Reset)。具体来说,J=1,K=0的组合是设置触发器的命令;J = 0,K = 1的组合是复位触发器的命令;J = K = 1 的组合是触发触发器的命令,即将其输出更改为其当前值的逻辑补码。设置 J = K = 0 保持当前状态。要合成 D 触发器,只需设置 K 等于 J 的补码(输入 J 将充当输入 D)。类似地,要合成一个 T 触发器,设置 K 等于 J。因此 JK 触发器是通用触发器,因为它可以配置为 SR 触发器、D 触发器或T触发器。

JK触发器的特征方程为:

对应的真值表为:

JK触发器真值表

时序

时序参数

触发器设置、保持和时钟到输出时序参数输入必须在时钟上升沿附近的一段时间内保持稳定,称为孔径。想象一下在睡莲上拍一张青蛙的照片。假设青蛙之后跳入水中。如果你拍青蛙跳入水中的照片,你会看到青蛙跳入水中的模糊照片——不清楚青蛙处于哪种状态。但如果你在青蛙稳稳地坐着的时候拍照在垫子上(或稳定地在水中),您将获得清晰的图像。同样,触发器的输入必须在触发器的孔径期间保持稳定。

建立时间是在时钟事件之前数据输入应保持稳定的最短时间,以便时钟可靠地采样数据。

保持时间是时钟事件后数据输入应保持稳定的最短时间,以便时钟可靠地采样数据。

孔径是建立时间和保持时间的总和。在此期间,数据输入应保持稳定。

恢复时间是在时钟事件之前异步置位或复位输入应处于非活动状态的最短时间,以便时钟可靠地采样数据。因此,异步置位或复位输入的恢复时间类似于数据输入的建立时间。

移除时间是在时钟事件之后异步置位或复位输入应处于非活动状态的最短时间,以便时钟可靠地采样数据。因此,异步置位或复位输入的移除时间类似于数据输入的保持时间。

应用于异步输入(设置、复位)的短脉冲不应在恢复移除期间完全应用,否则将完全无法确定触发器是否将转换到适当的状态。在另一种情况下,异步信号只是在恢复/移除时间之间进行一次转换,最终触发器将转换到适当的状态,但输出上可能会或可能不会出现非常短的毛刺,具体取决于在同步输入信号上。第二种情况可能对电路设计有重要意义,也可能没有意义。

设置和复位(和其他)信号可以是同步的或异步的,因此可以用建立/保持或恢复/移除时间来表征,并且同步性非常依赖于触发器的设计。

在验证较大电路的时序时,通常需要区分建立/保持时间和恢复/移除时间,因为可能会发现异步信号不如同步信号重要。这种差异化使电路设计人员能够独立定义这些类型的信号的验证条件。

亚稳态

触发器存在称为亚稳态的问题,当两个输入(例如数据和时钟或时钟和复位)几乎同时发生变化时,就会发生这种情况。当顺序不明确时,在适当的时序限制内,结果是输出可能会出现不可预测的行为,需要比正常时间长很多倍的时间才能稳定到一种状态或另一种状态,甚至在稳定之前振荡几次。理论上,安定下来的时间是没有限制的。在电脑里系统,如果在另一个电路使用它的值之前状态不稳定,这种亚稳态会导致数据损坏或程序崩溃;特别是,如果两条不同的逻辑路径使用触发器的输出,当它尚未解析为稳定状态时,一条路径可以将其解释为 0,而另一条路径可以将其解释为 1,从而使机器进入不一致的状态。

通过确保数据和控制输入在时钟脉冲之前和之后的指定时段(分别称为建立时间(t su ) 和保持时间(th h ))保持有效和恒定,可以避免触发器中的亚稳态。这些时间在设备的数据表中指定,现代设备通常在几纳秒到几百皮秒之间。根据触发器的内部组织,可以构建具有零(甚至负)设置或保持时间要求但不能同时具有两者的设备。

不幸的是,并不总是能够满足建立和保持标准,因为触发器可能连接到一个实时信号,该信号可能随时变化,不受设计人员的控制。在这种情况下,设计人员能做的最好的事情就是根据电路所需的可靠性将出错的概率降低到一定水平。抑制亚稳态的一种技术是将两个或多个触发器连接成一个链,以便每个触发器的输出馈入下一个触发器的数据输入,并且所有设备共享一个公共时钟。使用这种方法,亚稳态事件的概率可以降低到可以忽略不计的值,但绝不会为零。随着串联触发器数量的增加,亚稳态的概率越来越接近于零。级联的触发器数量称为“ranking”;“dual-ranked”触发器(两个触发器串联)是一种常见的情况。

所谓的metastable-hardened触发器是可用的,它通过尽可能减少建立和保持时间来工作,但即使这些也不能完全消除问题。这是因为亚稳态不仅仅是电路设计的问题。当时钟和数据中的转换在时间上接近时,触发器被迫决定哪个事件首先发生。无论设备制造得有多快,输入事件总是有可能靠得太近,以至于无法检测到哪个事件先发生。因此,从逻辑上讲,构建一个完美的亚稳态触发器是不可能的。触发器有时以最大稳定时间为特征(它们在指定条件下保持亚稳态的最长时间)。

传播延迟

触发器的另一个重要时序值是时钟到输出延迟(数据手册中的常用符号:t_CO)或传播延迟(t_P ),即触发器在时钟边沿。从高到低的转换时间(t_PHL)有时与从低到高的转换时间(t_PLH)不同。

当级联共享相同时钟的触发器时(如在移位寄存器中),重要的是要确保前一个触发器的 t_CO长于后一个触发器的保持时间 (t_h ),因此,出现在后续触发器输入端的数据会在时钟的有效沿之后正确“移入”。如果触发器物理上相同,则通常可以保证t_CO和 t_h之间的这种关系。此外,为了正确操作,很容易验证时钟周期必须大于总和 t_su + t_h。

总结

触发器至少可以通过两种方式进行概括:使它们成为 1-of-N 而不是 1-of-2,以及使它们适应具有两个以上状态的逻辑。在 1-of-3 编码或多值三进制逻辑的特殊情况下,这种元件可以称为触发器。

在传统的触发器中,恰好两个互补输出中的一个为高电平。这可以推广到具有 N 个输出的存储元件,其中恰好一个为高(或者,恰好其中一个为低)。因此,输出始终是one-hot(分别是 one-cold)表示。结构类似于传统的交叉耦合触发器;每个输出,当高,抑制所有其他输出。或者,可以使用或多或少的传统触发器,每个输出一个,并带有额外的电路,以确保一次只有一个是真实的。

传统触发器的另一种概括是用于多值逻辑的存储元件。在这种情况下,存储元件恰好保留其中一种逻辑状态,直到控制输入引起变化。此外,还可以使用多值时钟,从而产生新的可能的时钟转换。

-

存储

+关注

关注

13文章

4889浏览量

90289 -

脉冲

+关注

关注

20文章

911浏览量

100061 -

锁存器

+关注

关注

8文章

958浏览量

45475 -

触发器

+关注

关注

14文章

2065浏览量

63559

发布评论请先 登录

恒压变压器的发展史

5G的发展史

CAN-bus 发展史

unix系统发展史

触发器发展史及类型(上)

触发器发展史及类型(下)

触发器发展史及类型(下)

评论