本文详细介绍Cortex-M3中断优先级相关知识。

1、什么是异常和中断

凡是打断程序顺序执行的事件都称为异常(exception),比如HardFault,外部中断等。所以中断也可以说是异常的一种。其实这也很好理解,因为程序执行不外乎正常和异常而已,所以打扰程序正常运行流程的事件都可以叫异常。

2、Cortex-M3异常类型

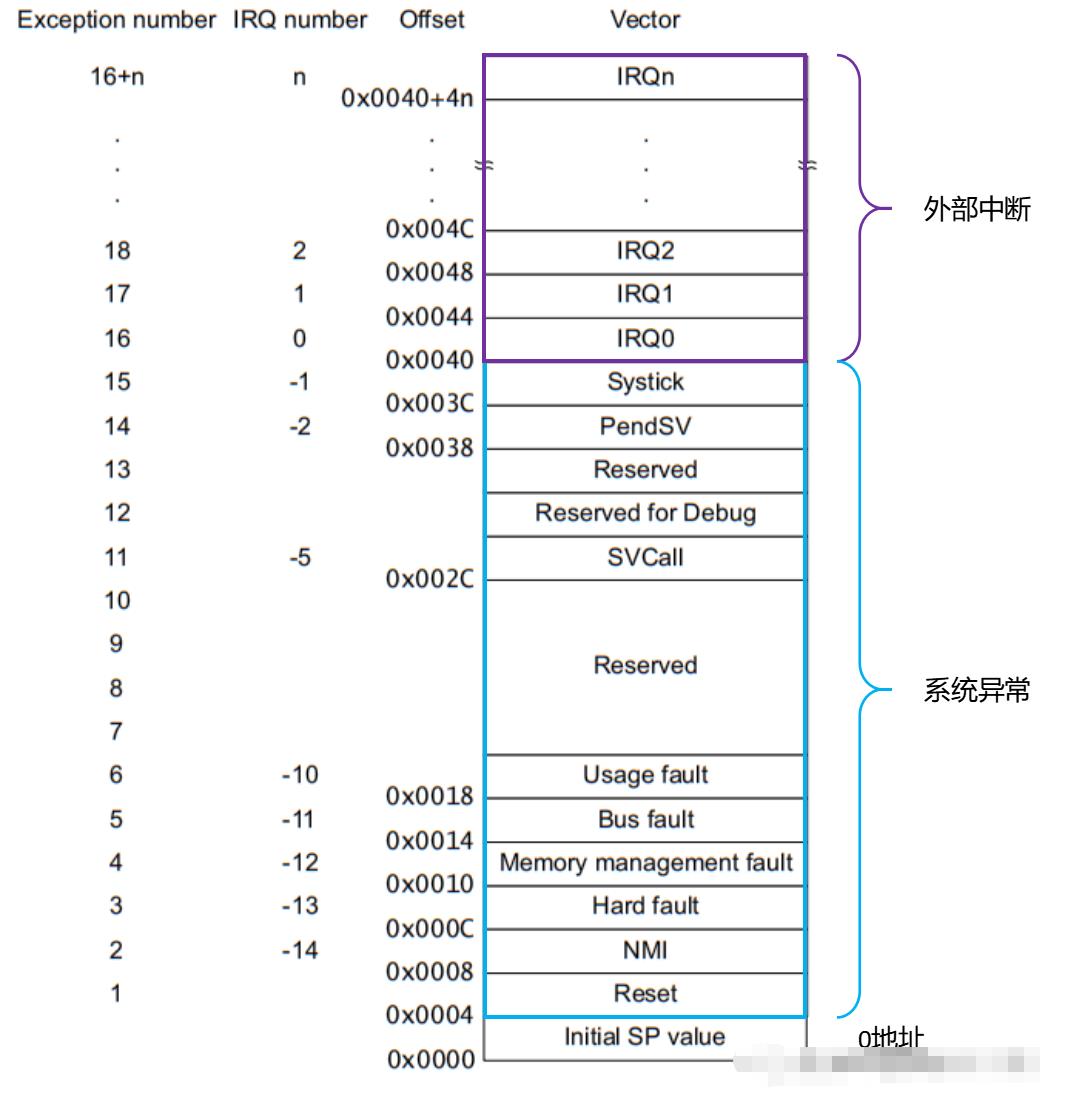

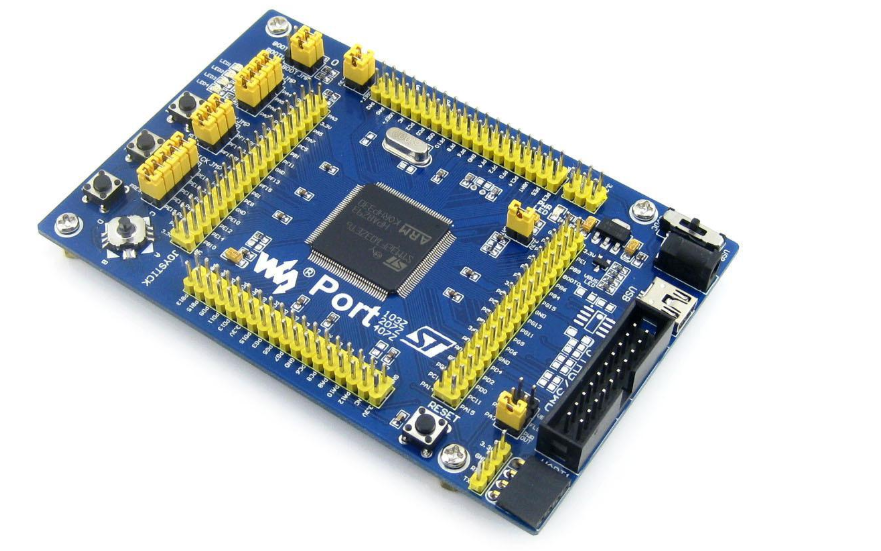

包括系统异常(异常编号1-15)和外部中断(异常编号16往上),系统异常在Cortex-M3内核中,由ARM设计,芯片厂商都会实现,外部中断最多可以有240个,由芯片生产厂家决定数量种类,比如UART,DMA等中断。Reset(-3)、NMI(-2)、HardFault(-1)这三个异常优先级都是负数且固定不变,优先级高于其他异常,除了这三个异常之外其他异常优先级都是可以编程的。

3、什么是中断抢占

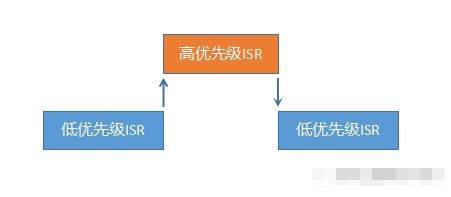

在执行低中断优先级中断函数时,高优先级中断到来,低优先级中断被打断,执行高优先级中断,高优先级中断执行完后回到低优先级中断继续执行。高优先级中断抢占了低优先级中断。如下图所示:

4、什么是抢占优先级和子优先级

每个中断优先级都包含两个部分,一部分称作抢占优先级,另一部分称作子优先级。以下来详细说明以下两个优先级的含义。

1)抢占优先级不同

具有高抢占优先级的中断能够抢占低抢占优先级的中断,也就是上面提到的中断嵌套。

2)抢占优先级相同,子优先级不同

当两个中断的抢占优先级设置为相同级别时,这两个中断不会出现中断嵌套。如果其中一个中断正在执行时,另外一个中断到来,后来的中断将会等到前一个中断执行完才能执行。如果这两个中断都处在等待响应状态,执行条件到来时,首先响应子优先级高的中断。

3)抢占优先级相同,子优先级也相同

这种情况也不会出现中断嵌套,内核将会按照向量表中的排位选择,优先执行靠前的异常。比如Pend SV和Systick两个中断优先级都设置为相同,如果两个中断同时到来,优先执行PendSV,因为它的排序靠前,见上面向量表。

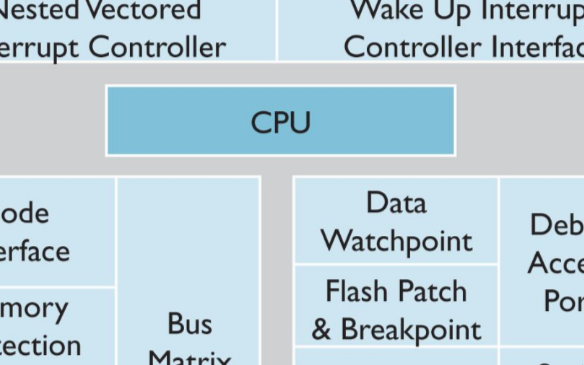

5、什么是优先级分组

在Cortex-M3内核中最多使用8Bit来表示中断优先级,在这8Bit中一部分用来表示抢占优先级,一部分用来表示子优先级,这两种优先级到底各占用几位,是由内核寄存器AIRCR(应用程序中断及复位控制寄存器)决定的,这个寄存的Bit8-Bit10代表了优先级分组,共3位,设置这三3位,可以改变优先级分组,如下几种组合:

000 高7位抢占优先级,低1位子优先级

001 高6位抢占优先级,低2位子优先级

010 高5位抢占优先级,低3位子优先级

011 高4位抢占优先级,低4位子优先级

100 高3位抢占优先级,低5位子优先级

101 高2位抢占优先级,低6位子优先级

110 高1位抢占优先级,低7位子优先级

111 高0位抢占优先级,低8位子优先级

另,Cortex-M3内核要求最多使用8Bit来表示中断优先级,但是很多芯片厂商为了简化设计都会进行裁剪,比如STM32只用4位表示优先级。

-

ARM

+关注

关注

135文章

9588浏览量

393579 -

内核

+关注

关注

4文章

1475浏览量

43089 -

中断

+关注

关注

5文章

920浏览量

43868 -

Cortex-M3

+关注

关注

9文章

276浏览量

61807 -

优先级

+关注

关注

0文章

21浏览量

9129

发布评论请先 登录

Cortex-M3处理器中断与FreeRTOS中断优先级配置

STM32中断优先级的相关概念与使用笔记资料免费下载

STM32中断优先级的相关概念与使用笔记详细资料概述

STM32中断优先级相关概念与使用笔记资料免费下载

关于Cortex-M3的中断优先级描述资料下载

2.FreeRTOS中断优先级和任务优先级

Cortex-M3中断优先级的相关知识

Cortex-M3中断优先级的相关知识

评论