欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:基于FPGA的千兆以太网ARP和UDP的实现

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639106

原文标题:基于FPGA的千兆以太网ARP和UDP的实现

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

探索TS3L500AE:千兆以太网开关的卓越之选

探索TS3L500AE:千兆以太网开关的卓越之选 在电子工程师的日常工作中,一款性能卓越的以太网开关器件往往能为设计带来事半功倍的效果。今天,我们就来深入剖析德州仪器(TI)推出的TS3L500AE

TNETE2201B 1.25 - 千兆以太网收发器:性能与应用解析

TNETE2201B 1.25 - 千兆以太网收发器:性能与应用解析 在高速数据传输的领域中,以太网收发器扮演着至关重要的角色。今天我们要深入探讨的是德州仪器(Texas Instruments

深度剖析TLK1211RCP千兆以太网收发器:设计应用指南

深度剖析TLK1211RCP千兆以太网收发器:设计应用指南 在现代高速数据传输领域,以太网收发器扮演着至关重要的角色。今天我们要深入探讨的是德州仪器(Texas Instruments

深入剖析TLK1221千兆以太网收发器:特性、功能与设计要点

深入剖析TLK1221千兆以太网收发器:特性、功能与设计要点 在高速数据传输的今天,以太网收发器扮演着至关重要的角色。TI公司的TLK1221千兆以

SM91604L LAN变压器:助力千兆以太网设计

SM91604L LAN变压器:助力千兆以太网设计 在电子工程师的日常工作中,LAN变压器是网络设备设计里的关键组件。今天,我们就来深入探讨一下BOURNS的SM91604L LAN变压器,看看它有

以太网通讯在FPGA上的实现

一、介绍在本项目由于我们需要使用PC实时的向FPGA发送将要识别的图片,所以我们最终选择使用以太网来从PC向FPGA发送图片并暂存在DDR中,下面是对以太网协议和硬件

发表于 10-30 07:45

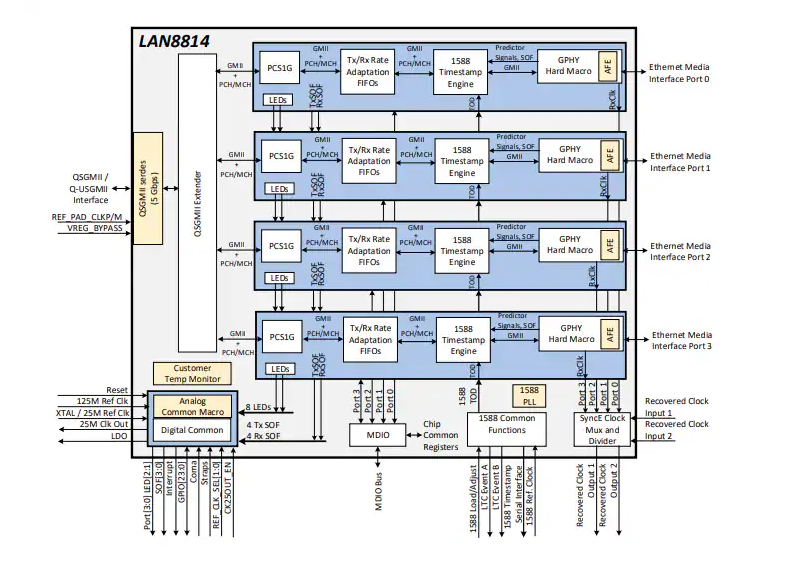

LAN8814 4端口千兆以太网收发器数据手册总结

Microchip Technology LAN8814 4端口千兆位以太网收发器是低功耗、四端口、三速(10BASE-T/100BASE-TX/1000BASE-T)以太网物理层收发器(PHY

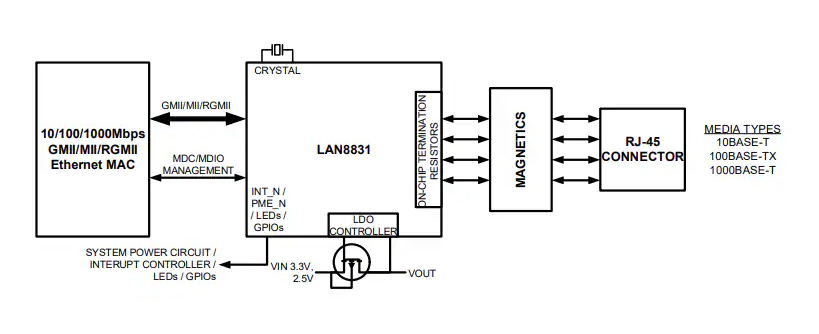

LAN8831千兆以太网收发器技术解析与应用指南

Microchip Technology LAN8831千兆位以太网收发器(带GMII/MII/RGMII )是完全集成的三速 (10BASE-T/100BASE-TX/1000BASE-T

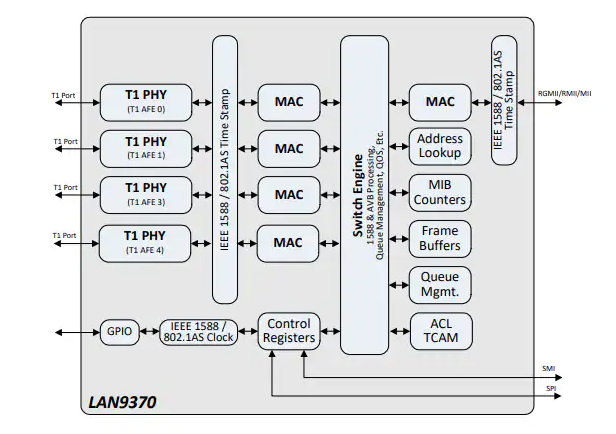

LAN9370汽车级以太网交换机芯片技术解析

Microchip Technology LAN937x千兆位以太网交换机是可扩展、紧凑型100BASE-T1以太网千兆位交换机,基于IEEE 802.3bw-2015规范。

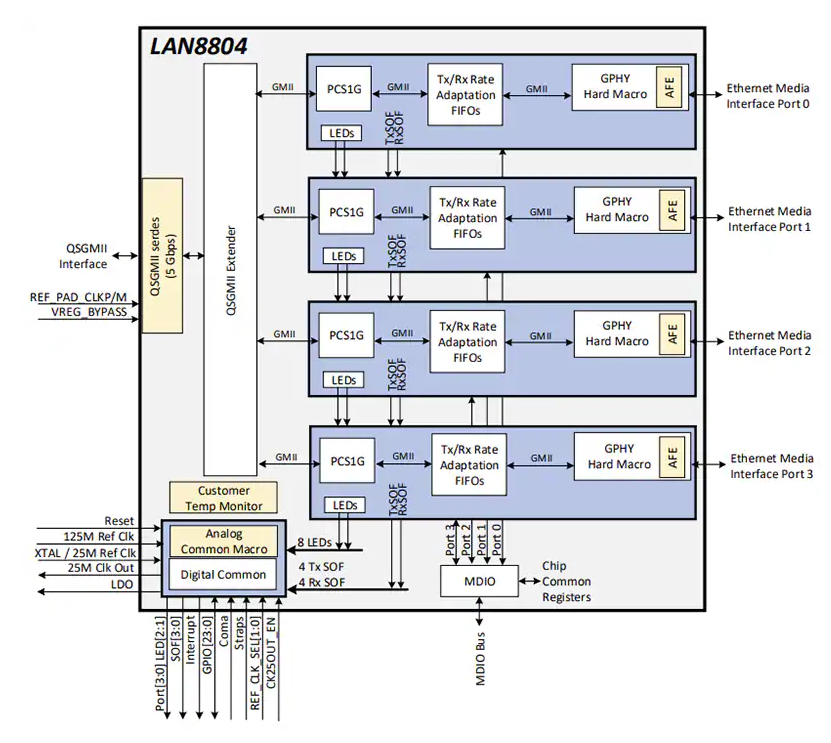

LAN8804四端口千兆以太网收发器技术解析

Microchip Technology LAN8804 4端口千兆位以太网收发器是低功耗、四端口、三速(10BASE-T/100BASE-TX/1000BASE-T)以太网物理层收发器(PHY

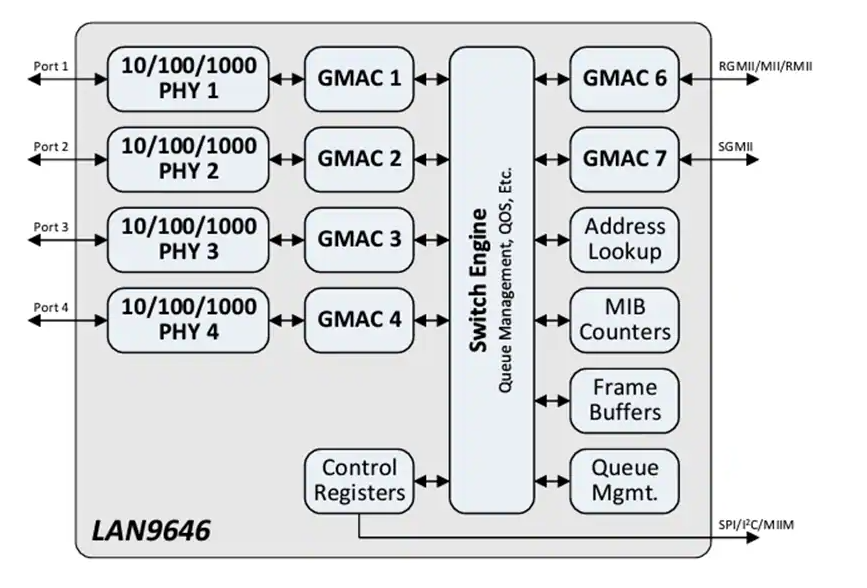

基于LAN9646六端口千兆以太网交换机的技术解析与应用

Microchip Technology LAN9646六端口千兆位以太网交换机是一款完全集成的托管第2层、六端口千兆位以太网交换机,具有高级特性。Microchip Technolo

移植网络PHY芯片驱动,如何融入 rt-thread 的网络体系,并添加新的以太网类型的报文?

PHY 芯片最底层收发以太网报文,有可能组成 VLAN 网络);

我要实现一个新的以太网类型报文(HPGP报文,以太网报文类型为 0x88E1),要求能在应用层收发该

发表于 09-22 06:11

【RK3568+PG2L50H开发板实验例程】FPGA部分 | 以太网传输实验例程

:

Window11 PDS2022.2-SP6.4

芯片型号:

PG2L50H-484

2.实验原理

2.1. 开发板以太网接口简介

开发板使用裕泰微的裕太微电子的 YT8521SH-CA 实现了一个 10

发表于 07-10 10:57

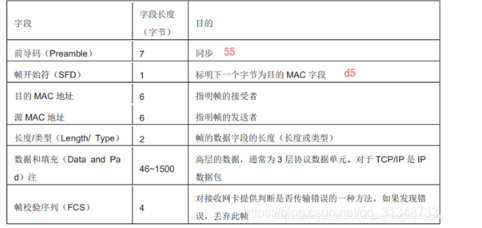

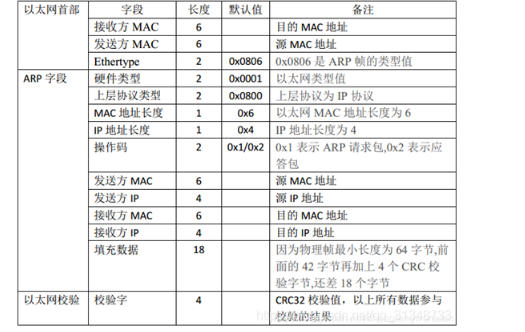

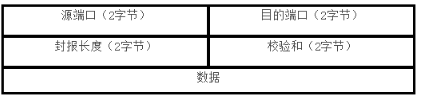

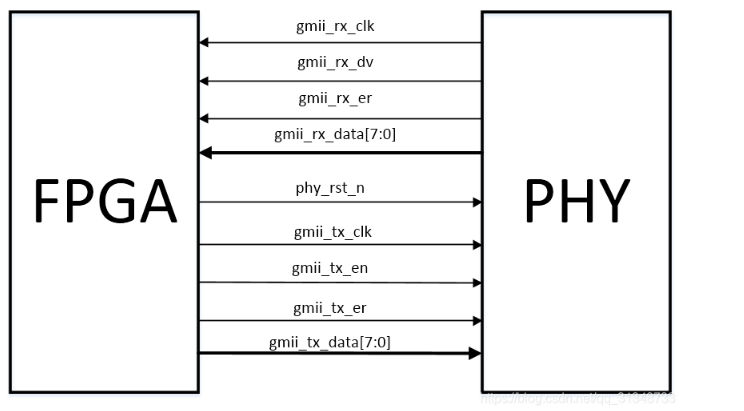

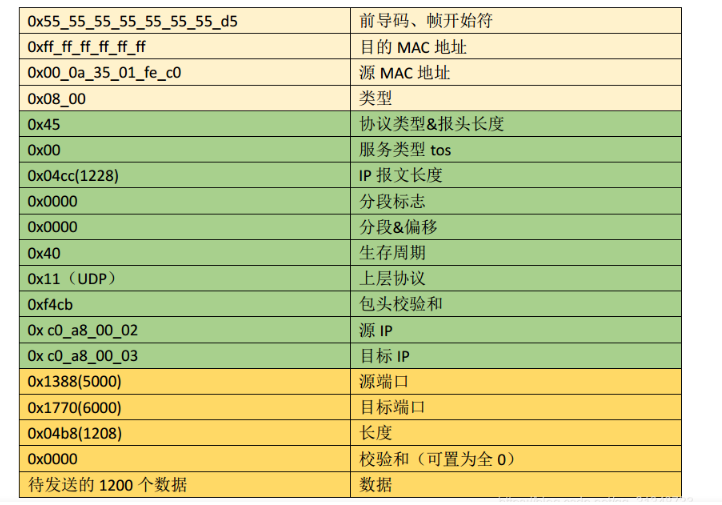

基于FPGA的千兆以太网ARP和UDP的实现

基于FPGA的千兆以太网ARP和UDP的实现

评论