最近在编写完FPGA逻辑,成功生成.bin文件后,发现将数据流文件烧写到Flash时间过长,突然想起可以通过Vivado软件进行设置,提高烧写速度。操作如下:

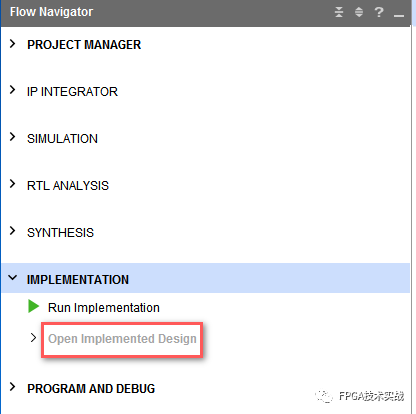

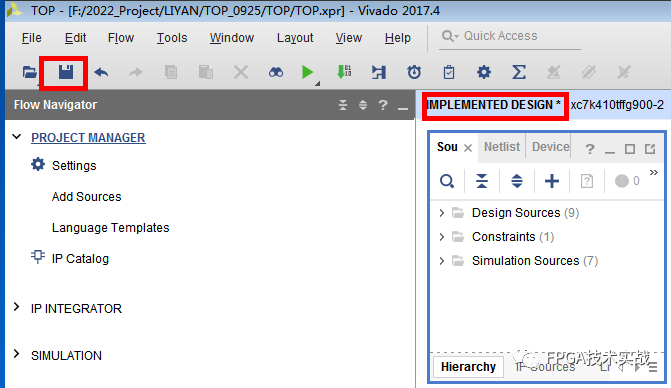

(1)布局布线完成后,点击Open Implementation。

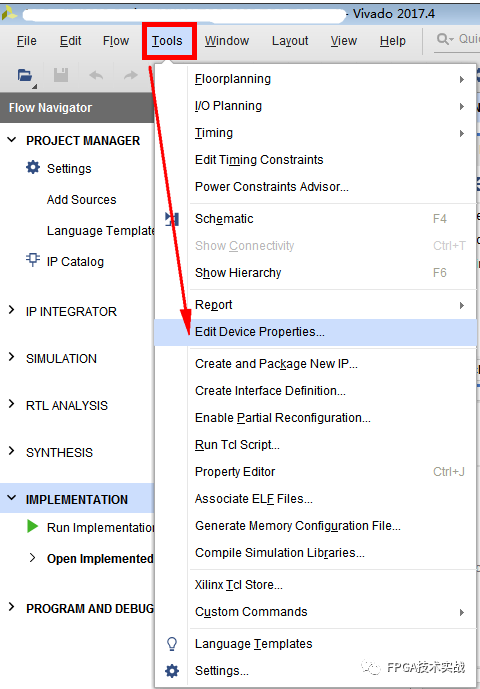

(2)点击Tool-----> Edit Device Properties...

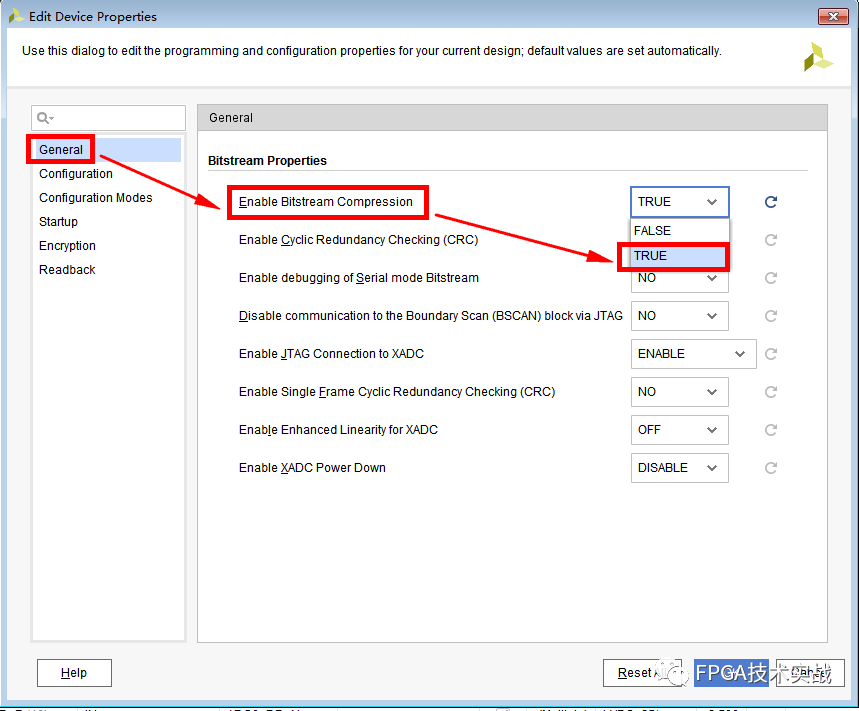

(3)General ----->Enable Bitstream Compression ----->TRUE,选择压缩数据流,提高下载速度。

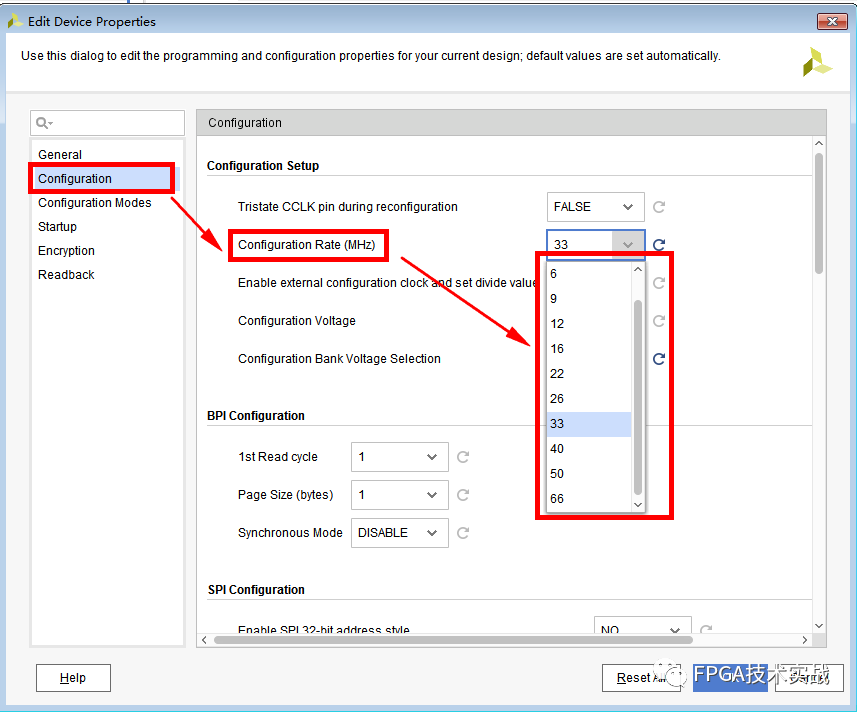

(4)Configuration -------> Configuration Rate(MHz),可以选择较大的CCLK时钟值。(如果配置I/O PCB布线不佳,较大的时钟可能会导致FLASH烧写失败,此时需要降低CCLK时钟)

点击OK,并点击“保存”菜单,保存当前配置。

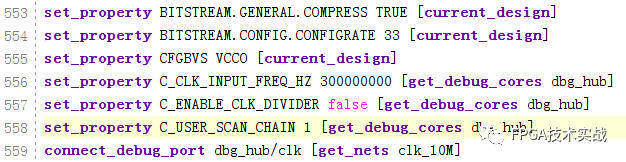

打开.xdc约束文件,我们可以看到新增以下内容:

完成以上操作,重新生成bit文件及bin文件即可实现加快FLASH烧写速度。

审核编辑:汤梓红

-

FPGA

+关注

关注

1655文章

22282浏览量

630112 -

FlaSh

+关注

关注

10文章

1715浏览量

154681 -

Xilinx

+关注

关注

73文章

2192浏览量

129894 -

文件

+关注

关注

1文章

587浏览量

25913 -

Vivado

+关注

关注

19文章

846浏览量

70458

原文标题:提高Xilinx FPGA Flash下载速度

文章出处:【微信号:FPGA技术实战,微信公众号:FPGA技术实战】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NANO2开发应用之 如何使用xilinx下载工具下载bit,固化FPGA

Xilinx FPGA无痛入门,海量教程免费下载

XILINX V7系列FPGA的的BPI FLASH程序下载问题咨询

Xilinx程序下载方式

Xilinx_FPGA下载烧写教程(超详细)

xilinx FPGA下载flash问题

Xilinx-Spartan6 FPGA实现MultiBoot

FPGA配置– 使用JTAG是如何烧写SPI/BPI Flash的?

提高Xilinx FPGA Flash下载速度

提高Xilinx FPGA Flash下载速度

评论