作为一个FPGA开发者,之前对于DDR的使用,一直仅限于对厂商接口的使用,像无论是Xilinx还是Intel,在使用DDR时甚至IP配置参数都不需要了解,直接从老的工程里把IP拷贝过来就可以,而在使用DDR时只需要会使用AXI4/AvalonMm标准总线接口就行了。混了这么多年,本着够用即可,再往下稍微了解些。

个人总结,浅入浅出。让我设计一个控制器那可是难为我了。

DDR——无非大的数组

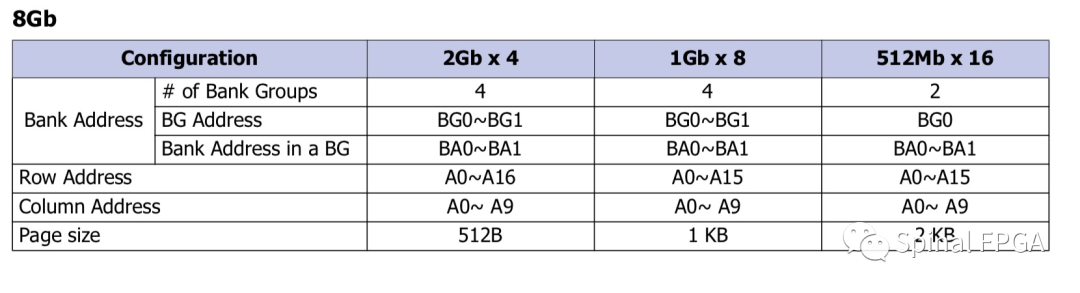

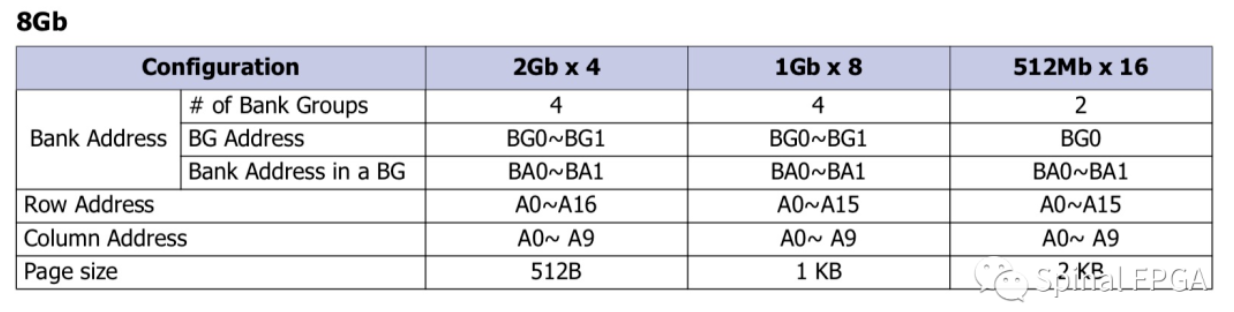

对于DDR的理解,最初简单的以为无非一个大的数组,我会接口使用就OK了。不管各种概念天花乱坠,其总归最终还是要归还到DDR颗粒芯片上来吧。我们常说DDR容量大小,某款DDR颗粒手册上写的规格容量如下图所示:

看完之后一开始我只看懂了这个DDR颗粒手册上写的DDR容量是8Gb,剩下的我就能看懂的不多了~这也是为什么决定花点儿功夫好好了解下DDR的基础知识。后面我们再来Review这张表。

这款芯片的512Mb x 16的引脚有这么几个:

BG:1bit(GB0)

BA:2bit(BA0~BA1)

ROW:16 bit(A0~A15)

Column:10 bit(A0~A9)

DQ: 16 bit(DQ0~DQ1)

看完之后简单总结一句话:对于DDR颗粒,Bank是读写地址动作的最小单元。像上面的512Mb x 16模式下,颗粒内部有两个Bank Group,每个Bank Group内部有四个Bank,而每个Bank内部的“存储矩阵(二维数组)”对应的行地址16 bit,列地址10 bit,每个存储单元存储16 bit数据。先不管对错,这么算起来的话:

2**(1+2+10+16)*16=2**(33)=8Gb

容量是对上了,然而这看起来和上面的表格里的有些东西却并对不上。

在上面的表格中,关于Configuration一行,512Mbx16意味着该DDR颗粒寻址能力为512Mb,每个地址对应16 bit。由于对于DDR4列地址的低三bit并不参与译码,故寻址范围大小的计算方式为:

2**(1(BG)+2(BA)+16(COL)+(10-3)COL)=2**26=512 Mb

如果你在Quartus进行配置的话,也会发现给使用者的接口AvalonMm总线地址位宽也恰好为26 bit。

Page Size

按照上面文章里面的解释,prefetch相当于在DRAM Core与外面的IO建立了8多条通道,而Burst Fetch Length则是对于DDR颗粒可以在指定行,列地址后可连续读取在该行指定列地址之后的多个列地址对应的内容。DDR4 prefetch和burst fetch length一般均为8,以上面的512Mbx16则意味着当发起一个读指令时,将会返回8x16=128 bit=16 Byte字节数据。

Page Size所定义的为一行ROW所对应的数据量大小,如前所属,参与寻址的列地址位宽为7,每个cell对应16 bits,对应burst fetch length为8,故Page Size的计算方式为:

2**7*16*8=2*14 bits=16 Kb=2 KB颗粒堆叠

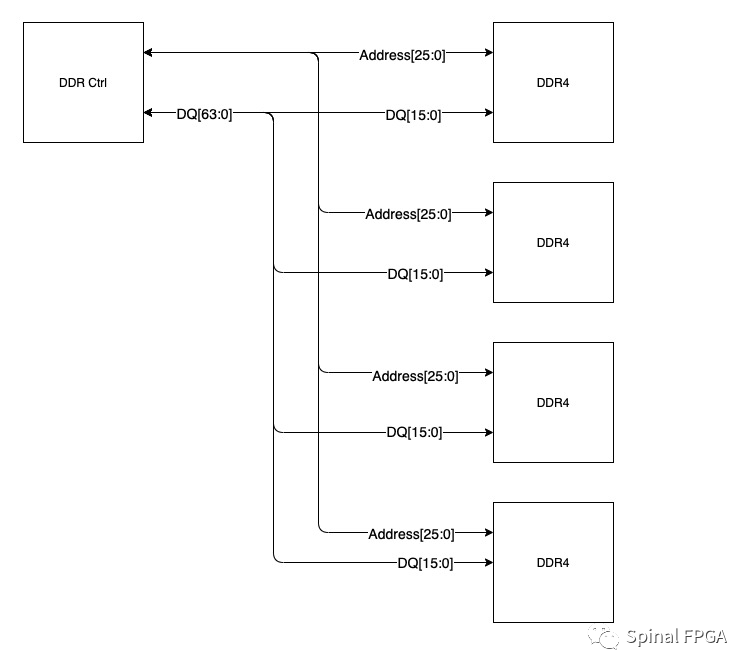

像上面的单个颗粒容量大小为8Gb。在FPGA使用里,DDR常见的配置有x64/x32这样的模式。

如果在板卡上使用DDR颗粒,以x64的形式来组织板卡DDR架构,那就是这样的结构。

x64模式下,用到4片DDR,4片DDR的地址总线共用,数据总线则分成四份连接到四路DDR上。故此当你在IP上发起64字节读写请求时每个DDR分别承担了16 Byte字节的读写,恰好为一次Burst Length。

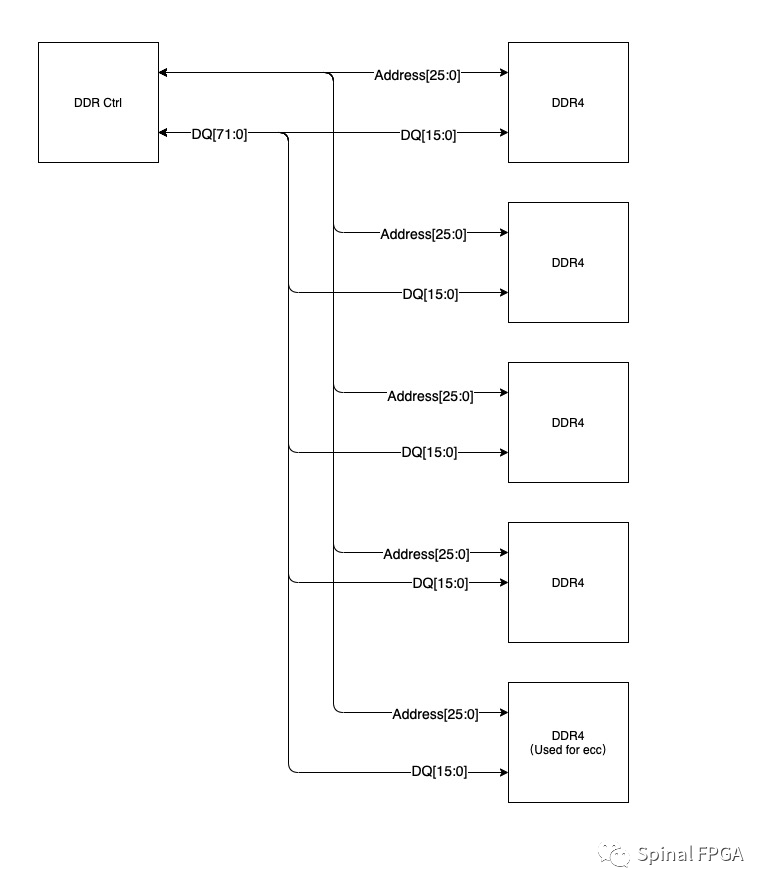

而当你如果要是能ECC时,则需要5片DDR:

此时第五个DDR 8bit专门用于存储ECC校验结果。在ECC模式下,x72bit模式下,若非64字节读取/写入,则需将数据先读取出来再更新写入,效率有一定的降低~

审核编辑:刘清

-

FPGA

+关注

关注

1664文章

22508浏览量

639450 -

控制器

+关注

关注

114文章

17886浏览量

195237 -

DDR

+关注

关注

11文章

762浏览量

69579 -

ECC

+关注

关注

0文章

104浏览量

21769

原文标题:FPGAer浅入浅出DDR——容量规格篇(一)

文章出处:【微信号:Spinal FPGA,微信公众号:Spinal FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

浅入浅出DDR的容量规格

浅入浅出DDR的容量规格

评论