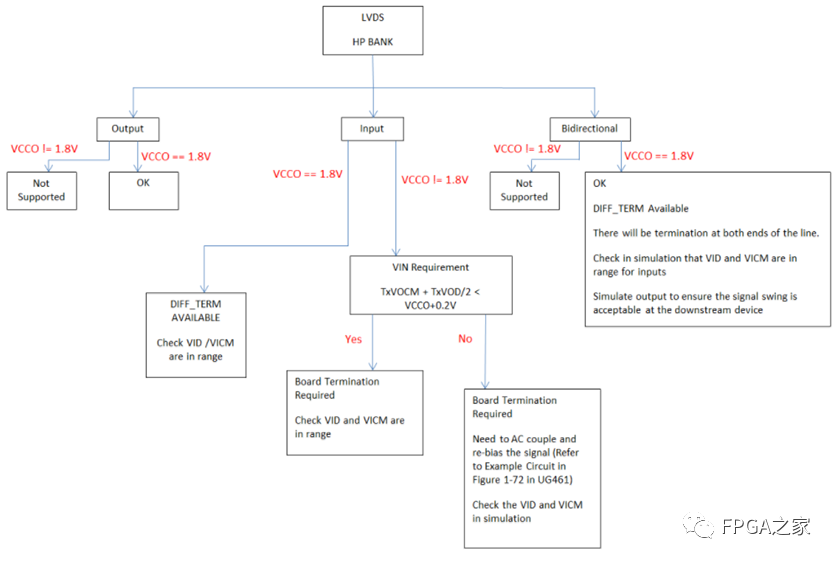

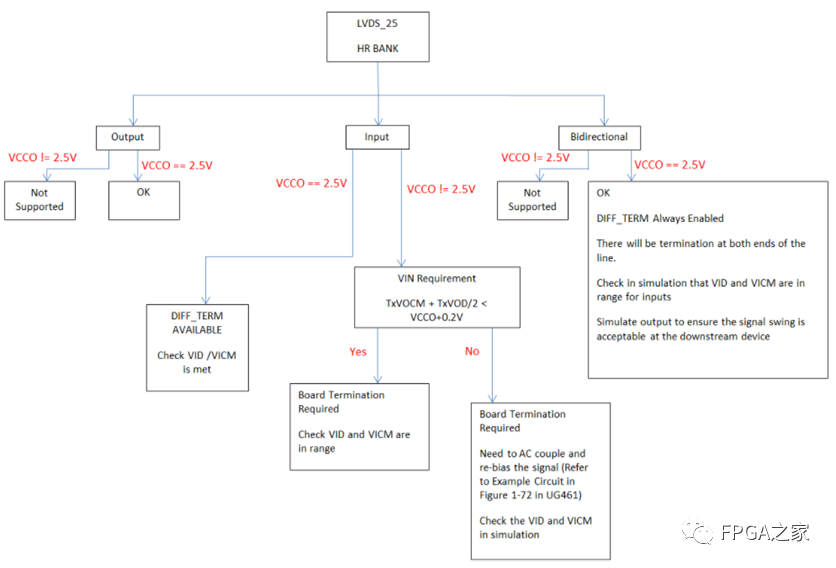

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及LVDS-33,LVDS-25)信号相连时兼容性的问题,该专题就解决一下这类问题。总的来说,只要按照下面图 1和图 2流程进行判断即可。

这里补充一点知识,Xilinx的FPGA从7系开始分HR IO Bank和HP IO Bank,其中HR(High Range)Bank支持1.2V,1.5V,1.8V,2.5V以及3.3V供电;而HP(High Performance)Bank只支持1.2V,1.5V,1.8V供电,不再支持2.5V和3.3V供电。

针对LVDS的兼容性,图 1和图 2已经可以解决绝大多数问题了,这里做一些补充和解释。

很明确的结论:作为输入引脚时,VCCO不等于1.8V的Bank有可能可以连接LVDS电平标准输入;VCCO不等于2.5V的Bank有可能可以连接LVDS_25电平标准输入。但是作为LVDS输出引脚时, 相应Bank的VCCO必须与电平标准的电压相匹配。

VCCO是IO Bank的Output Driver的驱动电源,Input Receiver中部分功能是由VCCAUX供电的。这就解释了为什么作为输入引脚时,电平标准可以与VCCO不匹配。当然Input Receiver也受到VCCO的影响,见第3条。

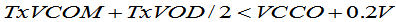

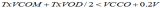

当LVDS作为输入引脚时,判断是否可以使用的第一条原则是,作为输入信号的绝对电平不能超过VCCO+0.2V这个绝对电压门限,否则有可能损坏引脚的Input Receiver。这是图 1和图 2中都做了

判断的根本原因。

判断的根本原因。

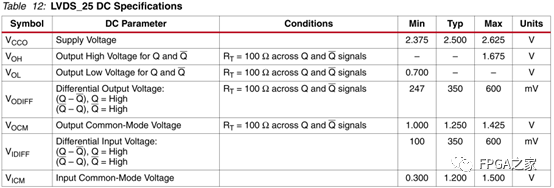

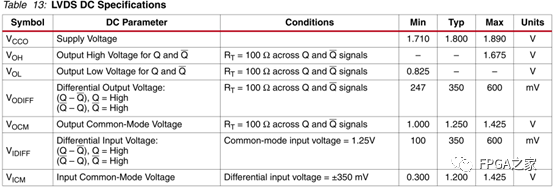

当LVDS作为输入引脚时,判断是否可以使用的第二条原则就是对比信号输入与Xilinx相关器件的LVDS的共模电压以及峰峰值的指标是否满足。例如Kintex系列的器件需要查阅DS182中的相关参数,如下图所示。

当LVDS作为输入引脚时,如果相应Bank的VCCO与对应的电平标准不匹配,即使可以使用,但DIFF_TERM功能一定不可使用。

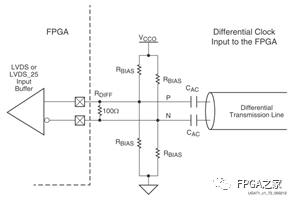

当LVDS作为输入引脚时,如果确实没有办法满足图 1和图 2的条件时,可以使用AC耦合的解决方案。其原理在于所谓的电平不匹配都是共模电压不匹配,如果使用如图 5所示的电路,其中AC耦合电容将DC电压阻断,也就是TX端的共模电压不会传到RX端,RX端只能接收到差分的输入信号,而RX端的共模电压通过RBIAS进行调节,以满足RX端接收到的绝对电压不会超过VCCO+0.2的要求。

Xilinx FPGA中的LVDS current-mode driver是真正的电流驱动器,不是电压模拟型的驱动器。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22503浏览量

639258 -

Xilinx

+关注

关注

73文章

2206浏览量

131900 -

信号

+关注

关注

12文章

2930浏览量

80408 -

lvds

+关注

关注

2文章

1242浏览量

70230 -

开发板

+关注

关注

26文章

6420浏览量

120887

原文标题:FPGA与LVDS信号兼容性分析方法

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

系统的电磁兼容性分析模型及设计方法

FPGA的封装兼容性意味着什么

电磁兼容性主要的几种整改方法

基于JavaScript浏览器兼容性测试方法

一文看懂电磁兼容性原理与方法及设计

FPGA与LVDS信号兼容性分析方法

FPGA与LVDS信号兼容性分析方法

评论