来源:《半导体芯科技》杂志 12/1月刊

作者:Raj Varma,Delphon公司技术总监

在生产环境中移动单个裸芯片(Die)可能会带来许多挑战。虽然有很多安全运输解决方案,但所有解决方案都是使用一次性卷带系统,或者采用针对每种芯片尺寸定制的载体 -也就是依据每个芯片外形尺寸为晶圆厂生产的不同载体。Delphon公司的Gel-Pak部门开发了一个新的解决方案,将改变制造商在HVM系统中运输和测试芯片的方式。

新兴的小芯片(chiplet)趋势要求将大型单片的功能分解为互连的小型芯片,这种替代片上系统(SoC)的小芯片技术相比来说具有明显的优势。向这项技术的转变更加需要已知良好的芯片(known good die,KGD),因为KGD芯片在集成到最终封装中之前已经经过全面测试。

目前行业在测试和组装过程中面临的一个挑战是,传统的运输处理芯片的方法可能不适于chiplet。因为chiplet的尺寸繁多,在组装过程需要拾取和重新拾取chiplet组件,或者在进程之间需要移动它们,因此需要一种更简化的方法来运输处理这些chiplet小芯片。

业内需要一种通用运输载体来替代带有定制设计托盘的包装袋或仅适合一次性使用的卷带。Gel-Pak以其著名的真空释放™(Vacuum Release™)托盘技术填补了这一空白,他们采用新开发的微纹理薄膜,可以实现轻松抓取裸片,无需使用包装袋。微纹理薄膜材料的灵感来自于自然界中壁虎、蜥蜴、甲虫、蜘蛛和蚂蚁的生物干粘附力。本文讨论了Gel-Pak为这种新型材料开发理想纹理、制造工艺和几何图案的过程,以及其作为集成电路(IC)载体的功效。

△图1:常用的芯片运输处理方式-切块薄膜、JEDEC托盘和卷带。

现代半导体行业主要面临着摩尔定律平台期的困难。通过晶体管几何形状减小以实现晶体管密度每两年翻一番的情况已经不再能持续。同时,单片芯片的物理尺寸正在增长,因为试图在一片硅片上装入更多的硬件块,这使得每单位面积封装更多处理能力的目标更加难以实现。

但是,单个芯片中可以集成的功能是有限的。Chiplet是一些互连的较小的芯片(chiplet)的2.5D和3D堆叠,而这些较小的chiplet具有明确定义的功能子集。与单片芯片相比,chiplet具有更高集成度,允许使用更多的硅来添加晶体管,而不会占用额外的空间。

组装chiplet时需要考虑一个主要因素:chiplet本身的完整性。一个“坏”的芯片会使2.5D或3D模块出现故障,导致良率低下。这种潜在的缺点加剧了对KGD的需求,因为在将芯片安装到更大的设计中之前,需要对每个单个芯片进行测试。采用“优质”芯片(KGD)使制造商能够轻松地将这些裸芯片集成到最终封装中,从而大大提高了这些模块的良率。

在最终集成整合之前,chiplet技术的测试和组装过程通常需要对这些组件进行存储和配套。组件通常在设施内被移动以进行芯片级测试或加工。不同的组件尺寸要求组件载体能够迅速适应外形尺寸的快速变化,但又仍保持JEDEC标准以适应现有的设备和拾取和放置(PnP)工具。

晶圆探针测试与SDT的比较

测试晶圆上单个芯片的传统方法是晶圆探针测试(WPT)方法,或称为晶圆级老化(WLBI)。在这种方法中,具有数千个探测针的专用晶圆探针台与裸片上的微凸块接触。但是,这不是一个完整而准确的测试,因为周围芯片的存在会降低测试准确性,并且不利于运行某些测试,例如大电流测试。虽然漏极和栅极泄漏测试(如IDSS和IGSS)可以在WPT上进行,但测量的泄漏值在分离后会发生变化。此外,侧壁裂缝等缺陷可能会带来额外的变化。单体裸芯片测试(singulated die testing,SDT)可以得到更准确的结果,由此产生的测试参数与封装部件保持一致。通过这些测试,可以更深入地评估裸片的可靠性。这使得供应商能够有效地绕过集成参数不匹配的“坏”芯片的潜在障碍,满足所需的chiplet性能要求。

在SDT期间运输处理裸片的挑战

单体裸芯片测试(SDT)是一项重大挑战,因为裸芯片可能很脆,容易受到颗粒污染、开裂和断裂的影响。理想情况下,裸片载体将允许制造商拾取和重新拾取芯片,接近其侧面,运输处理不同尺寸的芯片,并固定芯片(见表1)。

△表1

运输处理裸片的一些常见方法包括:

•华夫饼包装芯片托盘

•卷带

•胶带(切块胶带)

华夫饼包装芯片托盘通常是在一系列容纳半导体芯片的平行空腔或凹槽中运输裸片。凹槽和型腔体的宽度、长度和位置是针对特定IC尺寸量身定制的。但是,如果重新设计IC或供应商希望运送另一批芯片尺寸发生变化的IC时,则这种华夫饼包装托盘不能重复使用。这种托盘也不允许接触芯片的边缘。此外,这种托盘不太适合运输处理薄芯片。如果凹槽本身的平整度不够好,芯片在其中则始终有可能会翻转和迁移。

卷带包装面临类似的挑战;对于在新设计迭代中改变外形尺寸的IC来说,对定制凹槽和型腔尺寸的要求也要改变。由于凹槽和型腔用盖带密封,只能取下一次,因此卷带包装不适合SDT所需的重新拾取。

粘性胶带不需要像华夫饼包装和卷带包装那样定制凹槽和型腔以容纳特定IC。这些胶带还可以接触芯片的外侧面并固定芯片,以防止芯片迁移。但是,一旦芯片被拾取后,就不能被放回再重复使用,因而影响了其在SDT中的使用。

△图2:各种各样的动物群类的粘附系统图像。

(图片来源:[1])

自然界中的可逆粘附

Gel-Pak指出,业界需要一种通用芯片载体,该载体不需要定制凹槽或型腔来将IC固定到位,允许重新拾取,能够接触芯片边缘,并使芯片依靠自身固定。这种可逆粘附的灵感来自于自然界中发现的干粘附特性。某些蜥蜴、昆虫和青蛙爬上墙壁并轻松分离的能力是通过它们的脚趾垫的微纹理来实现的。脚趾垫由符合表面不规则性的原纤维微结构或者纳米结构组成;粘附力来自其外膜的粘弹性响应。如图2所示,每个物种的脚趾垫都具有其独特的质地纹理,其中每一个物种的微米和纳米级原纤维都足够长且灵活,可以到达它们附着的表面的微小凹谷中。换句话说,这些脚趾垫具有密集的微观接触点阵列,这些接触点表现出表面力和动力学反应,以产生牢固、可控和可靠的粘附接触。我们把这种脚趾垫组织材料的表面纹理和粘弹性响应的相互作用称为干粘附。

开发新型微纹理材料

在压敏粘合剂领域,已经有通过微纹理产生干粘附来实现牢固粘合的技术,并可以简单干净的释放(脱离粘合)。通过仔细研究其他成功粘合剂的发展情况,Gel-Pak在开发载体托盘技术时利用了相同的纹理粘合剂概念。在此过程中要观察的一个主要参数是拉脱力,即将粘合剂从表面上拉出所需的力。拉脱力必然是随着预载荷的变化而变化的,预载荷是拉脱前施加在粘合剂上的压缩力。研究表明,无论纤维尖端呈何种几何形状(例如,球形,扁平圆形,蘑菇形,刮刀形,凹形,方形,酒窝形)[2][3],拉脱力通常都随着预载荷增加而增加。

此外,较大的原纤维需要更大的预载荷力才能获得粘附力,因此需要更大的拉脱力才能将材料从表面脱离。换句话说,施加在粘弹性膜上的力越大,粘附力越强;原纤维越厚,附着和分离材料所需的力就越大。这可以有助于更好地了解PnP机器是否可以轻轻地从载体托盘中拿起裸片。

Gel-Pak专注于研究与大批量制造(HVM)兼容的纹理。在HVM中,使用传统的塑料制造工艺,例如注塑和挤出。通常在塑料制造工艺中,纹理化主要用于人体工程学考虑。而这种应用于芯片载体的纹理则需要粘性或粘合力控制。此外,纹理粘合剂的注塑成型在工业中并不普遍。在开发这种微纹理材料的过程中,Gel-Pak创新出一种注塑成型纹理粘合剂,可以应用于HVM。这在塑料制造业中尚无先例,应用本身也是独一无二的。因此,美国材料测试协会(ASTM)和其他测试标准都没有对纹理表面的粘性计量。为了使用最适合此类工艺的材料,Gel-Pak尝试了六种不同的纹理几何形状和二十多种不同的粘合剂配方。最终,选定交错凹坑尖端纹理用于这个工艺(图3)。

△图3:Gel-Pak新型通用载体使用了交错凹坑尖端几何形状的微纹理表面。

测试IC托盘技术

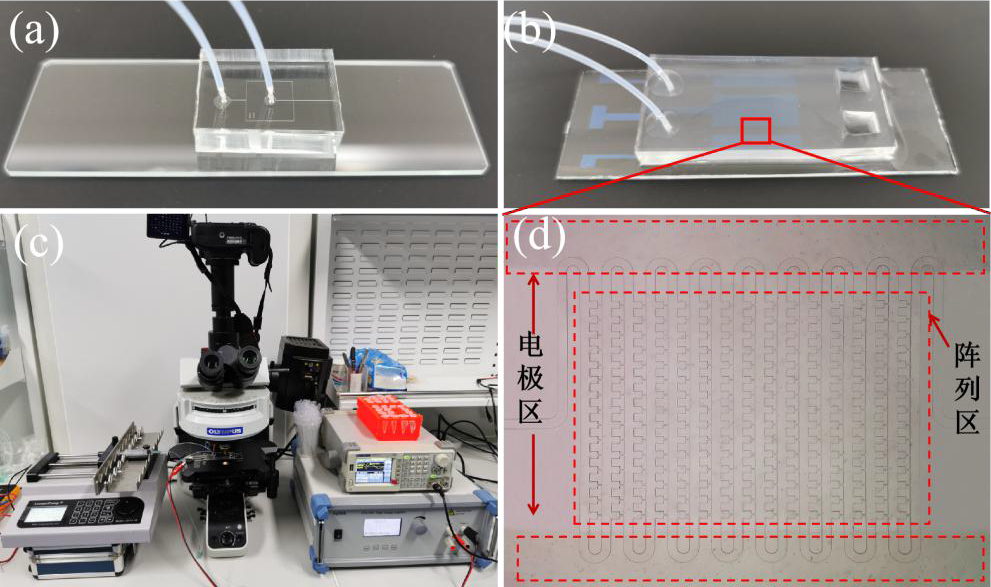

在选择纹理几何形状后,通过使用各种弹性体来生成各种预载荷力曲线(图4)。在这项研究计划中,微纹理的特征并不像之前发表的文献给出的那样小;然而,通过利用不同的粘合剂化学成分,可以覆盖一个很宽的预载荷力范围。研究原型是利用定制的扁平JEDEC托盘,将微纹理薄膜层压到表面(图5)。虽然JEDEC托盘本身是用于封装组件运输的,但使用JEDEC外形尺寸允许使用普通PnP机器进行测试,从而使其成为更实用的SDT解决方案。

△图4:六种不同弹性体化学品的预载荷与拉脱力关系。

根据以下几方面筛选所用的每种粘合剂:

•在-10℃、20℃和50℃下可承受

冲击/振动/跌落

•长期粘性增长

•集成电路背面残留物

•PnP和SMT可拾取性

经过测试,最终确定粘合剂的三

种不同粘性水平:

•低粘性

•中等粘性

•高粘性

低粘性材料对应于图4中的弹性体6。这种等级的附着力对于IC组件处理过程(例如测试)是理想的。中等粘性材料对应弹性体2、3和4,是传送处理和运输过程的首选。高粘性材料对应弹性体5,最合适更坚固的封装器件,例如无铅QFN封装。最后,我们在几种不同的PnP机器上测试了所研制的三种微纹理材料,包括Royce,Besi,Muhlbauer和MRSI,以及Juki的机器。只需对设备参数进行一些修改,所有机器都能够以中等速率成功地从修改后的托盘中拾取样品IC部件。这些修改允许足够的z轴下压力在IC部件表面形成一个密封真空杯,将真空拉到最佳阈值,然后启动拾取。

△图5:层压覆到扁平JEDEC托盘上的微纹理薄膜的照片,可以将不同尺寸的裸芯片粘附和固定。

结论

Gel-Pak的微纹理通用芯片载体是基于材料科学和制造技术的创新。我们探索了凸起几何形状和弹性体材料,以确保组件以最小的努力牢固地粘附在材料表面,并且可以通过PnP和SMT机器轻松移开。这种载体非常适合KGD的单体裸芯片测试过程。

扩展阅读

1. Eisenhaure JD, Kim S. A Review of the State of Dry Adhesives: Biomimetic Structures and the Alternative Designs They Inspire.Micromachines2017;8:125. doi:10.3390/mi8040125.

2. Campo A, Geiner C, Arzt E. Contact Shape Controls Adhesion of Bioinspired Fibrillar Surfaces. Langmuir 2007; 23:10235–10243.

3. He B, Chen W, Wang J. Surface Texture Effect on Friction of a Microtextured Poly(dimethylsiloxane) (PDMS). Tribol Lett 2008;31:187–197.

审核编辑黄宇

-

芯片

+关注

关注

463文章

54463浏览量

469547

发布评论请先 登录

集成电路制造中薄膜生长设备的类型和作用

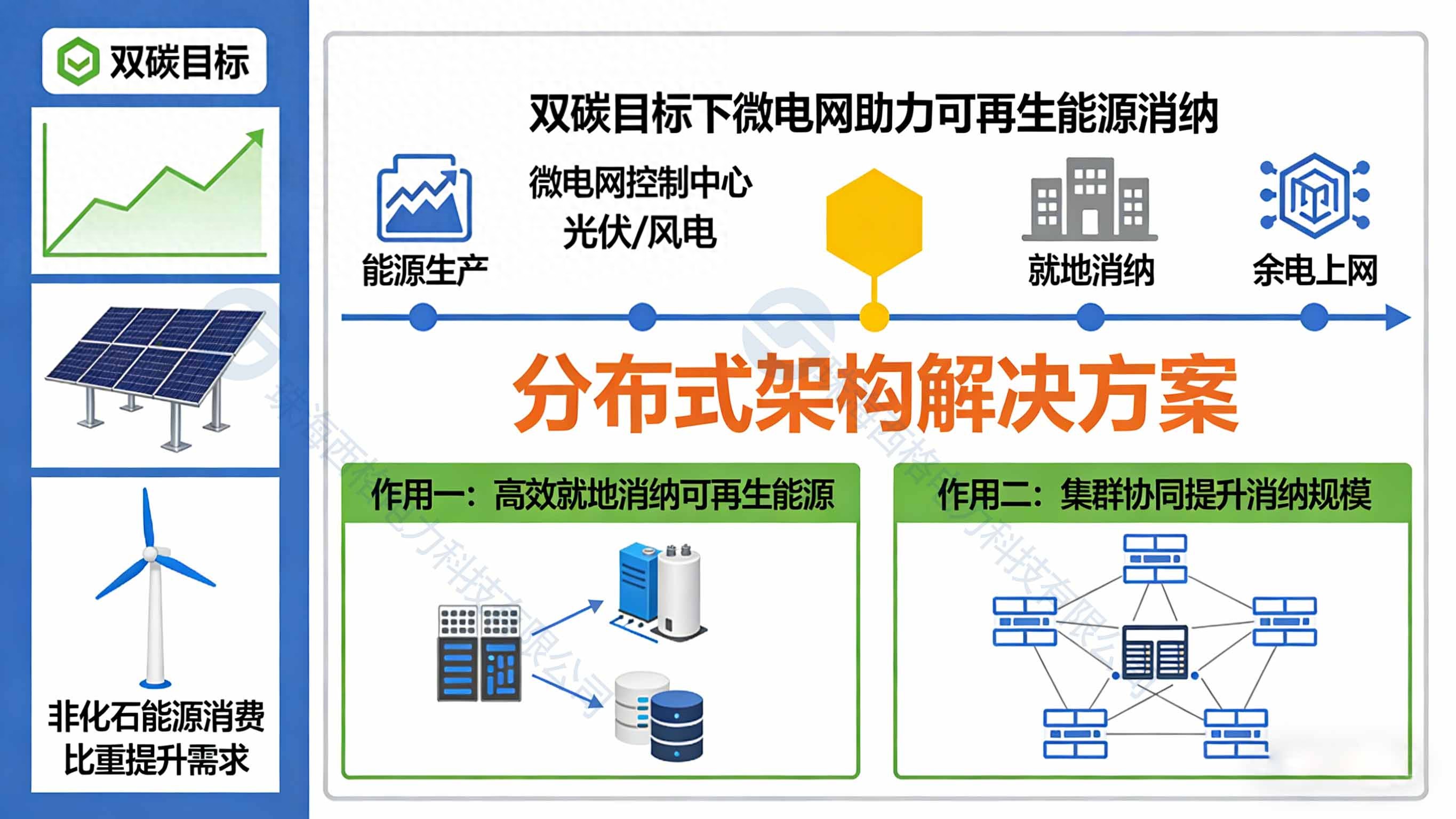

双碳目标下,微电网为何成为能源转型核心载体?

裸纤、专线、SDH、MSTP、MSTP+、OTN、PTN、IP-RAN 你了解吗?

富瀚微AI ISP 2.0,融合AI超分技术,实现“暗光如昼”

浅析昂瑞微的技术竞争力

动态环境下的挑战:移动载体上能否实现准确寻北?

浅谈智能微电网技术在零碳园区新型电力系统中的关键作用

基于悬空纳米薄膜硅基微盘谐振腔的CO₂传感器

在薄膜框架上提供的 PIN 二极管芯片 skyworksinc

Molex薄膜电池的技术原理是什么?-赫联电子

英伦科技10.1英寸裸眼3D数码相框升级了,玩转AI文生图太cool了!

新型微纹理薄膜实现通用裸芯片运输载体

新型微纹理薄膜实现通用裸芯片运输载体

评论