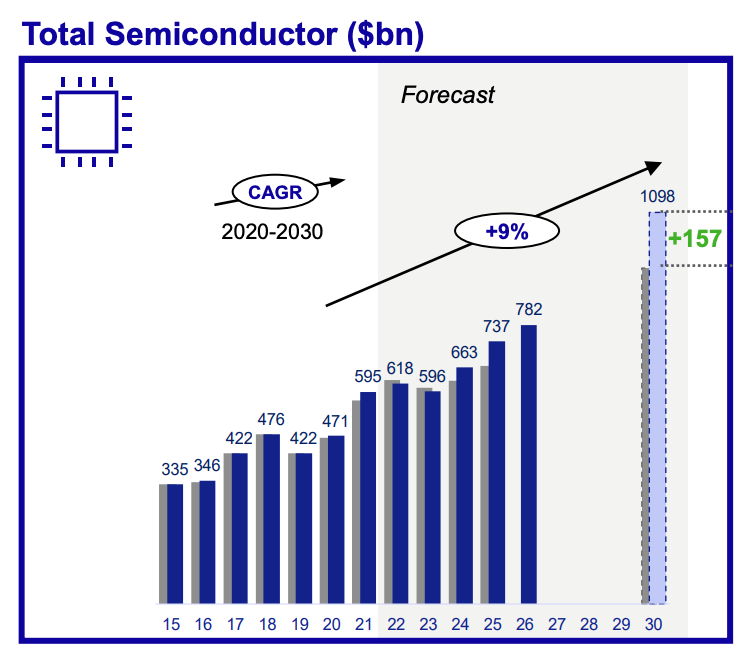

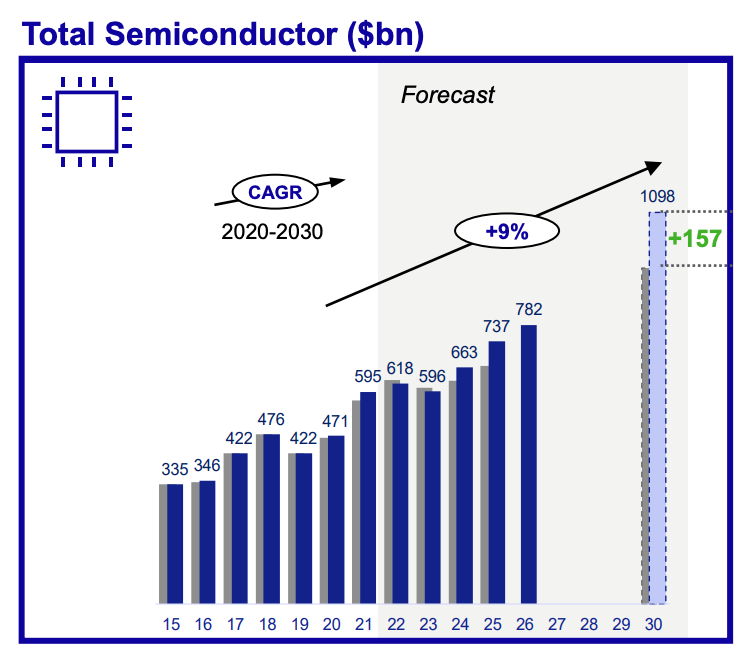

电子发烧友网报道(文/周凯扬)随着不少半导体公司纷纷公布财报,大家对去年尤其是第四季度的成绩都有所失望,唱衰整个产业的声音也常常传出。尽管如此,从ASML在去年投资者日上公布的预测来看,半导体终端市场从2022年到2030年,依然将实现9%的年复合增长率。只不过目前的预测下,没有给这一增长率拖后腿的,只有服务器、汽车以及工业电子市场,其中服务器市场更是有希望在2026年反超智能手机市场。

2022到2030年的半导体市场预测 / ASML

然而支撑起这一市场继续增长,并贡献主要运算能力的逻辑工艺演进,已经处于了一个放缓的状态,光刻系统的能耗性能已经上去了,晶体管的能耗性能也上去了,但晶体管密度、时钟频率的增长都已经逐渐趋于平缓。为了让逻辑工艺再次突破,业界也想出了不少办法。

系统设备的进化

每代逻辑工艺的提升,最关键的还是硬件基础,从90年代的i线***、到后来的KrF、ArF,以及现在逐渐成为主流的EUV***。***对于逻辑工艺的发展无疑是巨大的,而紧跟最新逻辑工艺的晶圆厂也为***公司贡献了2/3以上的销售额。

EUV,尤其是高NA EUV,已经被公认为我们实现下一轮逻辑工艺突破的最大驱动力。尽管这些***的价格已经突破天际,但晶圆厂仍在不停地下单,这是因为前期巨大投入的短痛,会慢慢带来成本、良率和周期上的长期收益。当然了,越来越小的PP与MP间距与更高的数值孔径,在满载利用率下固然能带来更低的工序成本,但目前的问题还是在光刻胶等配套材料上。

尽管研发时间不算短,但ASML还是规划好了到2032年的路线,2024年业界预计开始进入2nm时代,然后逐渐迈向A14、A10以及A7,届时借助的自然也是ASML第四代、第五代的高NA EUV***。

器件结构创新

如果我们坚持的仍是目前主流的FinFET结构,那别说挺进埃米时代了,就连做到2nm都无疑是一件难事。因此,在GAA晶体管架构进行演进就成了主流的研究方向,比如Nanosheet、Forksheet和CFET等。

Nanosheet作为GAA架构的第一代,也是三星选择在3nm上采用的技术,由于对纳米片的垂直堆叠,最大化了晶体管单鳍标准单元的有效宽度,同时又因为GAA的包围结构带来了改善的短沟道控制。这一结构可谓是同Track数量和同功耗下,在更先进的工艺上进一步提升频率的优秀思路。

而Forksheet由于在n型与p型晶体管之间加入了一个介电井减小了间距,从降低了米勒电容。这样一来,在同样的功耗下,前中后三段工艺加起来,相较Nanosheet能有10%的性能提升。

CFET则在堆叠上做到了极致,通过在单鳍上堆叠N&PMOS和NS沟道,再一次提高了有效宽度,而且这种垂直堆叠的方式不会因为NP之间的距离带来面积的增加。但这毕竟是GAA架构下最先进的技术,还存在着不少集成上的挑战,离最终量产还比较久远。

最后则是用来分配时钟和其他信号,同时也为多种器件供电的互联方案。根据IMEC的判断,从N5到N2的工艺节点内,双镶嵌结构依然会是主流,因为这是目前从成本来说最有效的方案。但双镶嵌结构并没有针对RC做出更好的优化,在用了低电阻TSV的方案后,最终还是得选择新的方案,比如半镶嵌结构。

半镶嵌结构由于存在气隙,可以更好地控制电容。所以IMEC预计在进入埃米时代后,应该都会选择半镶嵌的互联集成方案,不过这类方案目前仍处于研发阶段,而且在成本上也只能堪称有一定竞争力,同时未来还是得继续探索新的导电材料。

DTCO与STCO

从台积电、三星和英特尔等晶圆厂的各种宣发中我们可以看出,DTCO(设计与工艺协同优化)对于工艺节点的性能增益是巨大的,比如台积电就声称DTCO为5nm工艺带来的提升高达40%。

在EDA厂商、晶圆厂和IC设计公司的携手合作下,每个新工艺的出现都不再只有一个阶段,除了良率的稳步提升外,性能也还有继续增长的空间。与此同时,另一个概念,STCO(系统工艺协同优化)的概念也在这几年被抛出来,简单来说就是将多个芯片集成在单个封装上。

从STCO这一定义也就不难看出,这与先进的2.5D/3D封装和Chiplet设计脱不了干系。西门子EDA也给出了应用STCO带来的诸多优势,比如芯片设计团队可以并行开发SoC上的不同部门,设计者也能为每个区域的设计选择最优的工艺方案。除此之外,也可以扩展机械应力、固晶等一系列物理效应的早期分析,及早避免设计错误,从而导致较长的重新设计时间。

2022到2030年的半导体市场预测 / ASML

然而支撑起这一市场继续增长,并贡献主要运算能力的逻辑工艺演进,已经处于了一个放缓的状态,光刻系统的能耗性能已经上去了,晶体管的能耗性能也上去了,但晶体管密度、时钟频率的增长都已经逐渐趋于平缓。为了让逻辑工艺再次突破,业界也想出了不少办法。

系统设备的进化

每代逻辑工艺的提升,最关键的还是硬件基础,从90年代的i线***、到后来的KrF、ArF,以及现在逐渐成为主流的EUV***。***对于逻辑工艺的发展无疑是巨大的,而紧跟最新逻辑工艺的晶圆厂也为***公司贡献了2/3以上的销售额。

EUV,尤其是高NA EUV,已经被公认为我们实现下一轮逻辑工艺突破的最大驱动力。尽管这些***的价格已经突破天际,但晶圆厂仍在不停地下单,这是因为前期巨大投入的短痛,会慢慢带来成本、良率和周期上的长期收益。当然了,越来越小的PP与MP间距与更高的数值孔径,在满载利用率下固然能带来更低的工序成本,但目前的问题还是在光刻胶等配套材料上。

尽管研发时间不算短,但ASML还是规划好了到2032年的路线,2024年业界预计开始进入2nm时代,然后逐渐迈向A14、A10以及A7,届时借助的自然也是ASML第四代、第五代的高NA EUV***。

器件结构创新

如果我们坚持的仍是目前主流的FinFET结构,那别说挺进埃米时代了,就连做到2nm都无疑是一件难事。因此,在GAA晶体管架构进行演进就成了主流的研究方向,比如Nanosheet、Forksheet和CFET等。

Nanosheet作为GAA架构的第一代,也是三星选择在3nm上采用的技术,由于对纳米片的垂直堆叠,最大化了晶体管单鳍标准单元的有效宽度,同时又因为GAA的包围结构带来了改善的短沟道控制。这一结构可谓是同Track数量和同功耗下,在更先进的工艺上进一步提升频率的优秀思路。

而Forksheet由于在n型与p型晶体管之间加入了一个介电井减小了间距,从降低了米勒电容。这样一来,在同样的功耗下,前中后三段工艺加起来,相较Nanosheet能有10%的性能提升。

CFET则在堆叠上做到了极致,通过在单鳍上堆叠N&PMOS和NS沟道,再一次提高了有效宽度,而且这种垂直堆叠的方式不会因为NP之间的距离带来面积的增加。但这毕竟是GAA架构下最先进的技术,还存在着不少集成上的挑战,离最终量产还比较久远。

最后则是用来分配时钟和其他信号,同时也为多种器件供电的互联方案。根据IMEC的判断,从N5到N2的工艺节点内,双镶嵌结构依然会是主流,因为这是目前从成本来说最有效的方案。但双镶嵌结构并没有针对RC做出更好的优化,在用了低电阻TSV的方案后,最终还是得选择新的方案,比如半镶嵌结构。

半镶嵌结构由于存在气隙,可以更好地控制电容。所以IMEC预计在进入埃米时代后,应该都会选择半镶嵌的互联集成方案,不过这类方案目前仍处于研发阶段,而且在成本上也只能堪称有一定竞争力,同时未来还是得继续探索新的导电材料。

DTCO与STCO

从台积电、三星和英特尔等晶圆厂的各种宣发中我们可以看出,DTCO(设计与工艺协同优化)对于工艺节点的性能增益是巨大的,比如台积电就声称DTCO为5nm工艺带来的提升高达40%。

在EDA厂商、晶圆厂和IC设计公司的携手合作下,每个新工艺的出现都不再只有一个阶段,除了良率的稳步提升外,性能也还有继续增长的空间。与此同时,另一个概念,STCO(系统工艺协同优化)的概念也在这几年被抛出来,简单来说就是将多个芯片集成在单个封装上。

从STCO这一定义也就不难看出,这与先进的2.5D/3D封装和Chiplet设计脱不了干系。西门子EDA也给出了应用STCO带来的诸多优势,比如芯片设计团队可以并行开发SoC上的不同部门,设计者也能为每个区域的设计选择最优的工艺方案。除此之外,也可以扩展机械应力、固晶等一系列物理效应的早期分析,及早避免设计错误,从而导致较长的重新设计时间。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

热点推荐

昊衡科技:以十年 OFDR 积淀,让结构姿态 “看得见、测得到、控得住”

十年OFDR:自主研发,国产高端传感的突围之路十年间,昊衡科技坚持自主创新,深耕OFDR技术研发并实现国际领先。目前公司已获授权专利45项,构建起完整的知识产权壁垒,成为国内率先实现OFDR技术

新加坡电信与爱立信达成战略合作以加速5G-A演进

新加坡电信与爱立信近日达成战略合作,旨在加速5G-A演进,使其为一个可编程AI-powered的数字平台,以此推动企业转型,强化新加坡数字经济并确保网络基础设施适用于其未来十年发展需求。

黄仁勋:未来十年很多汽车是自动驾驶 英伟达发布Alpamayo汽车大模型平台

在当地时间1月5日黄仁勋在CES 2026上发表主题演讲,黄仁勋的新年首场演讲中重点提及自动驾驶、机器人等。 黄仁勋:未来十年很多汽车是自动驾驶 黄仁勋认为AI发展的下一站是进入物理世界。黄仁勋

十年测试工程师复盘:CP与FT的边界究竟在哪?

边界如何移动这些年,CP和FT的边界一直在变。分享三个项目:案例1:消费级MCU(40nm工艺)这是最传统的模式。CP只测基本参数(开路/短路、IDDQ、低频功能),耗时<2秒;FT覆盖

发表于 12-23 10:11

云天励飞出席GAIR 2025 AI算力新十年专场

的完整过程。本届论坛直面智能体系的底层核心——算力,从架构、生态、工具链到产业化落地,探寻未来十年的关键变量。

东风岚图与宁德时代正式签署十年长期深化合作协议

12月17日,东风岚图与宁德时代正式签署十年长期深化合作协议,双方将在新技术合作、产品供应、品牌共建、全球市场协同等领域展开全方位深度协同,确保东风岚图未来动力电池的稳定供应与技术领先性,持续提升其在电池技术与供应链安全领域的综合竞争力。

技术为基,定义未来:广东固特科技如何引领超声切割行业十年?

行业标准而努力时,广东固特的目光,已经落在了未来十年的技术路线上。这种引领并非空谈,而是建立在三大核心支柱之上。一、第一支柱:超越行业标准的技术体系广东固特率先提出并贯彻

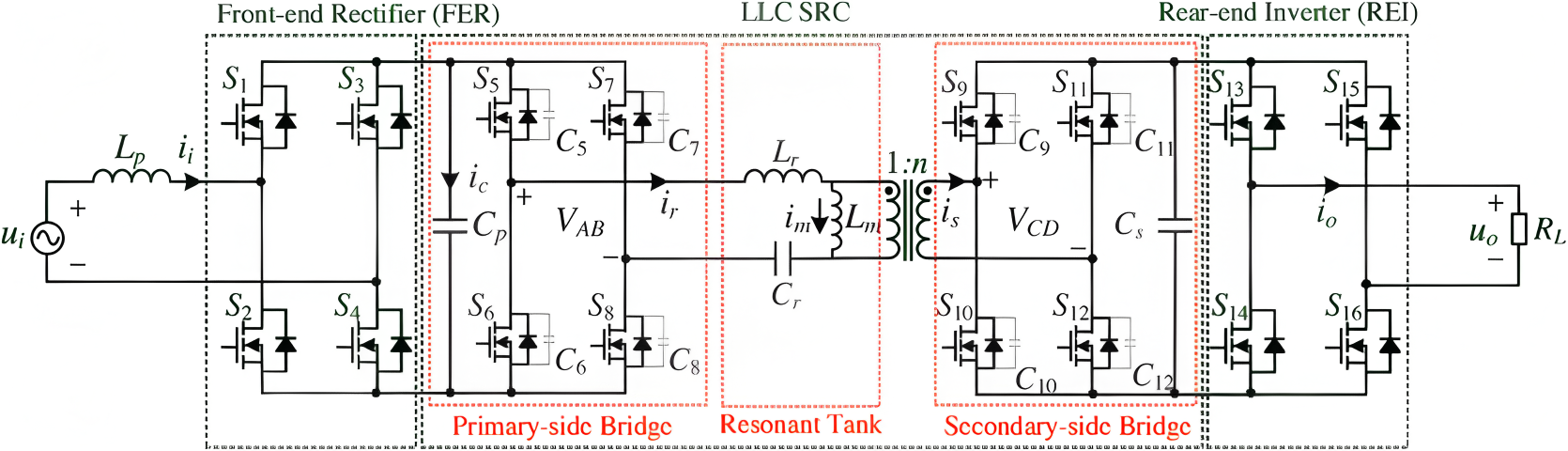

倾佳电子固态变压器(SST)技术路线演进与未来十年应用增长深度分析

倾佳电子固态变压器(SST)技术路线演进与未来十年应用增长深度分析及基本半导体SiC MOSFET系列产品的战略应用价值报告 倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连

华为五大创新开启非洲移动产业黄金十年

在2025年非洲通信展(AfricaCom 2025)期间,华为无线网络产品线营销副总裁陈实发表“创新开启非洲移动产业黄金十年”主题演讲,表示非洲是充满活力的数字热土,华为将聚焦“新流量、新体验

Wi-Fi FEM研发,开启第二个十年

转载自《钟林谈芯》 人生如逆旅,我亦是行人。十年之旅, 一起同行, 步步开花,Wi-Fi FEM研发,我们开启第二个十年。 2015年,在 锐迪科 (RDA)一起走进Wi-Fi FEM赛道,未

十年·NDI在中国|影像志:见证视频IP化的成长与未来

十年前,NDI改变了世界;十年后,千视与NDI携手,共同定义未来!《十年·NDI在中国纪录片》从一个疯狂的愿景开始NDI的诞生,源于一个看似疯狂却极具远见的构想。它的创造者坚信:随着视

NDI 十年:诞生 · 愿景 · 发展 · 未来— 独家专访 NDI 创始人 Andrew Cross博士

十年前,几乎没有人相信视频制作能脱离昂贵的基带设备,完全依赖电脑与网络;而今天,NDI已成为全球公认的IP视频制作标准。2025年,既是NDI的十周年,也是Kiloview与NDI携手走过的第

十年积淀,DPVR AI眼镜将正式亮相

表示想要购买AI眼镜。一个新的智能设备时代,正在打开。在这个节点,深耕XR领域十年的DPVR(大朋VR),将带来它的首款AI智能眼镜——DPVRAIGlasses

BOE(京东方)“照亮成长路”公益项目新十年启幕 科技无界照亮美好未来

的“世界高城”理塘,寓意该项目历经十年耕耘达到了全新的高度,也标志着BOE(京东方)下一个十年公益征程的崭新起点将由此启幕。活动现场,BOE(京东方)宣布,今年将继续向四川理塘县、陕西富平县、青海玉树州杂多县等地区捐建30间智慧教室。同时,在理塘活动现场,BOE(京东方)

未来十年的逻辑工艺演进方向

未来十年的逻辑工艺演进方向

评论