工程师可以使用ADI公司的解决方案来应对心电图子系统设计的主要挑战,包括安全性、共模/差模干扰、输入动态范围要求、器件可靠性和保护、降噪以及EMC/RFI考虑因素。

心电图(ECG)是一种常见的医疗记录,在许多恶劣的环境中必须可读且准确。无论是在医院、救护车、飞机、海上车辆、诊所还是家中,干扰源无处不在。新一波高度便携的心电图技术使得在更多环境中测量心脏的电活动成为可能。随着ECG子系统进入更多的院外应用,制造商面临着持续的压力,需要降低系统成本和开发时间,同时保持或提高性能水平。由此对ECG设计工程师提出了相当大的要求:提供一个安全有效的ECG子系统,能够承受预期使用环境的挑战。

本文确定了ECG子系统设计中通常被认为是主要挑战的内容,并推荐了缓解这些挑战的各种方法。讨论的挑战包括安全性、共模/差模干扰、输入动态范围要求、器件可靠性和保护、降噪以及EMC/RFI考虑因素。

挑战#1:满足最高安全水平,以确保ECG子系统安全有效

安全始终是ECG设计人员最关心的设计问题。必须保护患者和操作人员免受来自交流电源的电涌或过压以及通过ECG电极的任何电流路径的影响,这些电流路径可能超过建议的10 μA rms限值。最终目标是确保患者和操作员的安全,如果ECG子系统本身或连接到患者或操作员的其他医疗设备出现故障,则可能发生危险电压或电流。

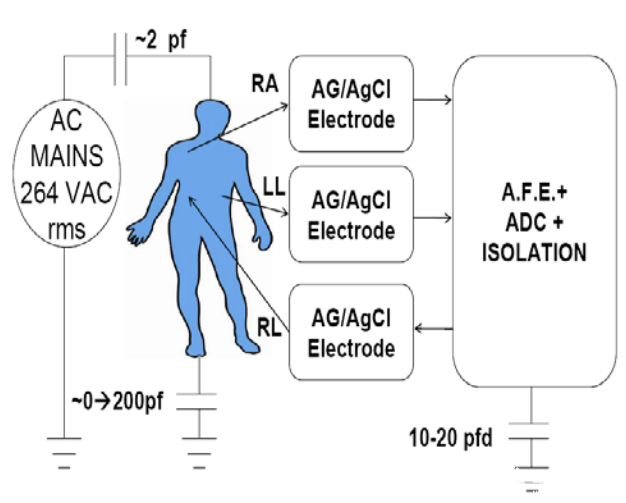

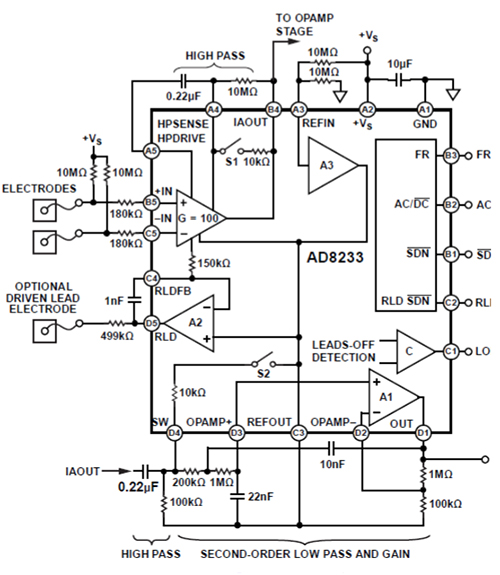

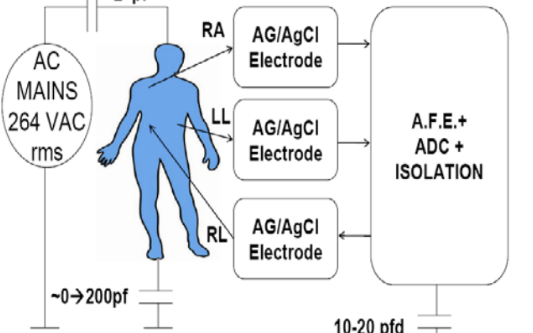

图1.交流电源耦合概述

在开始ECG设计之前,工程师必须确定临床应用,以及设备的使用和存储位置。工程师必须评估所有可能的误用设备以及可能导致向患者施加电流的潜在外部连接。当施加的电流(灌电流或拉电流)限制在10 μA rms以下时,即使在单故障故障期间,也可以保持操作员和患者的安全。必须保护患者免受意外电击,并且必须保护心电图设备免受紧急使用心脏除颤器产生的极端电压的影响。

心电图系统必须符合联邦法规以及国际标准和个别国家的指令。在美国,食品和药物管理局 (FDA) 将医疗产品分为 I 类、II 类或 III 类。这些分类类别会影响产品设计和审批流程。例如,用于诊断心律的便携式动态心电图监测仪被认为是II类设备。相比之下,带有ECG子系统的心脏监护仪/除颤器被指定为III类。

设备分类的意义是什么?在其设备分类网页上,FDA指出。

您的设备被分配到的类别决定了FDA批准上市所需的上市前提交/申请类型。如果您的设备被归类为 I 类或 II 类,并且没有豁免,则需要 510k 才能进行营销。所有被归类为豁免的设备都受到豁免限制。设备豁免的限制在 21 CF xxx.9 中涵盖,其中 xxx 是指第 862-892 部分。对于III类设备,除非您的设备是预修正设备(在1976年医疗器械修正案通过之前在市场上,或与此类设备基本等效)并且不需要PMA,否则将需要上市前批准申请(PMA)。在这种情况下,510k将是进入市场的途径。

设备分类取决于设备的预期用途以及使用适应症。

每个医疗器械的分类/评级为 B 型、BF 型或 CF 型。 这些分类会影响设备的设计和使用方式。根据 IEC60601-1 标准,适用不同的漏电流限制和安全测试。IEC标准还将应用部件定义为医疗设备中与患者进行物理接触以使设备执行其预期功能的部分。

大多数医疗设备被归类为BF型或CF型,BF型设备与患者有导电接触,但与心脏没有导电接触。CF型保留用于直接接触心脏的设备和部件。建议ECG设计人员将每个ECG应用作为CF III类系统来处理。设计人员无法控制如何将ECG子系统应用于患者,如果患者有心脏接入点,则由于应用部件可能直接连接到心脏,因此该设备必须归类为III类。所有心脏监护仪/除颤器均被归类为 III 类设备。

人类心脏对 50 Hz 至 60 Hz 范围内的电流最敏感。在50 Hz/60 Hz下,通过心脏时,只要34 μA rms就会损害心脏并导致危及生命的事件。考虑到将心电图系统连接到患者时可能发生的各种程序,包括起搏器/AICD(自动植入式心律转复除颤器)的留置导管,目前允许的电流限制为50 Hz / 60 Hz设置为10 μA rms。在ECG设计中,无故障条件下的限值为10 μA rms。美国心脏病学会(ACC)还建议将10 μA rms的限制也扩展到单故障故障。

设计人员必须检查电极之间、电极到电路或接地的电流可能产生电流可能超过10 μA rms的单故障场景的所有情况。该源/灌电流是频率的函数,但10 μA rms限值的频率范围为直流至1 kHz。从1 kHz到100 kHz,电流电平随频率线性增加:从1 kHz时的10 μA rms到100 kHz时的1 mA rms。高于100 kHz时,电流限制为1 mA rms。

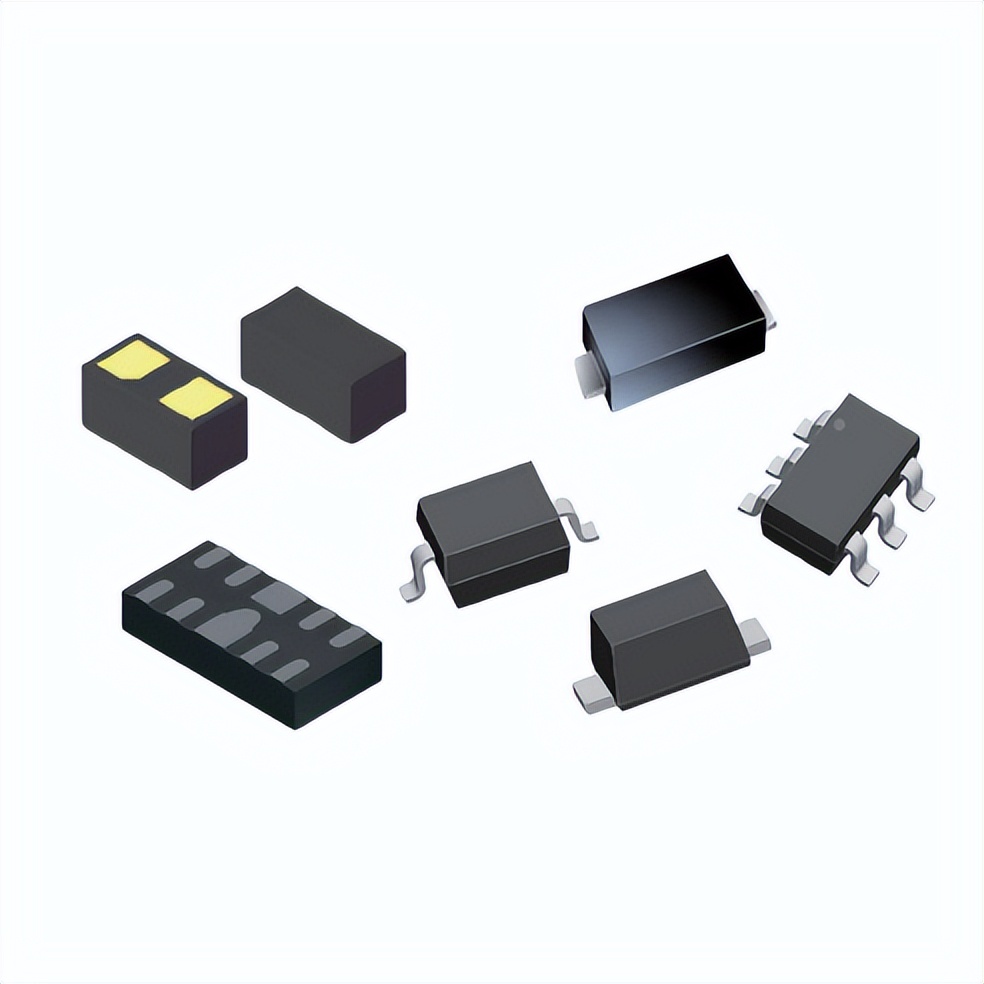

解决方案的形式是放置在信号路径中的电阻和/或限流器件。ADI公司生产的元件有助于满足患者安全需求。

挑战#2:共模和差模环境信号和射频干扰(RFI)

心电图测量心脏电气系统产生的电压。同时,ECG子系统必须抑制环境电信号,例如交流电源,安全系统和射频干扰(RFI),以放大和显示ECG信号。共模电压不能提供有关心脏的任何有用信息,实际上可能会妨碍测量精度。ECG系统必须能够抑制共模干扰,同时响应目标信号——差模ECG电压。在存在小差分信号的情况下抑制大共模信号的能力与系统的共模抑制(CMR)有关。

共模抑制可以通过多种方式测量。本文讨论了两种方法。第一种是将所有ECG电极连接在一起,并相对于ECG模拟前端电压基准驱动电极。对于单电源供电,基准电压源可以采用由RLD电极驱动的虚拟电压的形式,该电压电平位于单极性电源和隔离地之间距离的一半处。在这种情况下,共模抑制是相对于输入电平(20×log (V外/V在)).V在是施加的共模电压,V外是出现在特定目标引线上的电压。为了查看导联II的共模抑制,将电压施加到相对于右腿驱动端子的所有电极输入端(如果这表示ADC或RLD基准电压源的中点),并且器件被编程为显示导联线II。导联线 II 处出现的电压为 V外,施加电压,V在.

测量共模抑制的另一种方法是将所有电极连接在一起并相对于接地驱动它们。同样,共模抑制的定义是20×log (V外/V在),其中 V在是共模驱动信号和V外是在感兴趣的特定引线上看到的信号。

子系统设计和组件选择的这一部分需要对人体、交流电源和输入 RFI 进入和通过患者的环境耦合以及随后对 ECG 放大器在尝试抑制输入共模信号时的性能的影响进行建模。输入RFI通过多种方法去除,包括差模和共模滤波、环境屏蔽和算法。

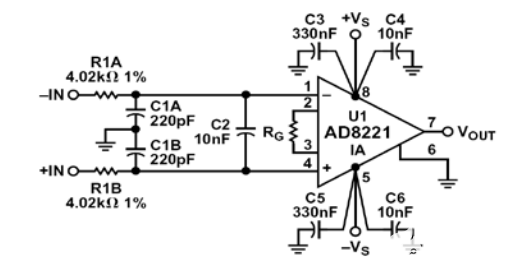

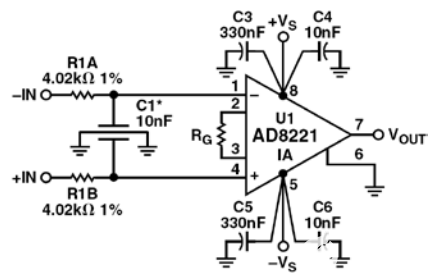

图2所示为传统的高频、低通滤波器网络,该网络容易出现C1A、C1B和C2值的差异。图3显示了一个集成的X2Y电容方案,由于X2Y结构和设计的性质,该电容提供了更高的性能。

图2.传统的高频、低通滤波器网络

图3.集成 X2Y 电容器实现

专门的ECG设计人员应对潜在环境进行建模,不仅要确定交流电源共模信号,还要确定连接到患者时可能到达ECG电极的其他共模和差模信号。大多数ECG电缆中都嵌入了保护电阻,用于除颤器保护。这种影响,加上电缆电容和前端EMI滤波的差异,会导致共模信号变得不平衡,从而导致相移和共模到差模的转换。

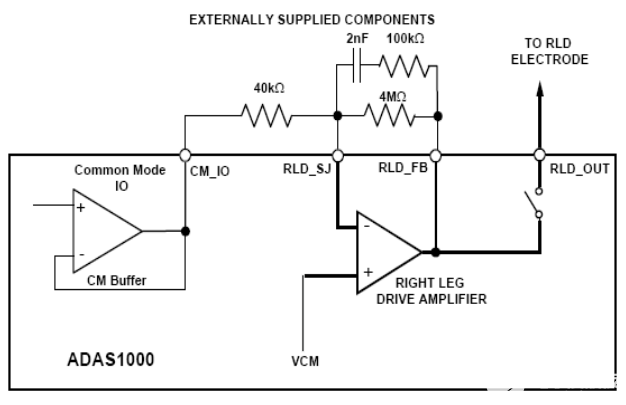

一种称为右腿驱动 (RLD) 的技术可以降低多导联配置的 CMR 要求。即使在2引脚系统中,放大器相对于接地的共模电压也可以降低,方法是使用一种RLD形式,将电流与输入的CM信号异相驱动180度回电极。由于电极阻抗不匹配,电流注入必须考虑到这一点,调整相对电流/相位以最小化有效共模信号。

简而言之,放大器输入必须具有足够大的共模(CM)和差模(DM)信号范围,以适应来自交流电源以及其他外部推理源(例如设备开/关和射频传输源)的CM/DM信号。差分放大器输入端零失调时的共模抑制必须与差分输入电压高达±1 V时一样好。

电力线干扰的其他解决方案包括DSP技术,如减法算法。为了帮助设计人员,ADI公司提供了可降低大输入共模信号影响的元件:CMR INA放大器、PLL、转换器以及用于ock-in放大器系统的同步调制器/解调器。ADAS1000 ECG AFE具有高差分输入阻抗和RLD特性,可解决共模抑制问题。

挑战#3:模拟前端共模和差模动态范围

心电图设备必须能够在患者用除颤器电击时快速做出反应。医生可能需要在除颤后一秒钟内查看患者的心电图。如果通过某些类型的金属(例如不锈钢)施加此脉冲,则材料的除颤后极化可能在 0.7 秒后高达 1 伏。这种差分偏移以及潜在的电磁(EMI)和/或射频干扰(RFI)可能会超过ECG前端的输入范围。简而言之,放大器饱和,看不到ECG信号。

ECG设计必须能够在这种类型的瞬态输入期间保持其共模和差分输入性能。由于大多数ECG系统现在在全球范围内销售,设计人员还必须解决最坏情况下的交流电源输入范围。举个例子:在西澳大利亚,交流电源电压可高达264 VAC rms,尖峰为6 kV。在这种环境下,共模抑制必须比交流电源电压为120 VAC rms的美国高出大约两倍。这一事实,以及可能发生的电极偏移和极化,需要高差分和共模输入动态范围。由于ECG电压介于100 μV和3 mV峰峰值之间,因此在目标信号数字化之前,模拟前端的动态范围输入能力非常重要。现代ECG前端的动态输入范围约为Ag/Ag-Cl电极应用的±1 V,除颤器垫应用的动态输入范围约为±1.5 V或更高。

一些系统采用单电源电压工作,生成的虚拟地在电源接地和电源轨之间向患者施加中点电压(无电流)。这通常是RLD电路的一部分。电极放大器相对于该中间电源轨,以确保不会注入交流或直流电流。相对于该虚拟接地所需的输入动态范围为±1 V,这是除颤后快速响应和预期最坏情况环境条件所需的。

Figure 4. Right Leg Drive—Possible External Component Configuration

ECG前端的噪声性能、线性度、CMRR和差分增益不得受到放大器特定输入工作点的影响。每个电极的输入阻抗必须大于1 GΩ,电容约为10 pF或更低,最好在电极之间匹配。ADI公司的分立式仪表放大器AD8220和AD8226具有宽动态范围,可实现满足CMR需求的电路架构。ADAS1000 ECG AFE满足低噪声、高动态范围、CMR和线性度的要求。Blackfin处理器还满足ECG和自动体外除颤器(AED)设备的后端需求。®

挑战 #4:ESD、环境和除颤器保护

设计工程师必须保护ECG前端免受损坏。ECG系统需要内置保护电路来处理静电放电、除颤器放电或其他过压和过流事件。人手模型模拟人体触摸设备的静电放电,使用1500 Ω电阻和串联100 pF电容器来限制可以通过人手放电的电流。充电电压决定了可以施加的瞬时电压量以及如何限制电流。电压可能超过 18 kV。一些标准将电压设置为低至 8 kV。

大多数ECG系统具有使用人手模型的除颤器脉冲和ESD的输入保护。除颤器保护电路具有多种要求:将前置放大器的CMR保持在性能频率;将少于 5% 的输送除颤器能量从除颤电极/垫上分流;并充分保护前置放大器电路,以便在除颤器脉冲后可以在显示屏或条形图上快速看到ECG。在急诊室 (ER) 中,一秒钟(或更短)的延迟是所需的响应时间。

除颤器保护电路可以采取两种形式。在一种情况下,ECG电缆是心脏监护仪除颤器的一部分,一系列电阻器(额定能量高压电阻器)通常会限制进入ECG前端的电流。此外,一些保护电路在保护电阻的ECG侧具有氩气或氙气灯泡,以将前置放大器侧电压限制在100 V以下。 此外,电压和电流限制装置可确保ECG系统不会损坏。设计人员应咨询特定仪表放大器 (INA) 或任何可能看到这种高电压和电流的有源/无源电路的制造商。可控硅整流器(SCR)提供部分过压保护。额定能量串联电阻器提供电流保护。也可以考虑限流器。

如果没有某种形式的保护,大多数有源器件无法承受与ESD测试相关的电压。需要与活动设备制造商联系,以确定所需的保护程度和建议的缓解措施。鼓励设计人员查看 FDA 有关用于除颤器保护的额定能量电阻器的指南。由于这些电阻器的测量/额定值不当,一些设备已被召回(FDA最近宣布,由于设备故障的报告,它正在审查AED的法规)。

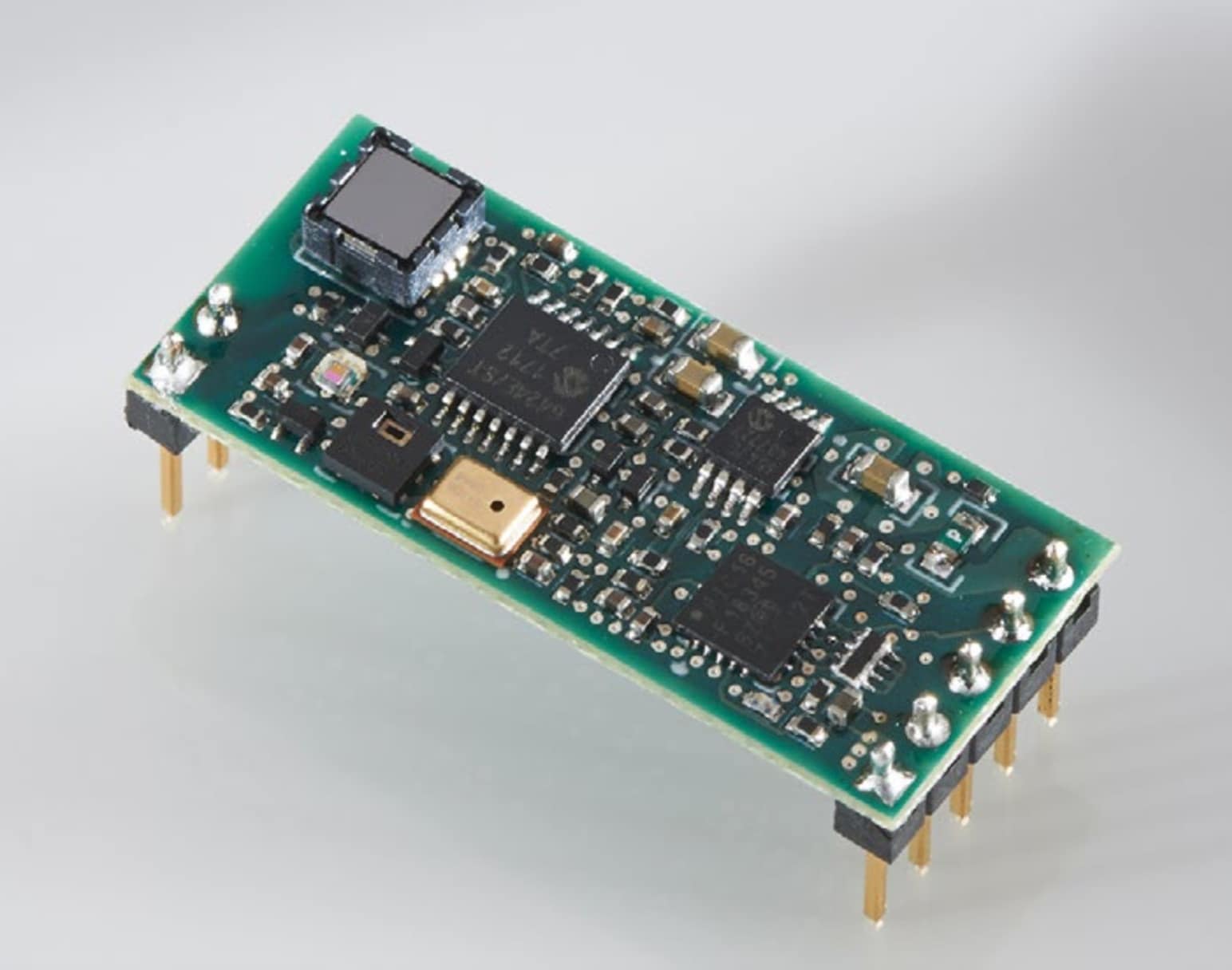

为了帮助设计人员使用分立式除颤器保护电路,ADI公司的元件已经过测试,可承受高水平的ESD和输入电流及电压。ADAS1000 ECG AFE在其封装引脚上包括大型ESD保护结构,并经过最大拉电流/灌电流容差评估。

挑战#5:电气噪声

ECG信号可能被多种来源破坏,包括电力线干扰、电极与皮肤之间的接触噪声、运动伪影、肌肉收缩和其他电子设备的电磁干扰。任何数量的信号源都可能导致心电图基线漂移或出现电噪声。对临床医生来说,重要的是心电图信号要清晰,所有电噪声组合起来尽可能小,以免混淆心电图诊断。对于诊断ECG应用,本底噪声应设计为满足10 μV峰峰值。

ECG设计人员必须采取措施过滤掉或丢弃所有这些噪声源。对等效输入本底噪声的要求因应用而异。对于心率监测器(HRM)等监护仪质量系统,在0.5 Hz至40 Hz带宽上指定约25 μV峰峰值的等效噪声值通常就足够了。在某些情况下,为了使系统功耗极低,可能会允许更高的本底噪声。即使在监视器质量应用中,本底噪声也需要低于25 μV峰峰值,因此需要充分了解临床环境和算法要求。

在设计完全诊断的 12 导联心电图系统(10 个电极)时,带宽可以低至 0.05 Hz 至 150 Hz,或宽至 0.05 Hz 至 2000 Hz。 起搏器检测要求将带宽进一步增加到至少 100 kHz。

例如,在动态心电图监测仪中,评估心电图波形的ST段用于确定STEMI(ST段抬高型心肌梗死);可以选择0.05 Hz至40 Hz的带宽,以帮助降低整体本底噪声,即使以评估超过40 Hz的更高频率分量为代价。在其他监护仪中,带宽可以是0.05 Hz至150 Hz甚至250 Hz,具体取决于患者和评估意图。

其他噪声考虑因素包括电缆移动(除非构造正确,否则会产生低频噪声)和突发噪声(也称为散粒噪声或电报噪声)。这种类型的噪音使医生无法看到心动周期各个部分的重要信息,包括ST段。

为了解决噪声问题,ADI公司采用各种电路技术来消除典型输入放大器的1/f特性,同时仍保持低高斯噪声和出色的器件线性度。ADI公司的CMOS工艺有助于实现极低的电报噪声水平。

挑战#6:电磁兼容性(ECM)和射频干扰(RFI)

ECG子系统必须受到各种外部/环境排放的影响。例如,附近的医疗设备以及环境中的高频工业或消费电子产品可以产生具有复杂调制/传输协议的足够E和H场。干扰信号可以通过传导或辐射发射到达ECG前端。

因此,在流程的早期,设计人员必须考虑辐射发射、辐射敏感性、抗扰度、传导发射和传导感化率/抗扰度的监管标准。由于世界各地的大气污染,越来越难找到一个允许对一个装置进行全光谱测试的开放区域测试场(OATS)。在一些国家,现在可以使用全高10米的测试室代替OATS。

系统设计人员必须与EMC测试机构合作,以确定IEC60601及其衍生产品第三版中定义的基本性能水平。读数裕量也必须定义为在特定频率下具有0.1 dB裕量,而正式通过可能是不可接受的,因为多个站点的OATS和10米腔室之间的读数可能存在多达±4.0 dB的变化。通常,8.4 dB裕量被认为是保守的。

设计人员应检查ECG的PCB尺寸、系统其余部分的数字和/或模拟I/O、输入电源形式、接地和法拉第屏蔽,这有助于防止ECG设计中嵌入的保护二极管和其他电路检测到辐射发射。ECG电缆本身可能在与电缆长度相关的特定频率下产生共振。如果其中一个谐振由ECG设计中的内部时钟或发射器激励,则可能难以符合标准的B级。这就是为什么在各种电缆上可能需要共模/差分扼流圈和直插式铁氧体的原因。

在正式测试之前,设计人员可以考虑使用一系列 E 和 H 场探头以及频谱分析仪对设计进行嗅探,以确定辐射频率和谐波。一系列预扫描可以确定热频率的位置以及它们与极限的接近程度。通过查阅源列表,设计人员可以确定该发射器上是否需要法拉第屏蔽,或者信号边沿的减速是否足够。系统内部的某些电缆可能需要铁氧体或其他滤波器来抑制谐振或高电平发射极。

另一种解决方案是寻找高度集成的小型封装器件,以满足辐射发射和入射辐射敏感性。ADAS1000 ECG AFE满足这些需求,是市场上首款在单芯片上集成导联脱落检测、呼吸监测和起搏器脉冲检测的器件。

总结

设计ECG子系统面临着大量的安全和信号处理挑战,其特点是小信号、宽带宽要求、电力线和环境的干扰,以及希望拥有非常低噪声的ECG放大器,同时保持极低的功耗。丰富的信息可以帮助设计人员开发安全、可靠和高性能的ECG设计。作为信号处理技术的领导者,ADI公司提供广泛的解决方案,帮助设计工程师克服所有主要的ECG挑战。

-

电源

+关注

关注

185文章

18709浏览量

261396 -

射频

+关注

关注

106文章

5944浏览量

172790 -

emc

+关注

关注

174文章

4323浏览量

190354

发布评论请先 登录

可穿戴设备的ECG系统克服心电图噪声和功率挑战

心电图(ECG)设计六大挑战与解决方案

心电图(ECG)设计如何防止ECG子系统受到各种外部和环境辐射影响

如何缓解GDDR6 DRAM实施所带来的挑战

ECG设计挑战的应对策略

ECG子系统设计的六大主要挑战及应对的方法建议

ECG设计挑战的缓解策略

ECG设计挑战的缓解策略

评论