光模块正在向着高速率、远距离方向发展。与100G以太网及更高速率的高速通信时,可能会出现传输错误,信号的传输距离会受到很多因素的限制。比如偏振模色散、色度色散、噪声、非线性效应等,这些因素会限制传输速率和传输距离同时提升。另外在实际传输过程中也并不存在理想的数字通道,信号在各种媒体的传输过程中总会产生畸变和非等时时延,这就意味着误码和抖动,而FEC编解码技术可以较好的改善误码性能。

什么是FEC?

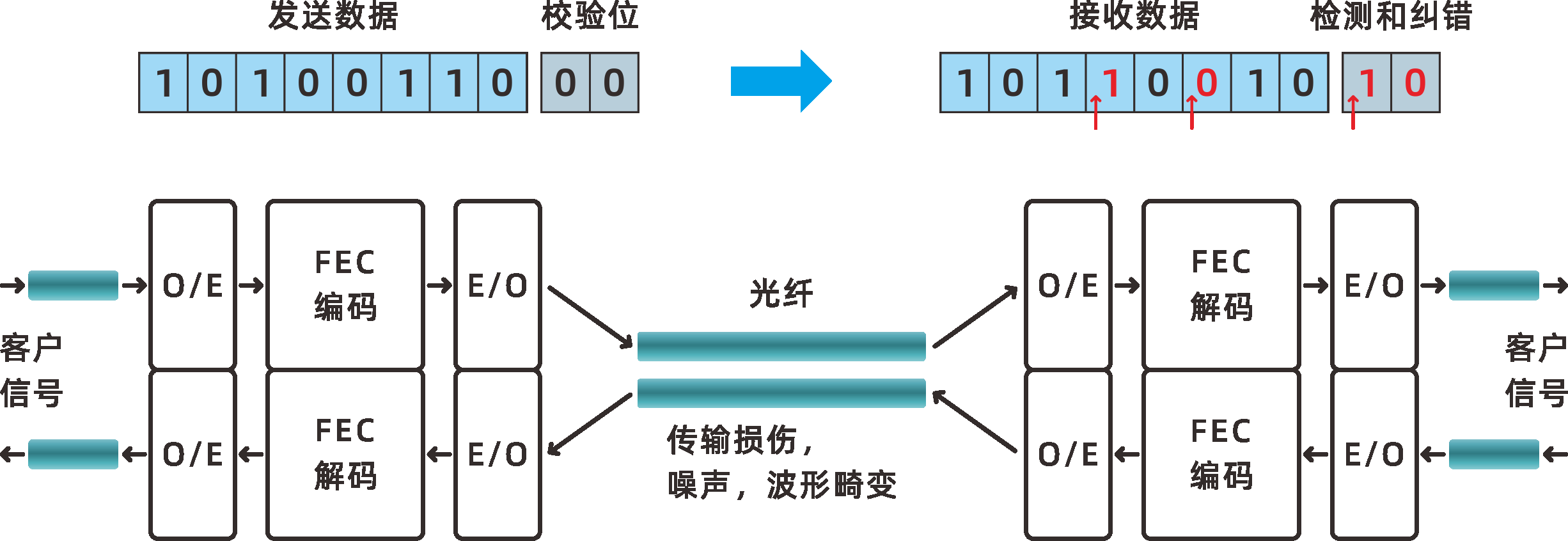

前向纠错码(FEC)和信道编码是在传输信道可靠性不高、强噪声干扰信道中进行数据传输时,用来控制接收数据包误码率(丢包、乱码)的一项技术。

我们的世界充满了噪声。噪声影响一切,包括数据传输和通信系统,无法摆脱。光通信系统的接收器直接受到噪声的影响,这使得理解接收到的信息变得更加困难。从技术上讲,当波通过光纤传输时,噪声会对光强度产生影响,而在长距离传输时,光色散会在信号中产生明显的缺陷。每当有噪声或光色散失真的影响时,光脉冲就会退化并失去其作为0或1的意义,接收器将接收到的光脉冲转换为电压。当接收器这样做时噪声太大,它会错误地解释数据,将0读为1或将1读为0。

FEC,在这一点上发挥作用,因为它减少了噪声对光传输系统传输质量的影响。通过在传输之前将开销信息添加到比特流中,该方法能够检测和纠正比特流中可能存在的部分错误。数据块受专门函数的约束,这些函数的输出是奇偶校验位的生成。开销由冗余位组成,其中还包含奇偶校验位。之后,将初始数据块和这些新数据拼接在一起,产生FEC码字。之后,这个FEC码字沿着传输线发送。

需要在接收端的设备上配置相同的FEC模式,以便接收端的FEC解码器机制知道对FEC码字应用什么样的功能。这允许接收器FEC解码器机制选择功能来重新生成数据并以高精度去除FEC开销。结果,产生了初始数据比特流,然后将其发送到更高的网络层。

FEC类型

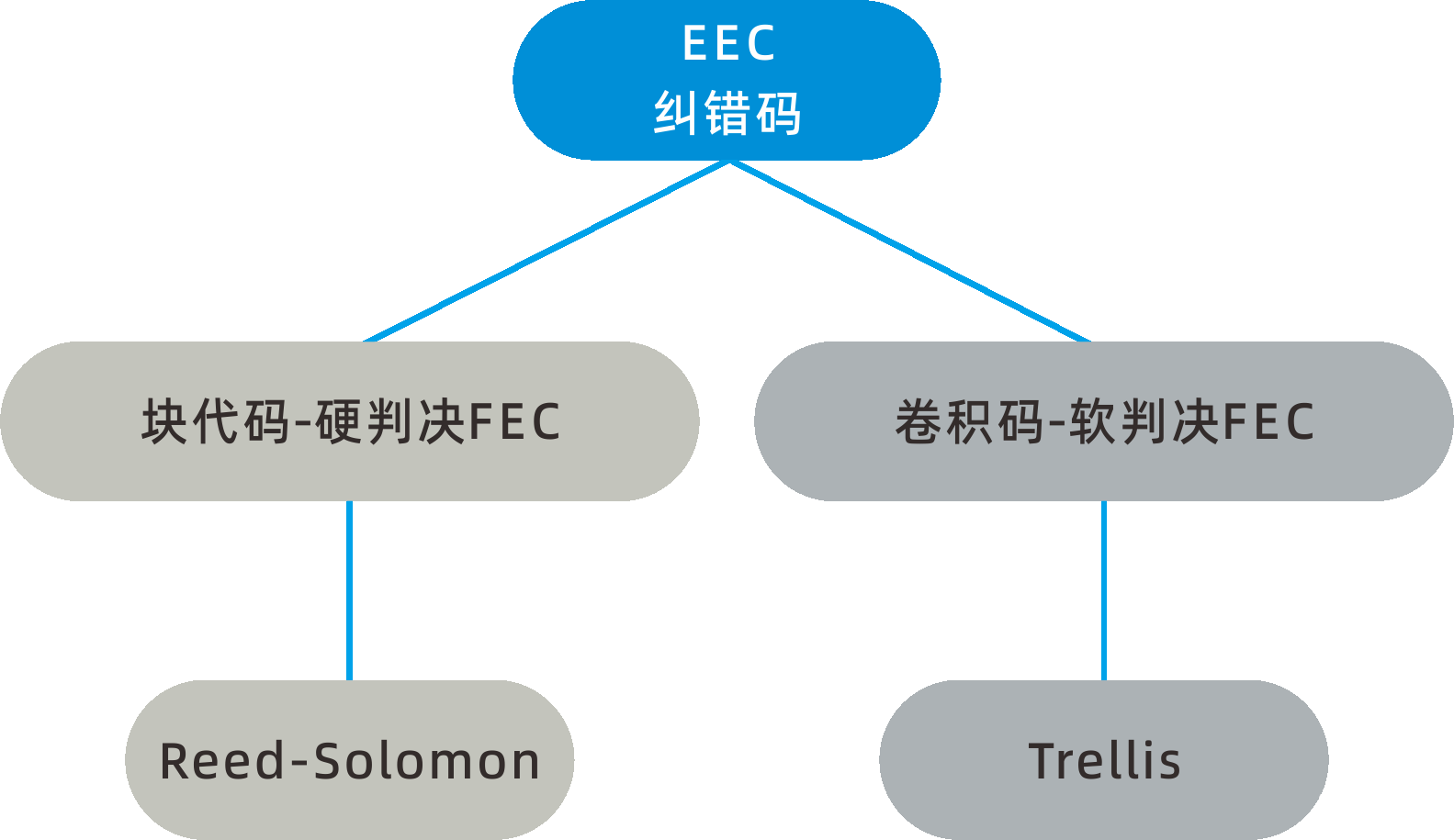

FEC代码可以检测并纠正有限数量的错误,而无需重新传输数据流。FEC码分为两种类型:块码和卷积码。块码被归类为硬判决FEC,而卷积码被归类为软判决 FEC。

为了纠正错误,块代码使用固定大小的块。最常见的块代码类型是Reed-Solomon。硬判决FEC算法代码采用固定长度的代码,判断每个符号对应的是0还是1。

软判决FEC算法中使用了卷积码,它们使用可变长度的符号流,并为0或1决策引入置信因子。这意味着接收器可以根据信号的幅度将位解释为0或1,如果它处于0置信区间或1置信区间内。这些代码将光传输系统的总距离可达性提高了30-40%。因此,软判决FEC有一个缺点:它增加了15-30%的开销,硬判决块代码是其三倍大。软判决FEC算法分支包括Trellis纠错码。

Reed-Solomon纠错码是当今通信行业中使用最广泛的错误检测机制。Reed-Solomon码对数据块进行操作,该数据块表示为一组称为符号的有限域元素,Reed-Solomon码可以检测和纠正各种符号错误。

当今通信链路中最常见的两种FEC方案是RS-FEC(528、514)和RS-FEC(544、514)。RS FEC(544,514)用于400G PAM4光模块链路和100G PAM4 (CAUI-2)链路;而RS-FEC(528、514)用于100G NRZ链路。

以下是两种RS-FEC方案的区别:

RS-FEC(528,514)编码以514符号的数据字段开始,每个符号10位,并添加14个奇偶校验符号以形成528符号的编码码字。然而,RS-FEC (544, 514)使用30个奇偶校验符号组成544个符号编码的码字。

由于PAM-4信号在电压电平之间具有更紧密的间距,因此眼图幅度是类似NRZ信号的三分之一,它略大并使用更多开销。结果,PAM-4信号的SNR降低并且更容易受到噪声的影响。为了补偿较低的SNR,KP-FEC设计有较高的编码增益。KP-FEC有可能纠正每个码字多达15个符号,而KR-FEC最多只能纠正7个符号。

FEC优缺点

事物不止有美好的一面,因此使用FEC(前向纠错)有几个优缺点需要注意。

优点

FEC具有成本效益。该技术的主要功能是纠正传输错误,因此我们可以使用相同的硬件组件获得更好的结果,无需更昂贵的激光器和接收器。

FEC实时运行,可以使用简单的算法在几秒钟内纠正代码。

增加互连距离。在纠正代码时,FEC有助于在更远的距离接收信号,例如,使用SD-FEC在100G链路上可以实现高达30-40%的距离增加。

降低误码率(BER) 。

如果检测到错误,FEC不需要重传整个帧,仅检测和纠正冗余位。节省了原本会用于重传的带宽。

缺点

延迟增加。FEC采用一种算法,将开销字节添加到有效载荷中,随着有效载荷的减少,将数据从A点传输到B点所需的时间会更长。

链路配置可能需要额外的改动,因为链路的两端必须使用相同类型的FEC;因此,在互连不同品牌设备时,请记住这一点。

总的来说,在大多数情况下使用前向纠错的优点大于缺点,但它并不适用于每个光模块。FEC的实现和使用通常由使用光模块的系统以及模块本身的类型决定。

FEC注意事项

在链路两端匹配FEC

使用FEC时,需要考虑的一个简单因素是必须在链路两侧的交换机和光模块之间使用匹配的FEC类型。例如,如果光模块支持RS-FEC,则其插入的主机设备也必须支持RS-FEC,并且链路设置的另一端必须遵循相同的原则。但是,如果链路一侧的设备支持RS-FEC,而链路另一侧的设备支持SD-FEC,则FEC功能将不起作用,并且链路将无法在FEC开启的情况下工作。同样,如果FEC在链路的一侧打开而在另一侧未打开,则该链路将不起作用。

RS-FEC 25G前向纠错

Reed-Solomon前向纠错用于许多25G SFP28光模块,以增加25G-CSR、25G-LR、25G-ER和BIDI场景中的范围。

NRZ 100G前向纠错

除了100GBASE-LR4和100GBASE-ER4使用LAN-WDM发射器并且无需FEC即可达到所需的10km和40km距离之外,所有100G NRZ模块要达到最大传输距离都需要在主机平台上启用RS FEC(528,514)。

100G PAM4前向纠错

100G PAM4模块(100GBASE-DR、100GBASE-FR、100GBASE-LR和100G-ER)在光模块数字信号处理器(DSP)芯片内置了RS FEC(544、514) PAM4 (KP1),当这些模块被主机检测到,主机平台上的FEC被禁用。

PAM4 400G前向纠错

为了实现最佳性能,必须在主机设备上为基于PAM4的400G QSFP-DD模块启用FEC (544,514)。

结论

总而言之,随着当前事件增加系统带宽和整体网络速度,在长距离传输时必须考虑纠错。前向纠错使您能够接收高质量的信号而不会受到噪声的干扰,噪声会使信号失真,并且它可以通过低成本组件提供更长的传输距离。FEC技术已经是一个热门话题,但我们可以预期它会随着速度和光调制技术的进步而变得更加流行。

审核编辑黄昊

-

通信

+关注

关注

18文章

6450浏览量

140269 -

FEC

+关注

关注

0文章

41浏览量

14280

发布评论请先 登录

深入解析 ICS83PN161I:10G 以太网 FEC 时钟转换的理想之选

100G BIDI 80km ZR4光模块

是德科技推出全新多通道误码仪FITS-8CH

Microsemi ZL30169:OTN时钟转换器的卓越之选

语法纠错和testbench的自动生成

指令集测试的一种纠错方法

今日看点:我国科学家研制出高精度可扩展模拟矩阵计算芯片;Microchip 推出首款 3nm PCIe Gen 6 交换芯片

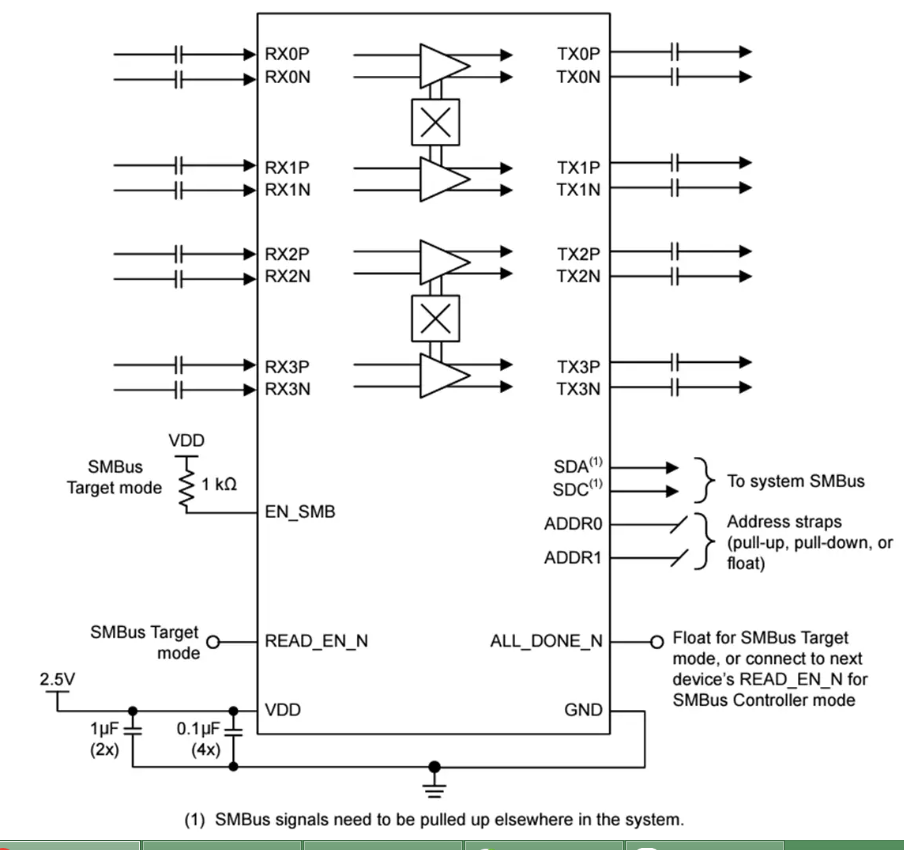

DS560DF810 56Gbps八通道重定时器技术深度解析

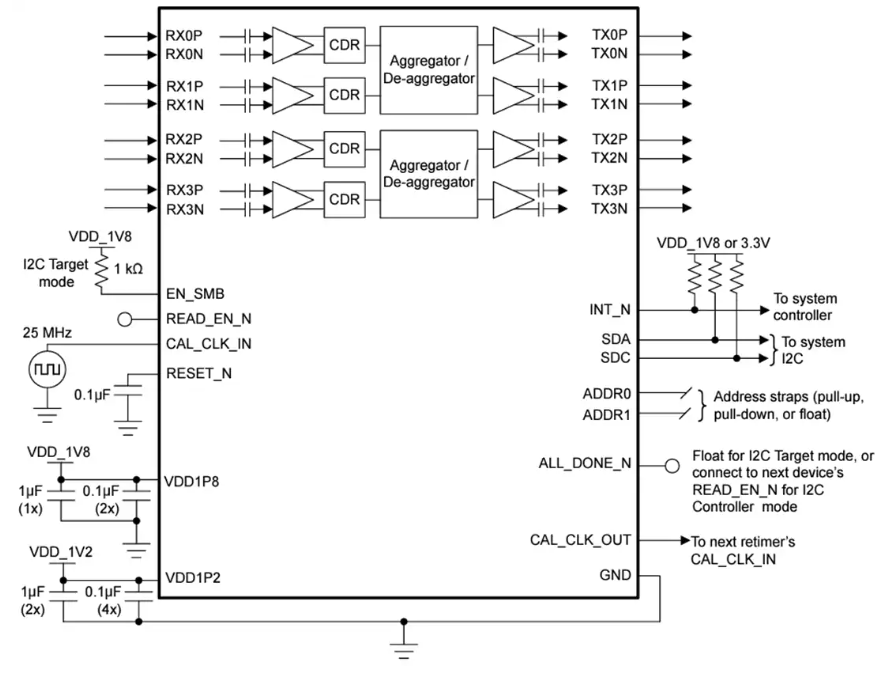

DS560DF410四通道多速率重定时器技术解析

易飞扬低延迟光模块产品系列为客户带来纳秒使用价值

什么是前向纠错(FEC)?FEC最全解析

什么是前向纠错(FEC)?FEC最全解析

评论