JESD204是一款高速串行接口,用于将数据转换器(ADC和DAC)连接到逻辑器件。该标准的修订版B支持高达12.5 Gbps的串行数据速率,并确保JESD204链路上的可重复确定性延迟。随着转换器速度和分辨率的不断提高,JESD204B接口在ADI公司的高速转换器和集成RF收发器中变得越来越普遍。此外,FPGA和ASIC中的柔性串行器/解串器(SERDES)设计自然开始取代传统的LVDS/CMOS接口到转换器,并用于实现JESD204B物理层。本文介绍如何使用 Xilinx FPGA 快速设置项目以实现 JESD204B 接口,并为 FPGA 设计人员提供一些应用和调试建议。®

JESD204B协议实施概述

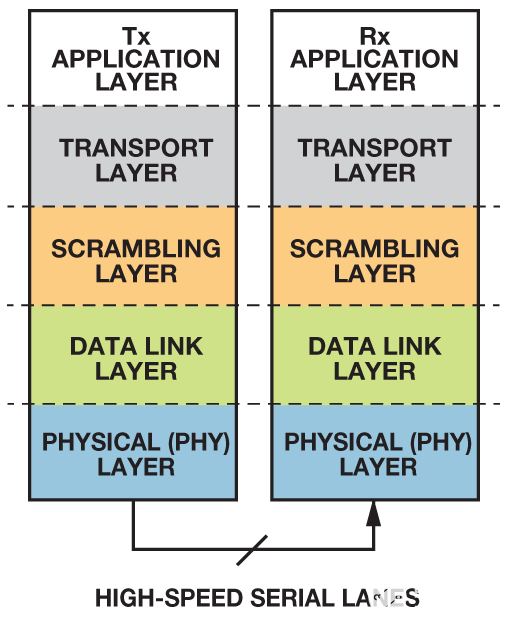

JESD204B规范定义了实现协议数据流的四个关键层,如图1所示。传输层映射样本和成帧、未加扰的八位字节之间的转换。可选的加扰层对八位组进行加扰/解扰,分散频谱峰值以降低EMI。数据链路层处理链路同步、设置和维护,并对可选的加扰八位字节进行编码/解码,使其与 10 位字符/从 10 位字符进行加扰。物理层负责以比特率传输和接收字符。

图1.JESD204B标准的关键层。

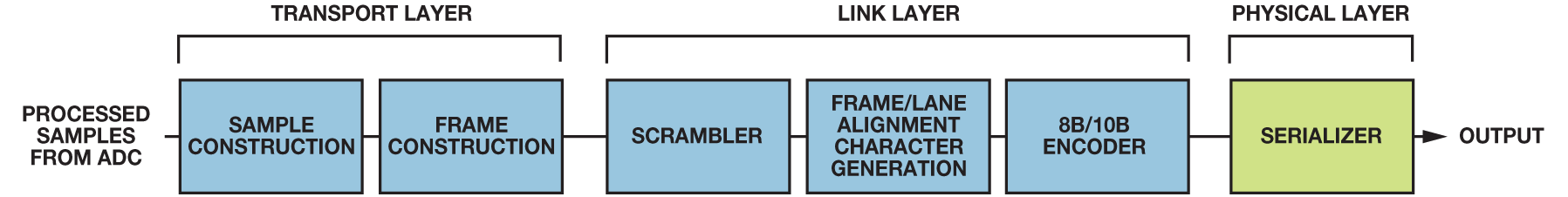

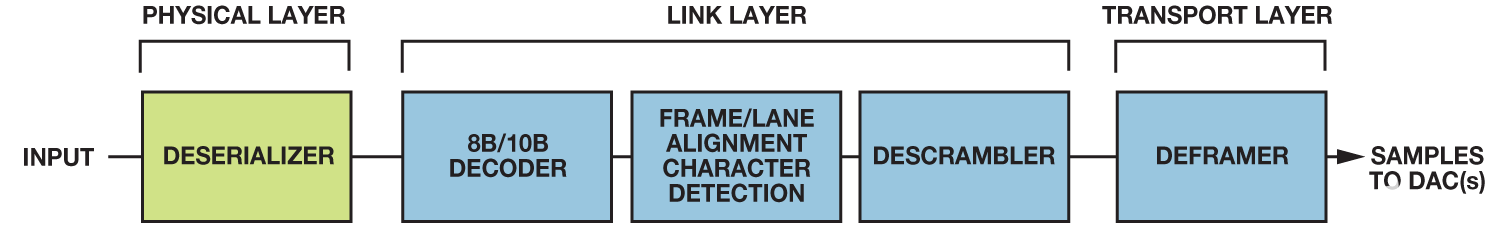

不同的JESD204B IP供应商可能以不同的方式实现这些层。图2和图3说明了ADI如何实现JESD204B发送和接收协议。

图2.JESD204B发射器实现。

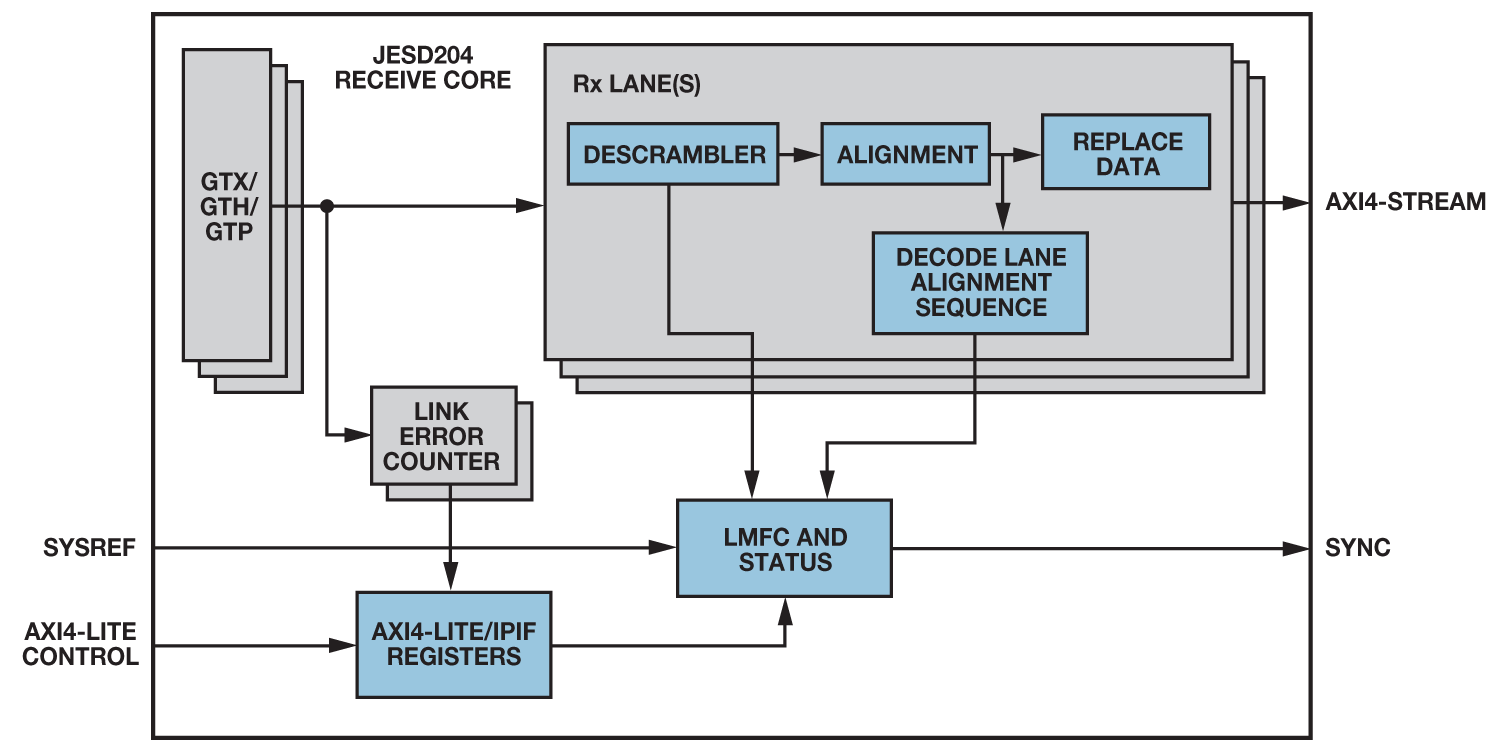

图3.JESD204B接收器实现

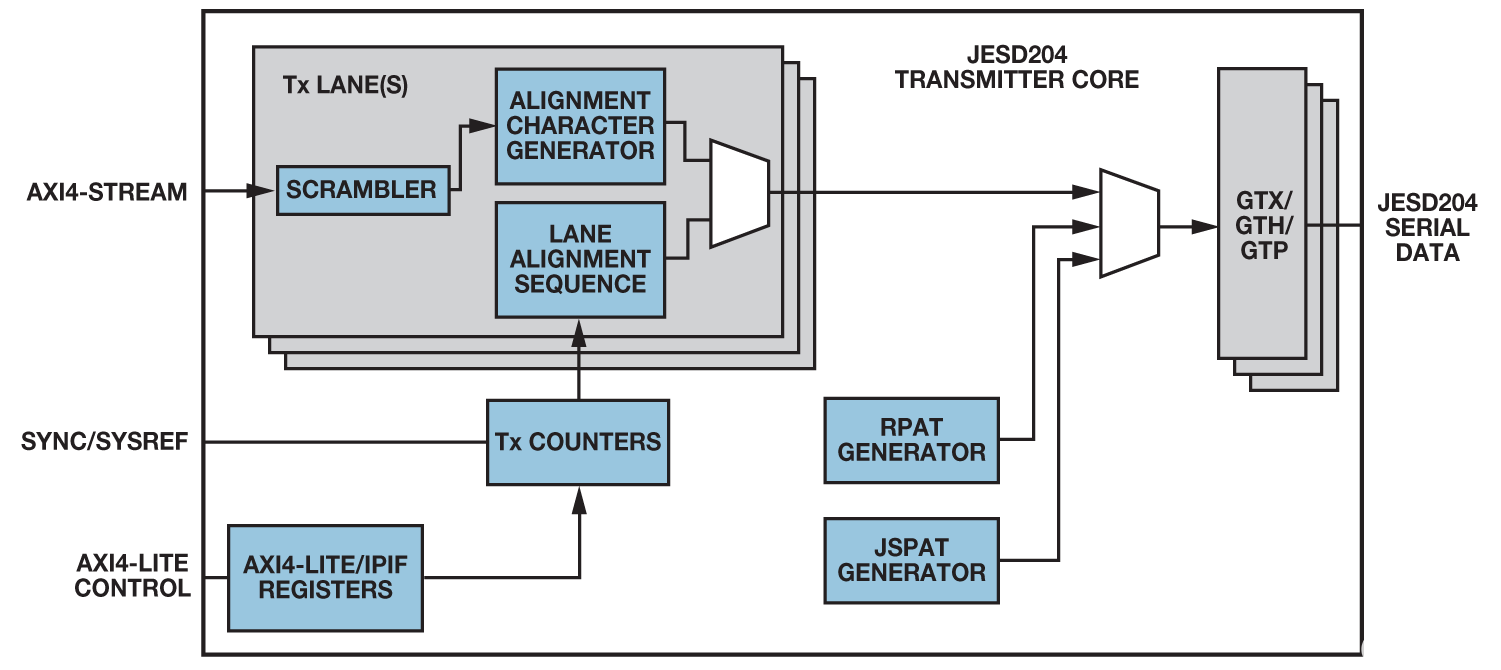

传输层的实现在很大程度上取决于特定转换器的配置以及它在样本和帧之间的映射方式,因此大多数FPGA供应商将其从其JESD204 IP中排除。此外,高度可配置、紧密集成的SERDES收发器集成在FPGA中。这些可用于支持各种串行协议,包括PCIe,SATA,SRIO,CPRI和JESD204B。因此,实现链路层的逻辑内核与实现物理层的可配置SERDES相结合,构成了JESD204B链路的基础。图 4 和图 5 显示了赛灵思 FPGA 上的 JESD204B 发射器和接收器的框图。发射器/接收器通道实现加扰层和链路层;8B/10B 编码器/解码器和物理层在 GTP/GTX/GTH 千兆收发器中实现。

图4.采用赛灵思 FPGA 的 JESD204B 发送器实现。

图5.采用赛灵思 FPGA 的 JESD204B 接收器实现。

采用赛灵思 FPGA 的 JESD204B 设计示例

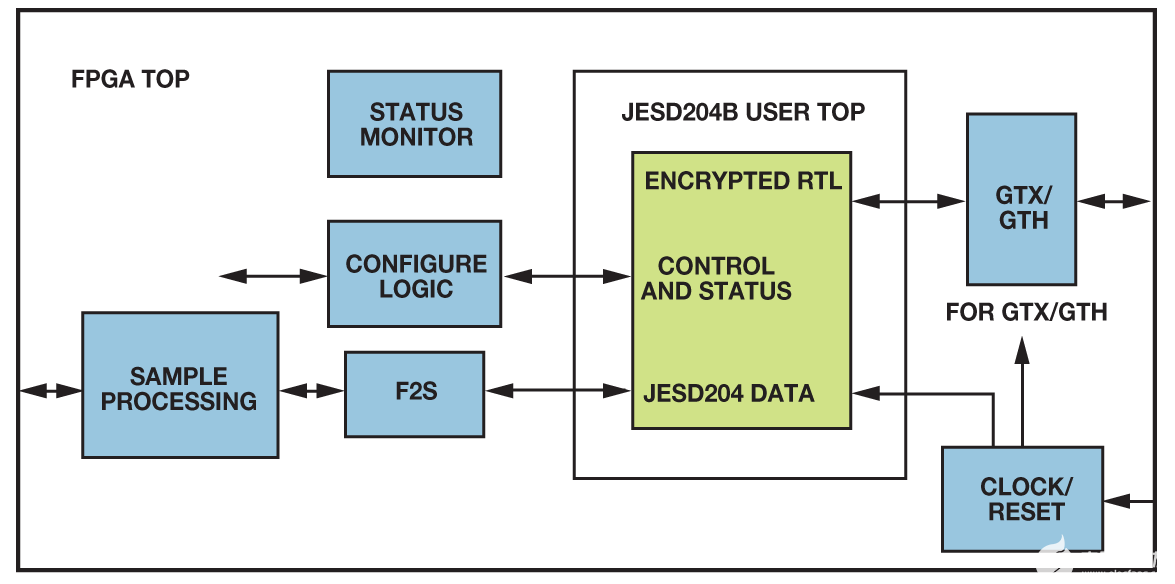

最新的 Xilinx JESD204 IP 核通过Vivado 设计套件®.Xilinx 还提供了使用高级可扩展接口 (AXI) 的 Verilog 示例设计,但此示例项目针对大多数应用进行了过度设计。用户通常有自己的配置接口,不需要为JESD204B逻辑集成额外的AXI。图6显示了一个简化的JESD204设计,旨在帮助FPGA用户了解JESD204的结构,并快速启动他们自己的基于FPGA的JESD204项目。

图6.JESD204B设计示例

加密寄存器传输语言(RTL)模块(由Vivado生成的JESD204逻辑IP核)等效于图4和图5所示的发射器和接收器模块。加密接口定义可在 Xilinx 示例设计文件中找到。然后将加密的RTL包装到JESD204B用户顶部。来自加密 RTL 的控制、配置、状态和 JESD 数据接口通过包装器与用户逻辑和 GTX/GTH 收发器数据连接。GTX/GTH 的符号对齐配置经过优化和更新,使收发器工作更可靠。

专用焊盘应用于SERDES收发器的GTX/GTH参考时钟。必须特别注意FPGA逻辑的全局时钟设计,包括内部PLL的时钟、并行接口、JESD204逻辑内核和用户特定的处理逻辑。此外,必须准确捕获JESD204B逻辑内核(子类1)的主系统基准(SYSREF)输入,以保证JESD204链路的确定性延迟。

GTX/GTH收发器和JESD204内核的复位顺序对于可靠的JESD链路初始化至关重要,因此JESD204内核应处于复位状态,直到GTX/GTH收发器中的内部PLL被锁定并且GTX/GTH复位。

需要帧到样本(F2S)模块来实现JESD204的传输层,该传输层根据特定的JESD204B配置将样本映射到帧或从帧映射帧。然后,由特定于应用程序的逻辑处理示例。辅助模块监控JESD204逻辑和物理层(PHY)状态,以便进行系统调试。

赛灵思 SERDES 收发器中的符号对齐

在SERDES接收器中,串行数据必须与符号边界对齐,然后才能用作并行数据。为了对齐数据,发射器发送一个可识别的序列,通常称为逗号。接收器在传入的串行数据流中搜索逗号,并在找到后将其移动到符号边界。这使接收到的并行字能够匹配传输的并行字。逗号通常是 K,它是 8B/10B 表中用于控制符号的特殊字符。对于JESD204B应用,发送器将发送K = K28.5符号流,用于代码组同步(CGS)。因此,FPGA可以使用K28.5作为逗号来对齐符号边界,用户可以指定逗号匹配是由逗号加号(运行视差为正号)还是逗号减号(运行视差为负)或两者组成。GTX/GTH逗号检测的JESD204B默认设置允许使用逗号加号或逗号减号来对齐逗号。

在某些应用程序中,默认逗号设置可能会导致符号重新对齐或对齐到错误的符号边界。这可能会导致混乱的8B/10B解码错误和JESD204B链路损坏。逗号加号和减号的组合更可靠,强制逗号对齐块连续搜索两个逗号,仅当接收的数据具有逗号加号或减号后跟逗号减号或加号且中间没有额外位时,才检测逗号。这有助于在线路速率较高或系统噪声过多时保持符号边界和链路稳定性。

基于FPGA的JESD204项目的设计考虑

从JESD204接收器到发射器的同步、低电平有效SYNC信号指示同步状态。正常运行期间链路重新初始化会导致样本数据混乱,因此必须实时监控链路状态。特别是,SYNC上的连续低电平意味着接收器无法识别接收数据流中的至少四个连续K28.5符号。如果发生这种情况,请检查发射器/接收器 SERDES 配置或确保发射器正在发送 K28.5。SYNC 上的持续高电平表示链路已建立并保持稳定性。当 SYNC 从高到低再回到高时,应计算低状态的持续时间。如果长度超过5帧加9个八位字节,则接收器检测到大错误并发送重新初始化JESD204链路的请求。如果持续时间等于两个帧时钟,则接收器检测到一个小错误,但不触发链路重新初始化。此功能可以显著简化系统调试和进一步的链路监控,因此用户应将其纳入其设计中。

8B/10B解码错误可能导致JESD204B链路重新初始化,但不是唯一原因,因此用户设计应能够计算每个通道的解码错误,以确定链路重新同步的原因。此外,SERDES链路质量可以通过8B/10B解码错误状态实时确定。

伪随机位序列 (PRBS) 为测量高速链路中的信号质量和抖动容限提供了有用的资源。大多数 FPGA 中的 SERDES 收发器具有内置的 PRBS 发生器和检查器,因此不需要额外的 FPGA 资源。因此,不要忘记实例化此函数,在评估误码率(BER)或眼图时应使用该函数。

SERDES收发器中始终使用缓冲器来改变内部时钟域。发射器和接收器的时钟设计错误或错误的时钟和数据恢复 (CDR) 设置可能导致缓冲区溢出或下溢。在这种情况下可能会发生一些链路错误,因此监视缓冲区状态是有意义的。缓冲区溢出和下溢的中断记录对于系统调试很有用,因此还应监视用户逻辑中不允许下溢或溢出的其他内部缓冲区。

结论

本文介绍了如何在赛灵思 FPGA 上快速实现 JESD204 模块,但该方法也可以应用于其他 FPGA。首先,了解FPGA供应商提供的JESD204逻辑内核和收发器的功能和接口,然后将它们实例化并封装到逻辑中。其次,全局设计FPGA时钟树并重置整个项目的顺序。第三,仔细定义JESD204逻辑内核、用户逻辑和收发器之间的接口。最后,添加必要的调试资源。遵循以下步骤将帮助您快速成功地设计JESD204接口。

审核编辑:郭婷

-

FPGA

+关注

关注

1656文章

22304浏览量

630779 -

收发器

+关注

关注

10文章

3796浏览量

110696 -

adc

+关注

关注

100文章

7453浏览量

553935

发布评论请先 登录

JESD204B的系统级优势

在Xilinx FPGA上快速实现JESD204B

JESD204B串行接口时钟的优势

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

JESD204B协议有什么特点?

JESD204B协议介绍

JESD204B的优势

在Xilinx FPGA上快速实现 JESD204B

JESD204B标准及演进历程

JESD204B是FPGA中的新流行语吗

在赛灵思FPGA上快速实现JESD204B

在赛灵思FPGA上快速实现JESD204B

评论