自UCIe产业联盟这一推进Chiplet互联生态的组织成立以来,采用Chiplet这种新兴设计方式的解决方案就迎来了井喷的趋势。根据Omdia的预计,全球Chiplet市场将在2024年增长至58亿美元,并在2035年达到570亿美元。

在这个潜力十足的市场面前,相关标准也在不断出炉,近日,国内集成电路相关企业及专家共同主导制定的《小芯片接口总线技术要求》团队标准在完成意见征求后,也正式通过了工信部中国电子工业标准化技术协会的审定。

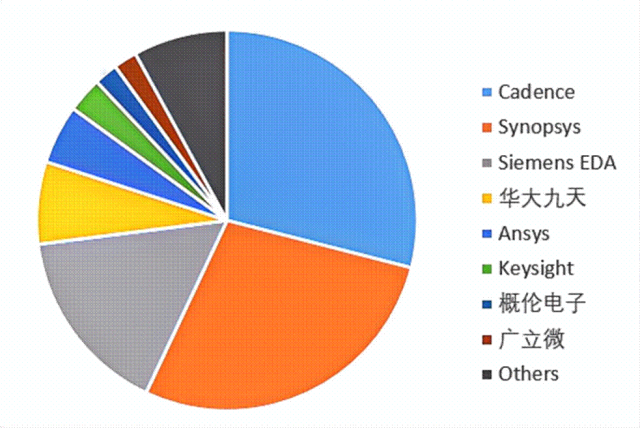

而在推进Chiplet普及的努力中,不仅有微软、Meta和谷歌这类促进者成员,还有IP厂商和EDA厂商作为贡献营收的主力军。除了快速布局的国际IP和EDA厂商以外,国内厂商也纷纷开启了自己的Chiplet进程。

IP厂商纷纷开启了Chiplet转型

芯原作为大陆排名第一、全球排名第7的半导体IP供应商,自然也不会错过这股Chiplet大潮。早在2021年,芯原科技在接受机构调研时,就表示他们已经开始与全球顶尖的晶圆厂开启基于5nmChiplet的项目合作,基于Arm架构的CPU IP Chiplet已经进入了芯片设计阶段,而用于AI运算的NPU IP Chiplet也已经进入了设计与实现阶段。

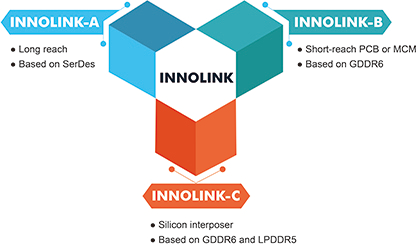

InnolinkChiplet方案/ 芯动科技

在Chiplet标准化道路上走得比较靠前的国内IP厂商当属芯动科技,早在2020年,芯动科技就和清华交叉院、紫光存储等企业共同发起了Chiplet产业联盟,同时推出了自己的InnolinkChiplet。根据芯动科技的描述,其InnolinkPHY和ControllerChiplet方案在物理层上可兼容UCIe协议,而且已经获得了Silicon验证,最高可支持3.4Tbps/mm2的带宽效率密度,以低功率小面积实现更大的互联带宽,非常适合用于高性能ASIC/FPGA硬件设计中。

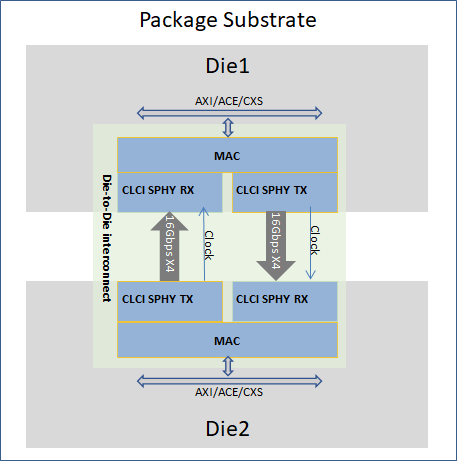

同样加入UCIe产业联盟的IP企业还有超摩科技,超摩科技的锦雷3200是专为Chiplet互联打造的die-to-dieSPHY IP,这也是超摩科技第一代Chiplet互联IP产品。参数上来看,锦雷3200可以做到每通道16Gbps的数据速率,在没有ECC的情况下做到小于10到15的BER。

锦雷3200 Chiplet架构/ 超摩科技

锦雷3200选择了台积电N12这一工艺节点,其ChipletD2D互联样片已经流片并完成了初步测试。从应用场景上来看,超摩科技给锦雷3200的定位包括云端计算、人工智能、数据通信和自动驾驶,都是需要高传输速率的场景。在超摩科技自己推出的企业级高性能CPU观云9000中,也用到了Chiplet的设计方法。

追求先进封装的EDA厂商开始发力Chiplet

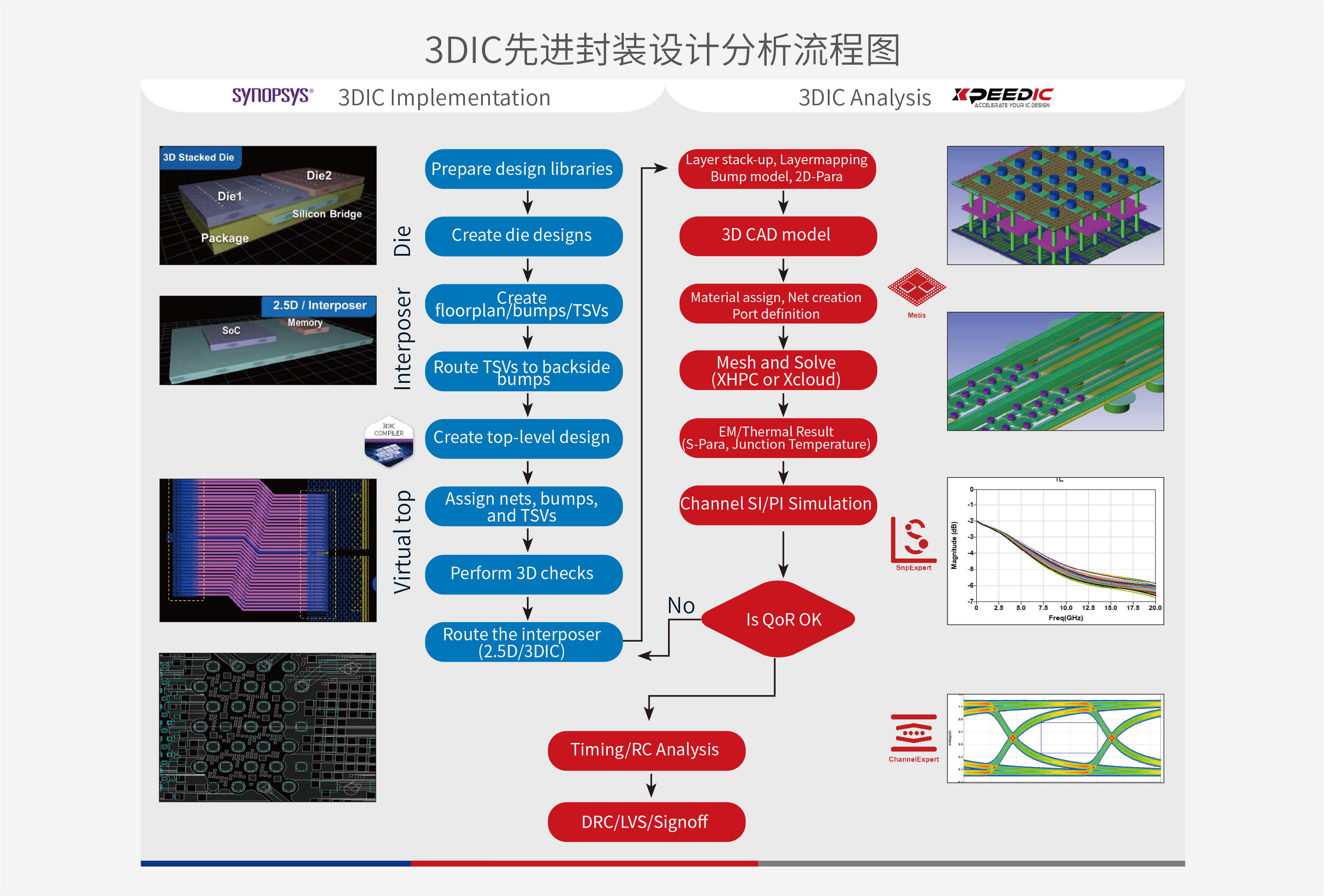

为了实现Chiplet的设计,同样需要EDA厂商出力,在设计工具层面上支持Chiplet。芯和半导体作为拥有3DIC先进封装设计分析全流程EDA的企业,也成了首家加入UCIe产业联盟的国产EDA厂商。

3DIC先进封装设计分析全流程EDA平台/ 芯和半导体

芯和半导体的3DIC先进封装设计分析全流程EDA平台,是业界首个用于3DIC多芯片系统设计分析的统一平台,集成了新思科技3DIC Complier和芯和半导体的Metis,做到了2.5D/3D先进封装的系统设计和仿真分析,全面支持2.5D Interposer、3DIC和Chiplet设计,也支持台积电和三星的先进封装工艺节点。

同样开始发力Chiplet的EDA厂商还有合见工软。要应对Chiplet在先进封装的挑战,必须打破在复杂多维空间系统级设计互连,实现数据的一致性和信号、电源、热、应力的完整性。为此合见工软在去年发布了先进封装协同设计环境(UniVistaIntegrator,简称UVI)之后,又在今年6月推出了UVI功能增强版。

UVI功能增强版首次真正意义上实现了系统级Sign-off功能,可在同一设计环境中导入多种格式的IC、Interposer、Package和PCB数据,支持全面的系统互连一致性检查(System-Level LVS),同时在检查效率、图形显示、灵活度与精度上都有大幅提升。

小结

除了以上提到的这些厂商之外,还有芯云凌、牛芯半导体、长鑫存储等企业也都纷纷加入了UCIe产业联盟。可以看出,对于国内专注于高速接口等高性能IP厂商和先进3D封装的EDA厂商来说,Chiplet的出现是一个不可多得的机遇。

芯片设计公司为了进一步减少成本加快上市时间,重复利用Chiplet的频率会逐步提高。但目前Chiplet仍主要用于复杂的高端芯片设计中,所用工艺也基本在5nm到16nm之间,随着未来制造成本进一步降低的话,相信会有更多的IP授权厂商完成Chiplet供应商的转型。

-

IP

+关注

关注

5文章

1893浏览量

156962 -

eda

+关注

关注

72文章

3158浏览量

184052 -

chiplet

+关注

关注

6文章

501浏览量

13667

发布评论请先 登录

为什么国产FPGA离不开统一EDA?从安全自主到效率翻倍,一篇说透核心逻辑

为什么国产MCU的工程生态很难统一?

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】跟着本书来看国内波诡云谲的EDA发展之路

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--中国EDA的发展

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--EDA了解与发展概况

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--全书概览

国产高性能ONFI IP解决方案全解析

中科亿海微牵头构建国产化FPGA/EDA生态 以协同创新破解“卡脖子”难题

英诺达ELPC荣登国产EDA“口碑榜”

【书籍评测活动NO.69】解码中国”芯“基石,洞见EDA突围路《芯片设计基石——EDA产业全景与未来展望》

合见工软与紫光同创合作推动国产EDA和FPGA产业快速发展

国产EDA又火了,那EDA+AI呢?国产EDA与AI融合发展现状探析

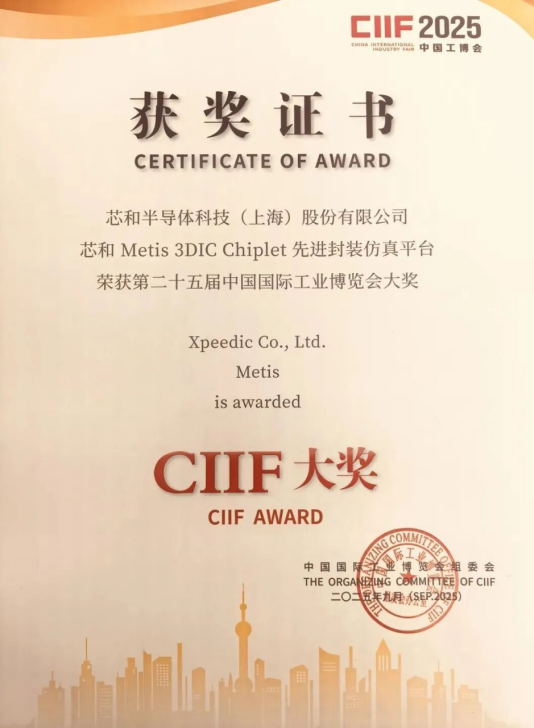

创造历史,芯和半导体成为首家获得工博会CIIF大奖的国产EDA

九霄智能国产EDA工具的突围之路

从IP到EDA,国产Chiplet生态进展如何?

从IP到EDA,国产Chiplet生态进展如何?

评论