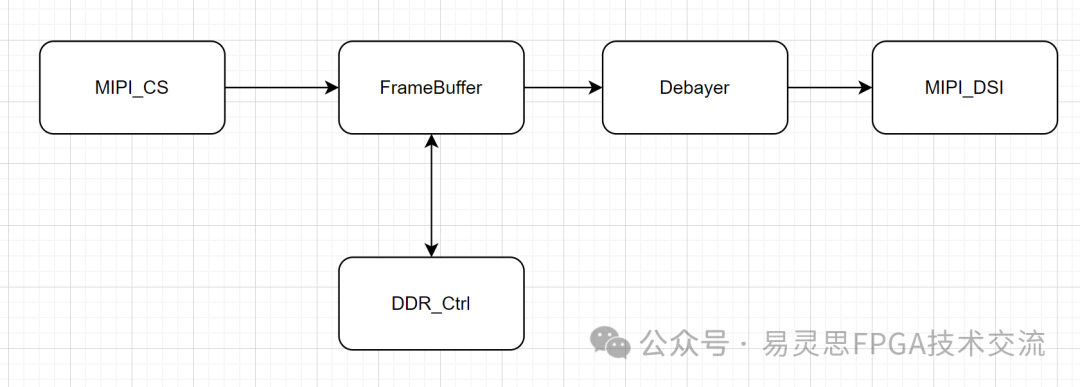

最近在帮助客户分析MIPI的问题,所以有此总结。第一次使用MIPI的人可能不知道怎么在易灵思平台上下手,今天我们来分享下MIPI的调试过程。

一、平台介绍

软件 :Efinity 2022.1.226.4.3

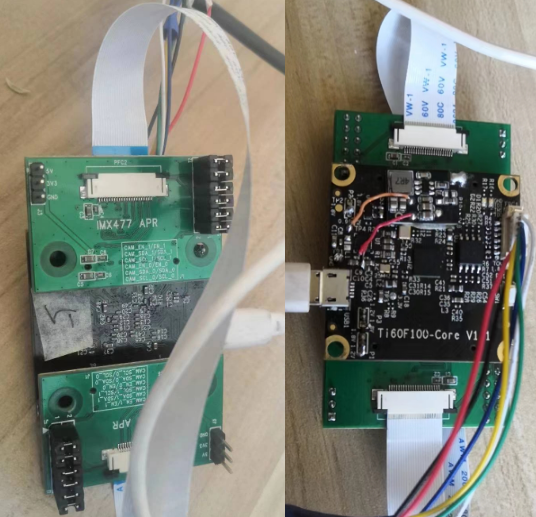

硬件平台 :易灵思的IMX477子卡加上代理商中印云端(全称:中印云端(深圳)科技有限公司)制作的Ti60F100核心板。

二、获取并掌握MIPI传输评估工具

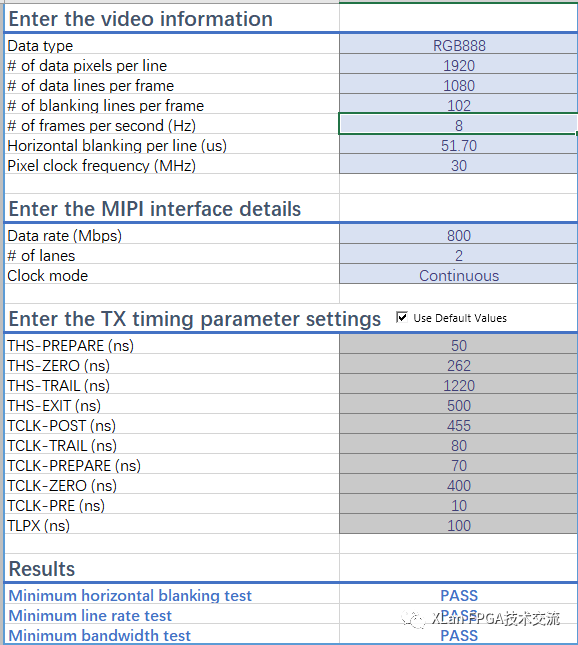

(1)获取易灵思提供的钛金系列FPGA-mipi-utility.xlsm文件,在文件内进行设置。

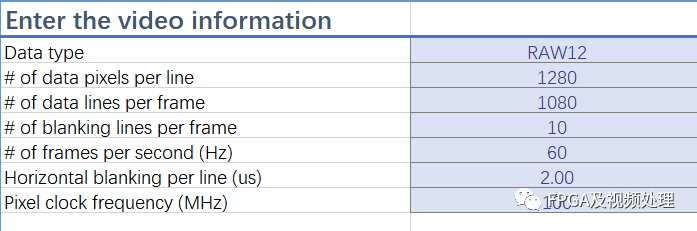

首先在Enter the video information中输入要传输的视频信息。要说明的是Pixel clock frequency对应IP核64位接口位宽的时钟,并不对应每个像素的时钟。另外Horizontal blanking per line(us)是指Thfp + Thbp + Thsa和,

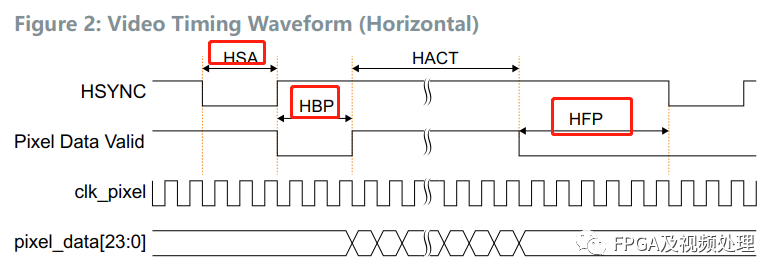

另外要求HSA,HBP和HFP的值都不能是0。因为要留给MIPI包中PH(Packet Head,32Bit)和PF(Packet Footer,16Bit)传输时间。

这是在传输过程确保能否正确传输的条件。

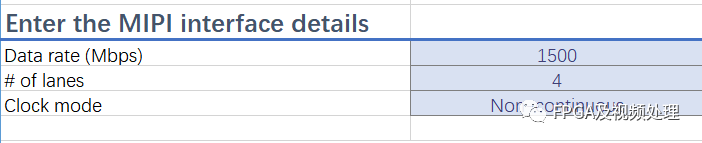

在Enter the MIPI interface details输入MIPI接口的参数

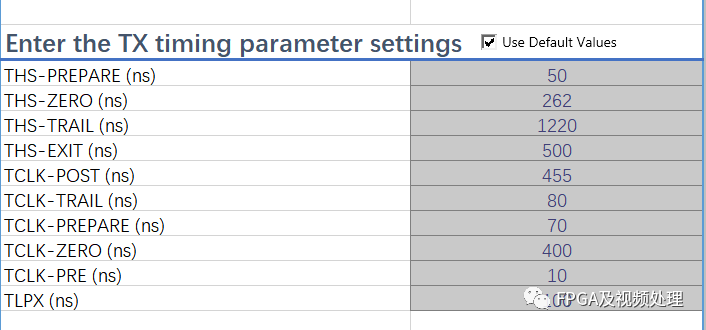

在Enter the TX timing parameter settings栏可以勾掉use default values根据接收端的参数来设置。

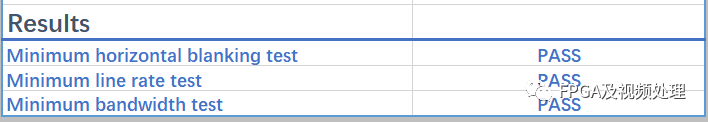

当参数都输入完成之后,在Results中提示PASS说明参数输入正确,否则会有错误提示,需要根据错误提示来修改参数。

三、硬件准备

(1)修改硬件电压。

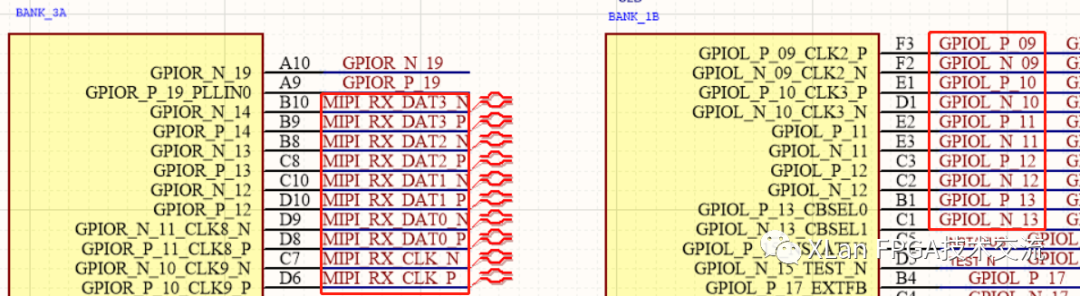

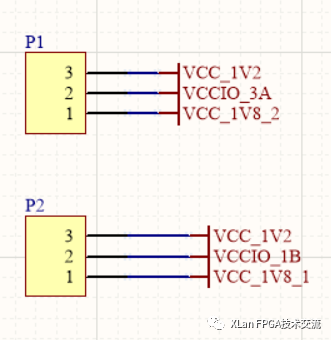

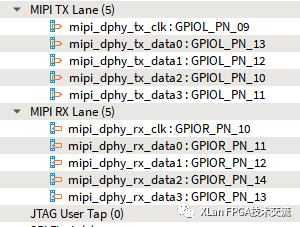

MIPI自环测试先要把MIPI IO所在的bank电压调到1.2V,本demo中,我选择的是Bank_3A的IO作为输出和Bank_1B的IO作为输入。

所以要把P1和P2的电压切换到VCC_1V2

(2)生成example并分配管脚

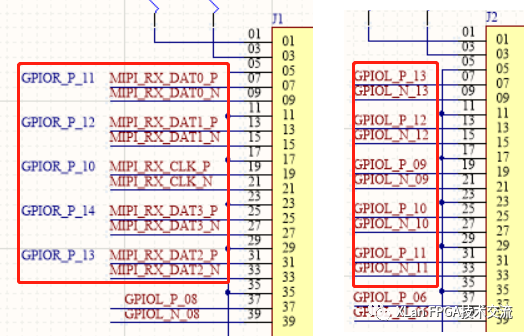

因为生成的example是对应易灵思Ti60F225 demo板的,所我们要移植到Ti60F100 demo板上。管脚分配在J1和J2的对应位置。另外要修改下对应的时钟和复位即可。

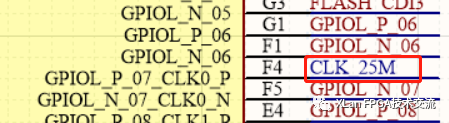

时钟分配到GPIOL_P_07。这是一个全局时钟,频率为25M,刚好与原来的demo对应。正因为是全局,所以要注意pll要选择core输入。

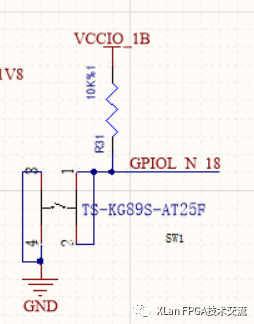

复位管脚我们分配给GPIOL_N_18

四、评估传输参数

(1)根据时钟要求计算pixel时钟支持的范围。可能自环的时候这两个时钟会有一些矛盾,但是相差不大的话,经过确认是没有问题的。另外我们也相信能够发送成功的,接收也可以。

MIPI TX要求:

PIX_CLK_MHZ <= (DATARATE_MPBS * NUM_DATA_LANE) / PACK_BIT。

MIPI RX要求:

PIX_CLK_MHZ >= (DATARATE_MPBS * NUM_DATA_LANE) / PACK_BIT

MIPI接口参数如下:

MIPI Data Lane = 2

MIPIData Rate = 800Mbps

视频格式如下:

parameter PIXEL_BIT = 24, parameter PACK_BIT = 48, parameterHSA=5,//minimumvalueispixelcntvalue,eg:RGB888-2 parameter HBP = 5, //minimum value is pixel cnt value, eg: RGB888 - 2 parameter HFP = 1024, parameterHACT_CNT =1920,//h_total=2945 parameter VSA = 1, parameter VBP = 1, parameter VFP = 100, parameter VACT_CNT = 1080, // v_total = 1182 3,480,990 parameter HS_BYTECLK_MHZ = 100, parameter DATATYPE = 6'h24 //24 - RGB888

按照上面的公式计算像素时钟。

DATARATE_MPBS = 800 NUM_DATA_LANE = 2 PACK_BIT = 48 PIX_CLK_MHZ<= 800 * 2/ 48 = 33.33 //像素时钟频率

是这样就行了吗?当然不是,还要确认修改成两个lane之后原来的数据带宽是否还能传输呢?要用评估工具进行评估保证PASS。

这里Horizontal blankingper line(us) =(5+5+1024)*(1000/66)ns = 15.51us

demo上我们选择30M.要计算视频带宽是否能传输,即要考虑公式也要考虑utility表。OK ,PASS.

===================================

五、MIPI 自环测试

===================================

连续时钟方案

(1)配置参数

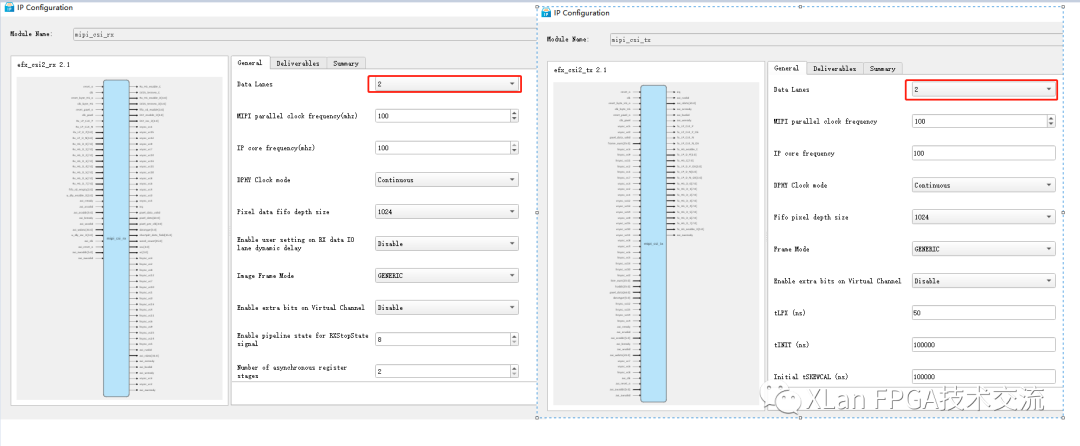

首先我们想要测试的是两个lane的自环,所以要先在IP核把data lane修改成2。

(2)修改传输时钟频率。

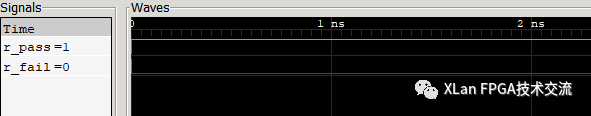

(3)上板调试

这一步到了测试环节。首先添加debug,观察r_fail和r_pass信号。上板之后我们检测r_pass和r_fail信号,如果r_pass为高,说明测试通。

assign led[1] = r_fail; assign led[2] = r_pass;

不连续时钟方案

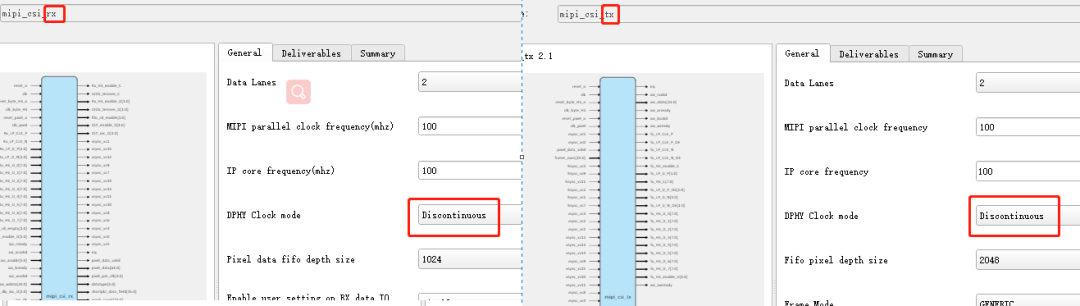

在生成IP时选择时钟不连续

demo中第一帧帧头解析错误,所以会出现不能pass的提示,但实际后面的帧都解析出来了。所以经过分析传输正常。

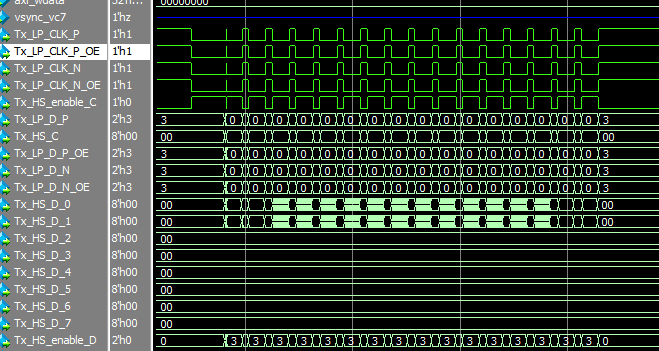

下面直观感受下什么是连续和不连续。

不连续发送的波形,可以看到很多LP_CLK_OE上拉

连续时则没有。

六、问题分析

(1)如果是不连续的话由于时钟是不连续的,所以通过逻辑分析仪抓取数据会出现明显的错误,这个是可以理解的。那要怎么分析数据,这里有个歪点子,因为是自环,所以发送时钟与接收时钟是同尖的。所以用发送时钟去抓取接收数据,事实证明很好用。就算相位有偏差也问题不大。

(2)另一个问题是,如果出现了没有pass的情况,应该怎样去定位问题?

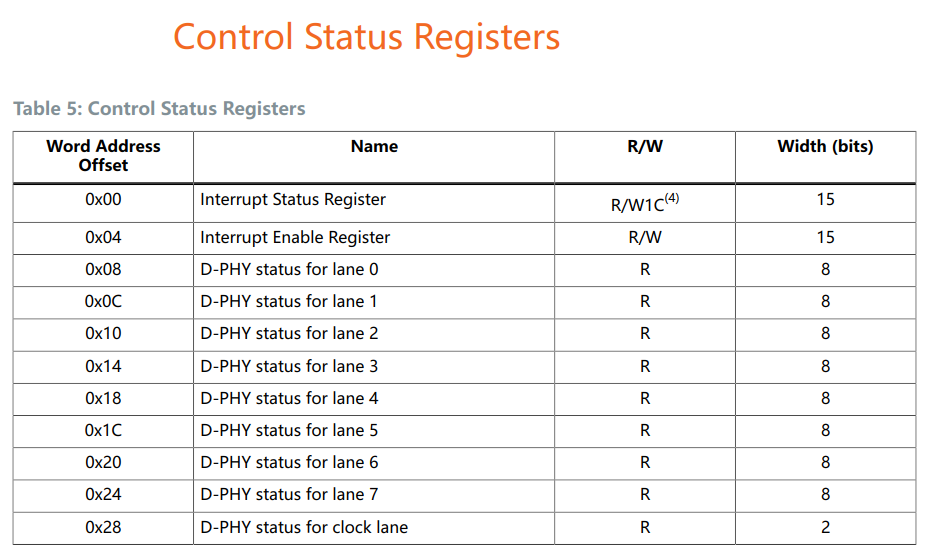

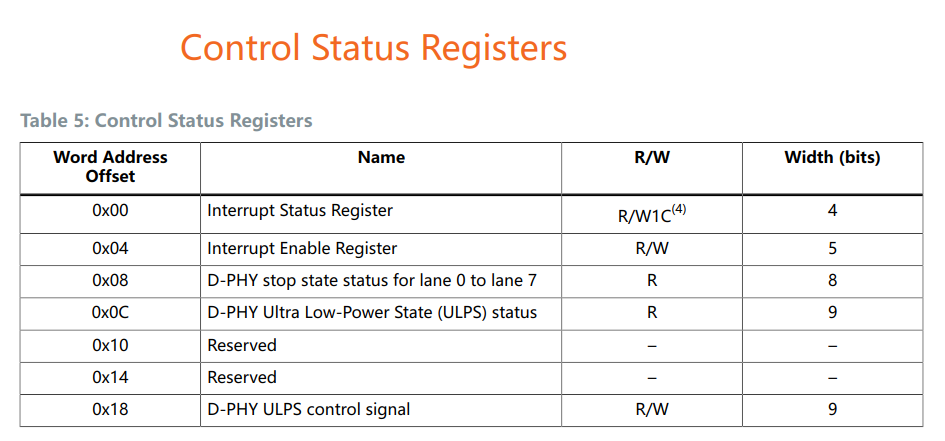

检查控制寄存器。通过读取寄存器的值可以大致判断数据出错的方向。

MIPI RX控制寄存器

MIPI TX控制寄存器

如果还是不能正确接收数据的话,易灵思还会有一些别的方式可以帮助解析数据包。

审核编辑:汤梓红

-

调试

+关注

关注

7文章

653浏览量

35881 -

MIPI

+关注

关注

11文章

364浏览量

51101 -

CSI

+关注

关注

1文章

38浏览量

51714 -

核心板

+关注

关注

6文章

1422浏览量

32139 -

易灵思

+关注

关注

6文章

66浏览量

5591

原文标题:易灵思MIPI CSI 自环调试步骤

文章出处:【微信号:gh_ea2445df5d2a,微信公众号:FPGA及视频处理】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MIPI2.5G DPHY CSI2DSI demo移植 -v1

MIPI-CSI像素时钟限制是否与CSI块限制相同?

基于赛灵思FPGA的低成本MIPI接口IP

易灵思推Trion Titanium FPGA,采用 “Quantum™ 计算架构”

MIPI CSI-2 RX Subsystem IP介绍和PHY实现浅谈

易灵思Ti60F100驱动LCD屏案例

易灵思FPGA产品的主要特点

易灵思MIPI CSI自环调试步骤

易灵思MIPI CSI自环调试步骤

评论