项目涉及5片FPGA之间的多机通信,1片主FPGA,4片从FPGA,5片FPGA采用星形连接的拓扑结构。4个从机与主机之间通信接口采用基于LVDS_33的差分IO接口标准,以满足高速率,抗干扰,chip-to-chip的数据流传输架构。各从机与主机通信时,采用全双工传输通信模式,收发双方信号线包括时钟信号tx_clk+,tx_clk-,rx_clk +,rx_clk-,差分数据信号tx_data+,tx_data -,rx_data +,rx_data -,共计4组差分通信链路。由于从主FPGA待传输的数据流通常不是单比特流,常见的数据流位宽为8bits或16bits,此时有以下两种通信方案。

方法1:采用基于源同步的1路差分时钟信号线和8路并行数据信号线来传输8bits位宽的数据流从理论上是可行的。该方法不足之处为:(1)当对数据流传输带宽提出更高要求时,即要求时钟信号速率更快以满足高速通信时,就可能对出现8路并行信号线之间相位不同步的问题;(2)需要消耗的FPGA管脚资源更多,布线要求也更高。

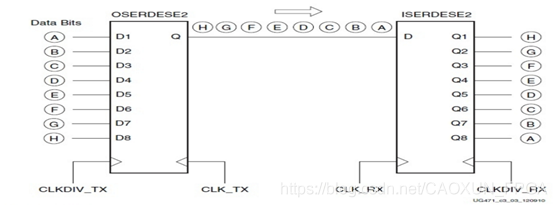

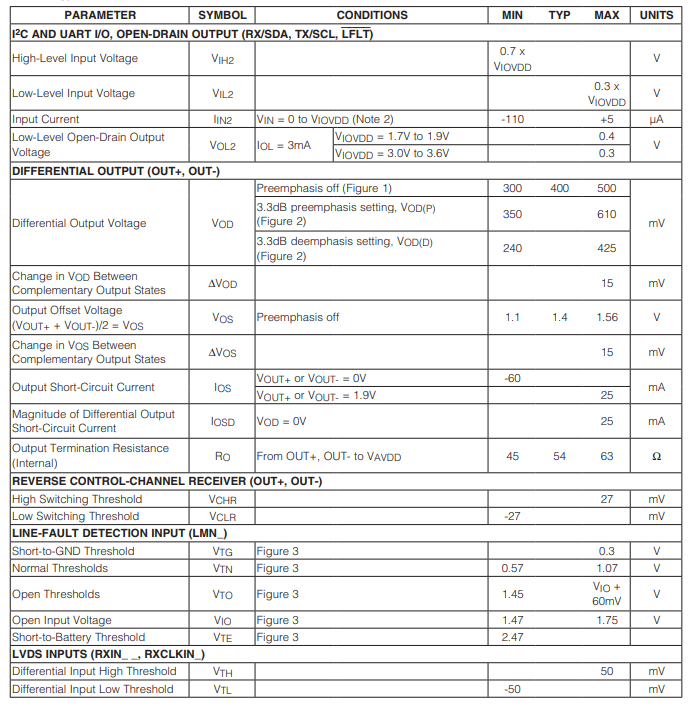

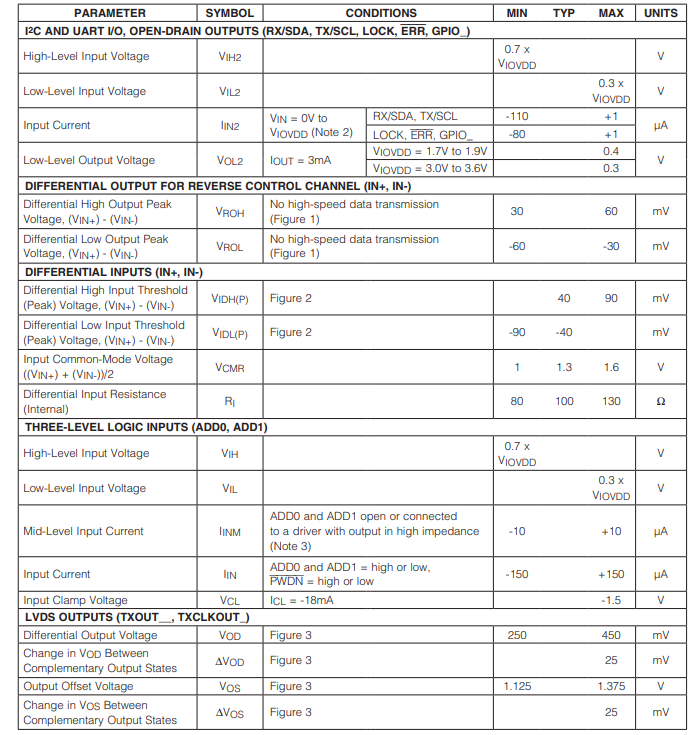

方法2:将并行数据转换为串行数据进行传输,然后串行数据在接收端整合为之前发送的并行数据。即在发送端,将8bits的数据流通过OSERDES单元转换为串行数据流bit0,bit1,... ,bit7,通过1路差分信号线输出给接收端;同理,接收端采用相反的传输原理,ISERDES单元将串行数据流bit0,bit1,... ,bit7通过8个移位寄存器缓存后整合为8位宽的数据流,完成串并转换。基于LVDS的差分IO接口支持的传输速率高达1.9Gb/s,故满足常用的高速串行数据通信。

1 设计过程

项目使用的芯片型号为Spartan6的xc6slx16-csg324,待传输的数据流位宽为8位,故IOSERDES的串并因子为8:1,FPGA的IOB集成了IOSERDES软核,故可以直接调用和自定义即可完成对ISERDES、OSERDES两个IP核的配置。

关于对ISERDES、OSERDES的相关配置可参考以下三个个用户手册。

UG382 — Spartan6 FPGA Clock Source;

UG381 — Spartan6 FPGA SelectIO Source;

XAPP1064 — source synchronize serialization and deserialization。

项目中使用的OSERDES配置参数如下图所示。

2 设计关键点

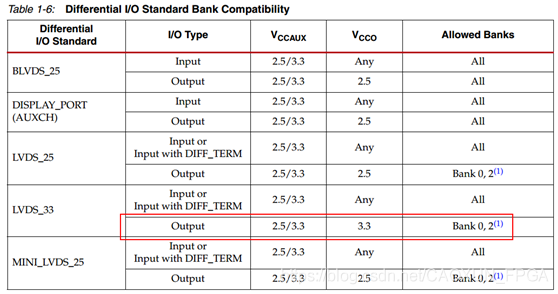

(1)Spartan6 FPGA芯片仅bank0和bank2支持OSERDES,其他bank不支持;对于ISERDES,所有bank均支持。如果忽略OSERDES对bank的限制,很容易造成在设计原理图时,出现LVDS的IO接口管脚分配问题。

(2)OSERDES数据流输出时钟信号tx_clk的构建。数据流输出时钟信号tx_clk分为两种,分别基于BUFIO2和基于PLL来实现,详见下文。

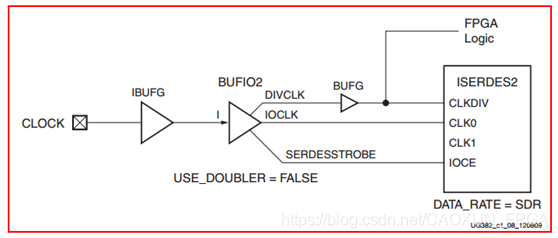

a)基于BUFIO2的SDR时钟信号

由于上图可知,将图中ISERDES用OSERDES等价替换即可。BUFIO2的IOCLK为数据流发送时钟,CLKDIV为FPGA内部控制并行数据输送给OSERDES的逻辑时钟,二者对应关系为:IOCLK = DIVCLK * DataWidth。例如,现在数据位宽为8,要求OSERDES串行通信速率为400Mbps,则IOCLK 为400MHz,DIVCLK经过BUFIO2以8分频后为50MHz,则外部晶振输入时钟CLOCK频率也为400MHz。该方法优缺点如下。

优点:数据流输出时钟信号构造简单,无需PLL倍频等;

不足:对外部晶振要求过高,例如要求400M甚至更高频率的外部晶振是不太实际的,故需要借助PLL/DCM时钟单元来实现。

b)基于PLL和BUFPLL的SDR时钟信号

由上图可知,方法二增加了PLL和BUFPLL时钟单元,CLKDIV和IOCLK时钟构建依据上图即可完成,注意点是PLL_BASE的CLKOUT0输出没有BUFG做缓冲。例如,同样要求OSERDES串行通信速率为400Mbps,外部晶振CLOCK可以为50MHz,通过PLL倍频,CLKOUT0(8倍频)输出为400MHz,用于IOCLK时钟,CLKOUT2直接作为CLKDIV时钟源,即可满足要求。

优点:外部晶振频率要求低,且通过PLL倍频操作,IOCLK方便工作于更高频率;

不足:需要借助PLL/DCM时钟单元来实现。

(3)ISERDES数据流输入对BITSLIP信号的控制。

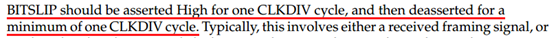

在ISERDES数据流接收端,提供一个Bitslip信号用于将接收到的数据流进行位对齐。例如发送端发送的数据TX_Data为8'b0110_0010,接收端初始接收到的数据为RX_Data为8'b0011_0001,通过使能Bitslip信号(Bitslip上升沿跳变有效)一次,接收端数据流向左移动一位,RX_Data则由8'b0011_0001变为8'b0110_0010,实现了接收端数据对齐操作。由于发送端和接收端相位关系未知,通常情况下,Bitslip需要使能有效的次数也不确定,但移位操作次数不会超过数据的位宽,否则就是通信链路出现故障。

上图是对Bitslip信号的描述,重点关注:Bitslip信号从有效到无效最小时间间隔至少为1个CLKDIV,经过实测,项目中使用的间隔为4个CLKDIV,当使用1个CLKDIV时间间隔时,接收端数据对齐无法实现。这个细节也影响调试结果和调试进度。

此外,对于ISERDES数据流接收端,由于差分数据信号和差分时钟均有OSERDES端提供,该差分时钟rx_clk+/-频率等于数据流传输速率,故接收端可以采用基于BUFIO2对rx_clk+/-进行时钟缓冲处理,无需使用PLL等时钟单元,即可得到IOCLK和CLKDIV。

3 设计难点

在整个设计中,有很多需要注意的设计要点,前文其实已有所提及。例如OSERDES仅支持bank0和bank2;IOSERDES的IOCLK和CLKDIV的时钟构建和合理选择;Bitslip数据流对齐控制信号的操作细节。这些都会影响设计和调试结果。除此之外,遇到过的一个最头疼的设计难点如下。

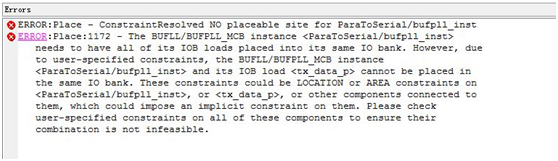

Bufpll mapping error:Constrain Resolved NO placeable site for bufpll。

为避免错误,项目中所有差分时钟信号和数据信号管脚均分配在bank2。当对OSERDES的IOCLK和CLKDIV的时钟信号构建完毕后(外部晶振输入管脚为V10,位于bank2,频率为50MHz),进行Implement Design步骤,但是编译结果出现错误提示:Constrain Resolved NO placeable site for bufpll。

由图示错误提示可知,BUFPLL这个instance也需要设置为bank2,才能将BUFPLL和IOB的其他parts,如oserdes放置在同一个bank中,故需要对BUFPLL进行位置限制。

该FPGA芯片位于bank2的BUFPLL有两个:BUFPLL_X1Y0,BUFPLL_X1Y1,对应的PLL_ADV也有两个PLL_ADV_X0Y0,PLL_ADV_X0Y1,因为BUFPLL是用于PLL的CLKOUTx输出缓冲的。

故在ucf添加约束如下:

INST ParaToSerial/bufpll_inst LOC = BUFPLL_X1Y0;

INST clk_struc/pll_base_inst LOC = PLL_ADV_X0Y0;

本项目中单独对BUFPLL进行位置约束还不能解决问题,于是又进一步对pll_base该instance进行相同的位置约束。此外,发现一个疑点,将约束改为

INST ParaToSerial/bufpll_inst LOC = BUFPLL_X1Y0;

INST clk_struc/pll_base_inst LOC = PLL_ADV_X0Y1;(此处更改)

则implement编译时依旧还是会出现相同错误,这个原因我现在也解释不了,欢迎知道的网友热心指导,谢谢!!!

备注:能顺利解决上述bufpll mapping error,得到了下面博文的启发,在此非常感谢该网友的思路分享。

4 设计结果

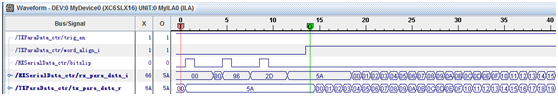

项目对基于LVDS差分接口的IOSERDES高速串行数据通信进行了收发测试。数据流传输速率为625Mbps,测试码采用FPGA发送端内部产生的0~255的递增序列,数据流同步码或前导码为0x5a,待发送的并行数据位宽为8位。测试结果见下图所示。

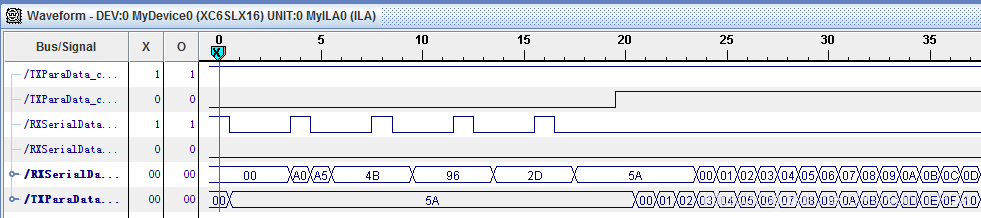

由上图可知,发送端和接收端经过3次Bitslip完成数据流的位对齐操作,当数据对齐之后,发送端开始输出0~255的测试递增序列,接收端经过4个时钟延迟后,正确的接收到数据流。

此外,为什么接收端与发送端数据流传输间隔为4个时钟,而不是其他? 原因为项目配置ISERDES工作模式为retimed,接收端要经过4级流水线缓冲器后,才将数据接收到的数据输送给FPGA内部逻辑,故有4个时钟的延迟。如果采用NETWORKING_PIPELINED Mode,则只经过3级流水线寄存器,故只有3个时钟延迟,测试结果见下图。

补充说明:

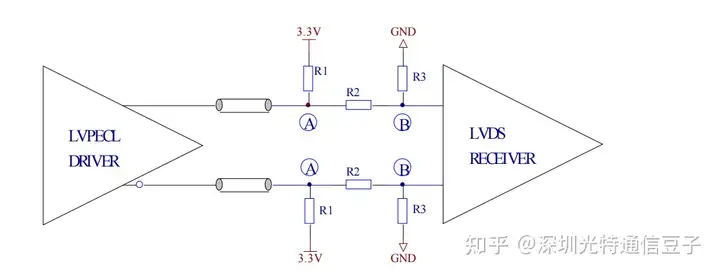

(1)LVDS信号输入端需要进行阻抗匹配,阻值通常为100Ω;该匹配电阻可以外接或者开启FPGA内部片上输入电阻,属性设置为DIFF_TERM = "TRUE";

(2)硬件设计时,差分信号线走等长线,设置该走线阻抗为50Ω;可以在差分信号线两侧采用平行GND走线进行屏蔽,减少差分信号线受到的干扰。

(3)基于该LVDS差分IO接口的高速串行通信尚未考虑对传输数据流进行数据编码,如8b10b编码。采用不同的编码方式可以应用于不同的场合,且可以提高通信链路的稳定性。

精彩推荐 至芯科技12年不忘初心、再度起航12月17日北京中心FPGA工程师就业班开课、线上线下多维教学、欢迎咨询! 锁存器、触发器、寄存器的关联与区别及其相应的verilog描述 FPGA学习-FIFO深度H的计算

原文标题:基于LVDS差分接口之IOSERDES的高速串行通信

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1655文章

22287浏览量

630300

原文标题:基于LVDS差分接口之IOSERDES的高速串行通信

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【新品】ZYNALOG徴格半导体推出ZGN4XXX系列LVDS/M-LVDS高速接口芯片

SN65LVDS33和SN65LVDS34高速差分接收器数据手册

嵌入式接口通识知识之LVDS接口

嵌入式接口通识知识之MIPI接口

差分输出 × 超低抖动:打造高速稳定的大型数据同步时脉

【高云GW5AT-LV60 开发套件试用体验】 LVDS屏显示和camera

从SerDes到SoC,全场景适配的FCom差分晶振设计全解

MAX9249多媒体串行链路串行器,带有LVDS系统接口技术手册

MAX9268多媒体串行链路解串器,具有LVDS系统接口技术手册

可编程差分振荡器:0.6ps低抖动,满足高速通信与快速交付需求

基于LVDS差分接口之IOSERDES的高速串行通信

基于LVDS差分接口之IOSERDES的高速串行通信

评论