5G与BAW

BAW振荡器VS石英振荡器

小结

原文标题:基于BAW技术的时钟解决海量数据下的精准时钟需求

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电子发烧友网

+关注

关注

1013文章

544浏览量

167483

原文标题:基于BAW技术的时钟解决海量数据下的精准时钟需求

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

TCXO:精准时钟信号背后的“中国芯跳”

的5G基站正处理着海量数据,确保视频通话流畅无阻;工厂里的自动化设备正在精密运转,分毫不差地执行每个指令……这些看似平常的场景背后,都依赖一颗不到米粒大小的核心元

LMK3H2104超低抖动时钟发生器

,满足以太网控制器和PCIe交换芯片的时钟需求。l 低抖动特性优化信号完整性,提升网络吞吐量和延迟性能。硬件加速与AI计算l 为FPGA、ASIC等加速芯片提供精准时钟,支持高带宽内存(HBM)和高速

发表于 01-14 09:29

LMK3H0102 参考无源2差分或5单端输出PCIe Gen 1-7兼容可编程BAW时钟发生器总结

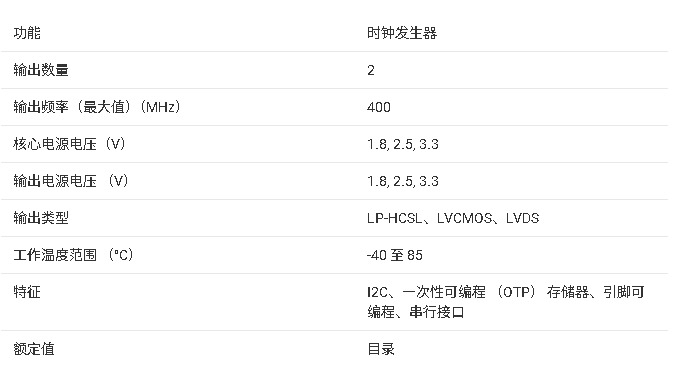

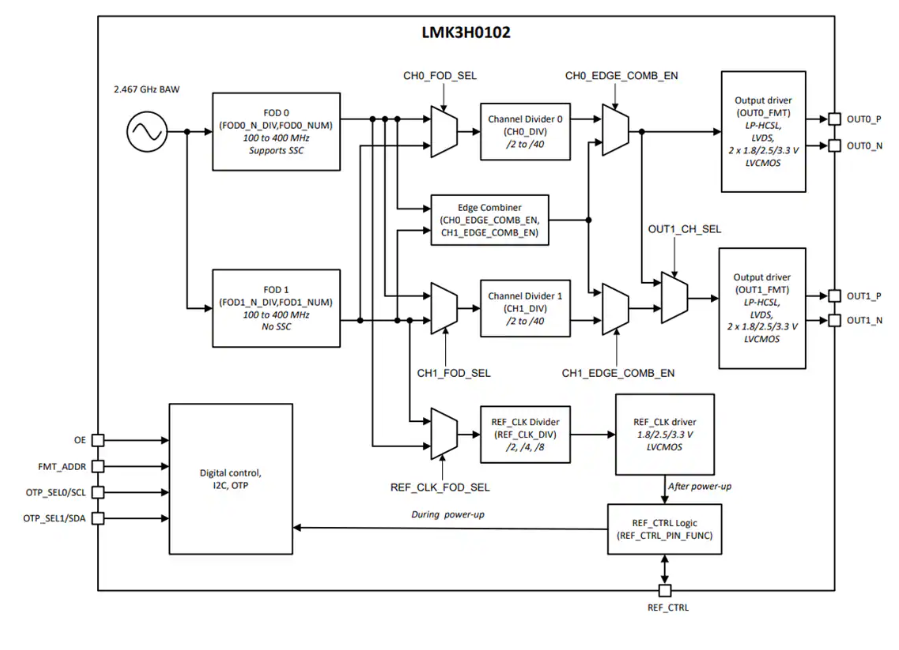

该LMK3H0102是一款 2 输出 PCIe Gen 1 至 Gen 7 兼容无基准时钟发生器,支持扩频时钟 (SSC)。该器件基于 TI 专有的体声波 (BAW) 技术,提供 ±2

LMK3C0105 参考无5-LVCMOS输出可编程BAW时钟发生器技术文档总结

LMK3C0105是一款支持 SSC 的 5 输出无基准时钟发生器。该器件基于 TI 专有的体声波 (BAW) 技术,提供 ±25ppm 时钟输出,无需任何晶体或外部

LMK3C0105-Q1 参考无源5路LVCMOS输出可编程BAW时钟发生器技术文档总结

LMK3C0105-Q1 是一款支持 SSC 的 5 输出无基准时钟发生器。该器件基于 TI 专有的体声波 (BAW) 技术,提供 ±25ppm 时钟输出,无需任何晶体或外部

LMK3H0102-Q1 参考无晶体时钟发生器技术文档总结

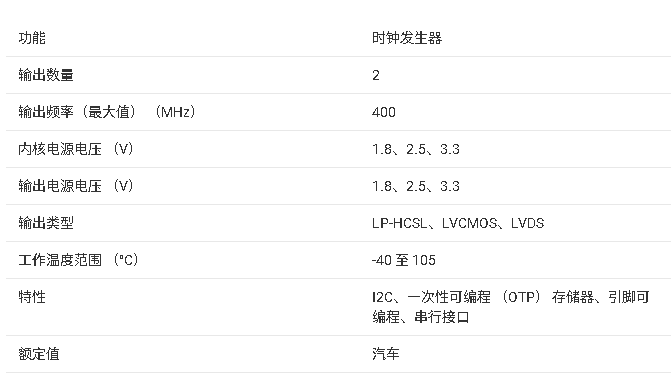

LMK3H0102-Q1 是一款符合 PCIe Gen 1 至 Gen 7 标准的 2 输出无基准时钟发生器,支持扩频时钟 (SSC)。该器件基于 TI 专有的体声波 (BAW) 技术

精准时钟,驱动未来 ----澜起科技发布多款高性能时钟芯片

,将为人工智能、高速通信、工业控制等关键领域提供精准、可靠的时钟信号支撑。 澜起科技高性能时钟芯片 作为电子系统的"心脏",时钟芯片产生的脉冲信号是系统运行的基石,其信号质量直接决定了

Texas Instruments LMK3H0102无基准时钟发生器数据手册

(BAW) 技术,提供 ±25ppm时钟输出,无需任何晶体或外部时钟基准。这些器件可同时提供两个SSC时钟、两个非SSC

德州仪器BAW时钟如何重新定义ADAS和IVI

在向更加自主的分区架构发展的过程中,为实现软件驱动的决策,需要精确的定时和可靠的时钟电路。从高级驾驶辅助系统 (ADAS) 到车载信息娱乐系统 (IVI) 和高速数据网络,汽车制造商纷纷实施外设组件

PTP 时钟:精准时钟同步的核心力量

在当今数字化时代,时钟同步对于众多领域的高效、稳定运行至关重要。无论是工业自动化生产线的协同运作,还是汽车电子系统中各个部件的精准配合,都离不开高精度的时钟同步技术。西安同步电子科技有

PTP 时钟:精准时钟同步的核心力量

在当今数字化时代,时钟同步对于众多领域的高效、稳定运行至关重要。无论是工业自动化生产线的协同运作,还是汽车电子系统中各个部件的精准配合,都离不开高精度的时钟同步技术。西安同步电子科技有

基于BAW技术的时钟解决海量数据下的精准时钟需求

基于BAW技术的时钟解决海量数据下的精准时钟需求

评论