实现覆盖率收敛

为什么这么难?

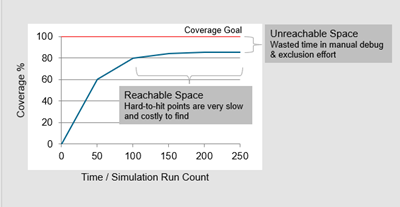

仅使用仿真来实现覆盖率收敛是很难的。仿真所用的时间和测试运行的次数与已完成覆盖率目标的百分比增长之间不呈线性关系。 如下图所示,尽管随着时间的推移,仿真运行次数不断增加,但覆盖曲线却趋于平缓。这通常归结于以下两个因素:1) 那些覆盖率目标在本质上就无法达到;2) 那些难以实现的覆盖率目标可能需要手动创建测试用例,因为受约束的随机仿真可能无法达到这些覆盖率目标。在某些情况下,运行无数的仿真测试用例并不能产生最佳投资回报率,也无法实现覆盖率收敛。

形式验证如何加速

覆盖率收敛

形式验证可通过两种方式加速仿真覆盖率收敛:

-

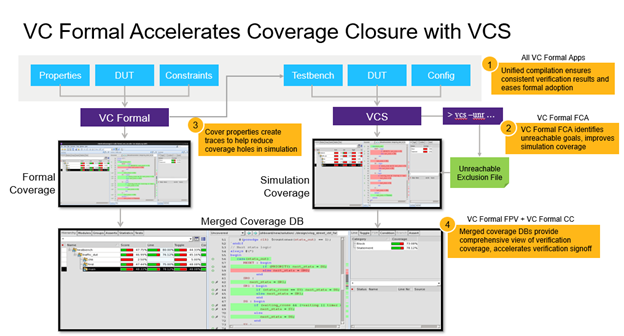

新思科技专为分析未覆盖点的可达性推出了一款VC Formal应用,即Formal Coverage Analyzer(FCA)。该应用可以生成总结性报告,指出相关覆盖率目标是否可以达到。这种分析通常称为UNR(不可达性)。如果某个覆盖率目标无法达到,可能会导致两种行为:如果设计人员在审核后确认这符合预期,则可以将相关覆盖率目标从验证计划中移除,以便提高达成的覆盖率百分比;如果这在预期之外,则通常表示这是一个设计漏洞或过约束,此时需要用户采取行动来修复设计漏洞或放宽约束。

-

形式验证发挥作用的另一种方式是覆盖属性。使用形式化技术验证断言时,工具将充分证明属性的正确性或生成反例,而覆盖属性则与此不同,其目标是让形式化工具生成一条轨迹来显示如何能达到该覆盖点。该轨迹有助于创建新的仿真测试用例,以便打到难以覆盖的覆盖率目标。

VCS+VC Formal

集成的优势

虽然仿真和形式验证之间的协同作用并不强求两种技术一定要来自同一家EDA供应商,但如果这两种解决方案拥有其他技术共性,则会有更多好处。 新思科技符合行业标准的VCS仿真器和新思科技的创新型VC Formal解决方案拥有很多有价值的联系,能够让终端用户从中获益。

-

新思科技VCS解决方案与新思科技VC Formal解决方案共享一个通用编译前端。统一的编译确保VC Formal可以轻松地应用于VCS验证环境,并确保对设计语义和意图的解释一致。

-

新思科技的VC Formal FCA应用可以在VCS shell内原生调用,以进行可达性分析来识别不可达目标,从而创建一个排除文件并反馈给VCS环境,以此提高仿真覆盖率。

-

新思科技VC Formal FPV应用中运行的覆盖属性可帮助创建更多的仿真测试用例,以覆盖随机仿真难以打到的点。

-

使用新思科技的VCS和VC Formal解决方案时,可以合并仿真和形式化覆盖率数据库。这样一来,使用一种技术验证的设计便无需使用另一种技术再次进行验证。这也大大加速了验证收敛和签核。

SoC验证时间

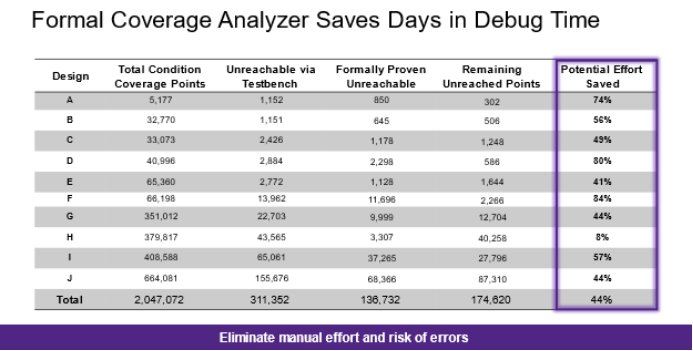

节约40%-80%

在使用新思科技的VCS和VC Formal解决方案后,很多客户发现验证时间节省了40%到80%,同时也对实现验证签核更有信心。下表显示了10种客户设计以及形式化分析在减少验证时间方面的影响。

为了帮助客户最大限度地发挥形式化技术的优势,新思科技形式验证服务团队在世界各地提供专家支持,协助开展方法培训、验证审核和各种交钥匙项目。

为了帮助客户最大限度地发挥形式化技术的优势,新思科技形式验证服务团队在世界各地提供专家支持,协助开展方法培训、验证审核和各种交钥匙项目。

总结

凭借新思科技VCS与VC Formal解决方案的强大功能,形式化技术对于证明芯片设计的正确性有很大的帮助。通过使用形式化技术来增强仿真,开发者们可以加快覆盖率收敛,从而实现更高质量的设计。新思科技的VC Formal解决方案、Verdi解决方案与VCS功能验证解决方案互相紧密集成,能够提供当今复杂SoC验证所需的速度、容量和灵活性,并帮助开发者找出设计缺陷的根本原因。 更重要的是,开发者自己并不需要成为形式化专家,而只需利用这些解决方案就能取得成效。 新思科技芯片设计和验证解决方案共享通用技术和一致的设计诠释,能够为验证开发者提供无缝的用户体验并带来更高的性能和生产力。新思科技产品“价值链”的持续创新能够帮助企业高效地设计下一代变革性产品。此外,新思科技的VC Formal解决方案还可与验证工具箱中的其他工具相互配合,助力开发者实现高质量的形式化签核。

原文标题:1+1>2:这两个工具,治好验证开发者的精神内耗

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

-

新思科技

+关注

关注

5文章

926浏览量

52652

原文标题:1+1>2:这两个工具,治好验证开发者的精神内耗

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CCLINKIE转EtherNET/IP:治好了PLC和流量计的精神内耗

元服务发布配置开发者服务信息

Sigmstar-ssd2355-助力开发者AI产品

电商API入门问答:开发者必知的10个基础问题

矽速科技正式入驻 RuyiSDK 开发者社区,共建 RISC-V 开发者生态!

Java开发者必备的效率工具——Perforce JRebel是什么?为什么很多Java开发者在用?

1+1>2:这两个工具,治好验证开发者的精神内耗

1+1>2:这两个工具,治好验证开发者的精神内耗

评论