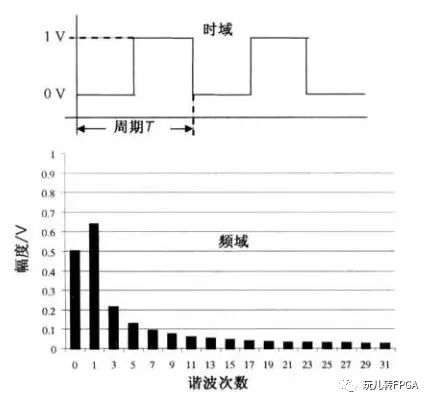

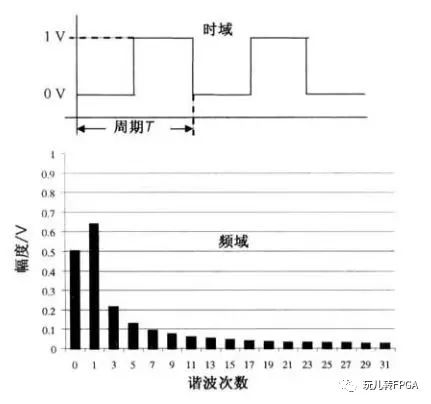

方波时域与频域

假设方波频率为f0。横轴谐波次数为0的柱状图代表直流分量的幅值,也就是方波的平均电压(与占空比有关),谐波次数为1代表频率为f0的正弦波分量的幅值,3代表,3*f0的正弦波分量幅值,以此类推。

可以看出,谐波只有奇数次的分量,1次谐波开始频率越高,幅值越低,对波形影响也就越小。

那么,此时如果此方波过一个低通滤波器,将1,3,5,7...次谐波通通滤掉会如何?

结果就会只有一个0次谐波,也就是0.5V(50%占空比)的直流分量。那么此时我们IO输出占空比变为40%,输出电压就是0.4V,占空比80%,输出就是0.8V,这不就实现了DAC的功能吗?

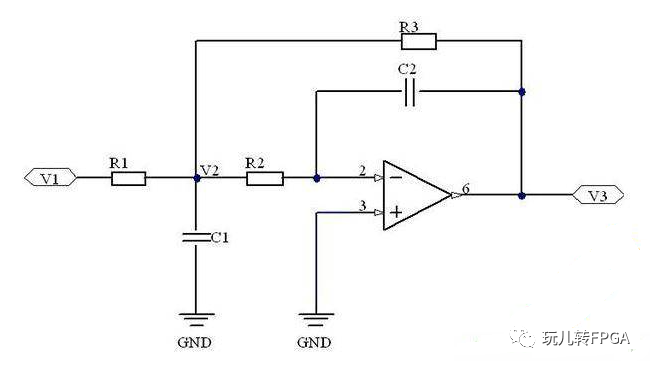

模拟滤波器

二阶有源低通滤波器

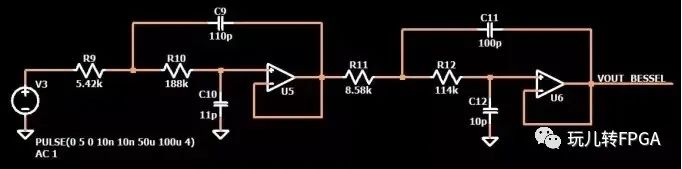

贝塞尔滤波器

除了上图的滤波器外,如果不追求精度,可以直接LC低通滤波器,简单实用,亲测有效。

Matlab分析方波频谱代码

fs=10000; %采样频率

t=0:1/fs:1;

subplot(211);

plot(t,x);

subplot(212);

pspectrum(x); %显示功率谱密度

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22513浏览量

639619 -

dac

+关注

关注

44文章

2856浏览量

197674 -

模拟滤波器

+关注

关注

0文章

33浏览量

13730 -

数字IO

+关注

关注

0文章

8浏览量

8262

原文标题:FPGA数字IO如何实现DAC功能

文章出处:【微信号:HaveFunFPGA,微信公众号:玩儿转FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

DAC3161在应用中若要使用IO TEST该怎么用?

DAC3161在应用中若要使用IO TEST该怎么用?我现在能输出正常波形,但温度变化过大后,可能会有FPGA和DAC数据接口时序不匹配问题。调整寄存器延时后又能恢复正常。所以想用

发表于 12-02 08:29

FPGA的IO

多种不同的电压标准,也有丰富的IO。首先,FPGA的IO物理命名规则,也就是我们做管脚约束时候的命名,芯片通常是长方体或者正方体,所以命名通常采用字母+数字组合的方式,从上到下是字母(

发表于 07-18 14:26

如何设计基于FPGA的多功能数字钟?

现场可编程门阵列(Field Programmable Gate Arrays,FPGA)是一种可编程使用的信号处理器件。通过改变配置信息,用户可对其功能进行定义,以满足设计需求。通过开发,FPGA能够

发表于 11-11 08:31

将Kintex 7 FPGA与CMOS输入DAC连接如何实现?

我正在尝试将Kintex 7 FPGA与CMOS输入DAC连接。我相信这意味着我需要使用标准IO引脚而不是GTX收发器。标准IO引脚上的最大频率和数据速率是多少?谢谢。

发表于 05-14 09:31

请问CPLD或者FPGA能够实现任意的IO口对联吗?

需要实现这样的功能,我有比如说10个IO从CPLD或者FPGA的左边10个管脚输入,序号为0到9,期望实现能够输出的为任意的序号,比如说我需

发表于 04-23 14:19

FPGA实现数字时钟

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进

发表于 11-29 16:51

•184次下载

基于FPGA和Quartus II的多功能数字钟设计与实现

本文以FPGA平台为基础,在QuartusⅡ开发环境下设计开发多功能数字钟。数字钟实现计时\校时\整点报时\世界时钟

发表于 12-18 11:51

•4.1w次阅读

FPGA设计中DAC控制的Verilog实现图文稿

FPGA设计中DAC控制的Verilog实现图文稿(ltspice 放置电源)-该文档为FPGA设计中DAC控制的Verilog

发表于 07-26 12:17

•10次下载

FPGA设计中DAC控制的Verilog实现

FPGA设计中DAC控制的Verilog实现(单片机电源维修)-该文档为FPGA设计中DAC控制的Verilog

发表于 07-26 12:18

•19次下载

FPGA设计中DAC控制的Verilog实现修订稿

FPGA设计中DAC控制的Verilog实现修订稿(空调电源芯片)-该文档为FPGA设计中DAC控制的Verilog

发表于 07-26 13:13

•10次下载

FPGA 结构分析 -IO 资源

工作方式; IO串并转换资源:分析IO资源如何实现串并转换。 其中第二、三系列是对第一系列中的部分内容进行更进一步的详细描述。本篇是对于第一个系列——IO资源进行部分描述,共分为几个章

基于TXS0108实现FPGA IO Bank接不同外设IO接口电压转换

引言:上一篇文章我们介绍了通过添加电阻器、场效应晶体管(FET)开关、电平转换器甚至其他Xilinx FPGA等选项实现HP Bank IO与2.5V/3.3V外设对接的方法。本文介绍利用TI公司TXS0108

请问FPGA数字IO如何实现DAC功能呢?

假设方波频率为f0。横轴谐波次数为0的柱状图代表直流分量的幅值,也就是方波的平均电压(与占空比有关),谐波次数为1代表频率为f0的正弦波分量的幅值,3代表,3*f0的正弦波分量幅值,以此类推。

发表于 06-28 14:50

•942次阅读

FPGA与传统DAC的比较

中的一种半定制电路而出现的。而DAC(Digital-to-Analog Converter)即数字-模拟转换器,是一种重要的外围设备,主要功能是将数字信号转换为模拟信号,使得

FPGA数字IO如何实现DAC功能

FPGA数字IO如何实现DAC功能

评论