01 全文速览

通过打印或者印刷二维 (2D)半导体纳米片溶液可实现低成本电子器件集成。该工作通过溴分子掺杂WSe2 晶体管,实现高性能P型二维材料薄膜晶体管,其空穴迁移率达到27 cm2 V-1 s-1,且具有~107 的高开/关比。此外,基于溶液法制备的p型WSe2 和n型MoS2的互补反相器(CMOS)展现出1280的超高增益。

02 背景介绍

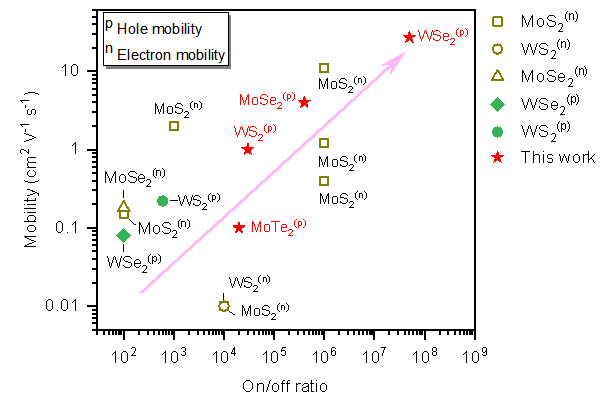

近年来,二维层状材料因其出色的电学和机械性能,在柔性和可穿戴集成器件领域引起了广泛关注。特别是,各种二维材料的单晶纳米片可以分散在溶液中,形成n型和p型的半导体油墨,进而通过高可加工性和低成本的图形印刷技术实现互补电路。溶液法制备的n型 MoS2薄膜晶体管已经实现了高电子迁移率(超过10 cm2 V-1 s-1)和开/关比(大约 106)。具有高迁移率的 P 型二维层状材料,例如黑磷,由于其低化学稳定性和低氧化势垒,不适用于溶液工艺。而化学稳定的材料,包括各种过渡金属二硫化物,其溶液法制备P型薄膜晶体管表现出低迁移率(约0.1 cm2 V-1 s-1)和较小的开/关比(102 - 105),从而限制了大规模、溶液加工的互补逻辑电路和高性能 p-n 异质结器件的发展。

不同于机械剥离或者CVD制备的单片二维晶体管,溶液法制备的二维薄膜晶体管的沟道是基于许多单个薄片组装而形成的连续的薄膜。研究发现纳米片与纳米片界面的电阻值相对纳米片内的电阻更高。此外,二维薄膜/金属处的高肖特基势垒也阻碍载流子注入,导致较高的接触电阻。因而,相对于P型单片二维材料晶体管,溶液法制备的P型二维薄膜晶体管的器件优化难度更大。

03 本文亮点

在本项工作中,我们通过掺杂Br2分子来提高溶液法制备的过渡金属硫族化合物p型晶体管的性能。

(1)Br2 掺杂的 WSe2 晶体管表现出 27 cm2 V-1 s-1 的场效应迁移率,同时具有接近零伏的阈值电压和超过 107 的电流开/关比。

(2)密度泛函理论 (DFT) 计算表明,Br2 分子可以物理吸附在WSe2表面上,覆盖率高达 》1/4,并且在最高价带附近引入浅受体态,来实现P型掺杂。

(3)Br2 掺杂可以有效降低肖特基势垒和提高半导体沟道电荷传输。

(4)此外,Br2分子掺杂的 WSe2 薄膜晶体管表现出出色的开关循环和应力测试稳定性。

(5)最后,溶液法制备的 p-WSe2 和 n-MoS2 CMOS 反相器的增益超过1200。

04 图文解析

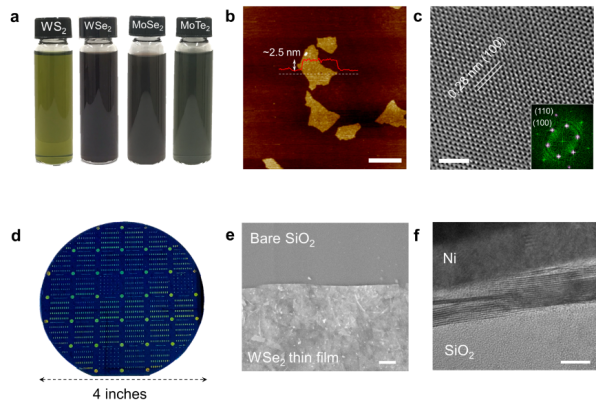

▲图1. 2D TMDs溶液和大面积图案化薄膜。

本文使用的不同过渡金属硫族化合物半导体纳米片的油墨是通过使用电化学剥离、超声、清洗、及离心过程制备。溶液法制备的WSe2 纳米片尺寸约为 800 nm,厚度约为2.5 nm。通过滴涂法,并结合光刻胶剥离工艺可以在二氧化硅、玻璃、以及PEN柔性衬底上形成致密的图形化的半导体薄膜。

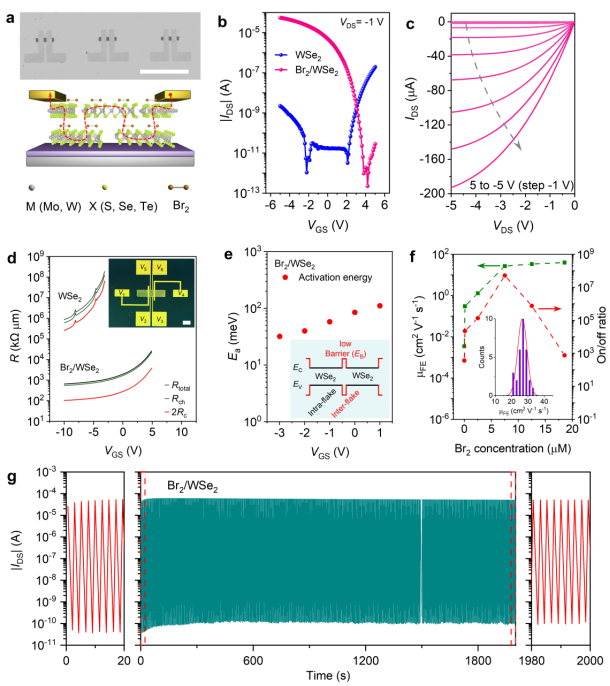

▲图 2. 溶液法制备的 WSe2 晶体管的电学特性。

未处理的WSe2 晶体管的表现出典型的n型主导的双极特性,且具有较低的空穴迁移率,约为 10-3 cm2 V-1 s-1。在尝试了各种P型掺杂分子后,我们发现Br2分子是最有效的掺杂材料。经过Br2分子处理后,实现了27 cm2 V-1 s-1 的场效应空穴迁移率,同时具有接近零伏的阈值电压和超过 107 的电流开/关比。空穴迁移率增加的主要原因有两个:第一个是由于 Br2 掺杂降低了接触电阻,第二个是由于 Br2 掺杂改善了沟道中的电荷传输界面处的电阻。同时,我们发现针对二维薄膜晶体管选择掺杂剂时,掺杂材料的分子大小也至关重要。此外,Br2分子处理过的P型WSe2晶体管也表现出较好的快速开关、连续测试及应力测试稳定性。

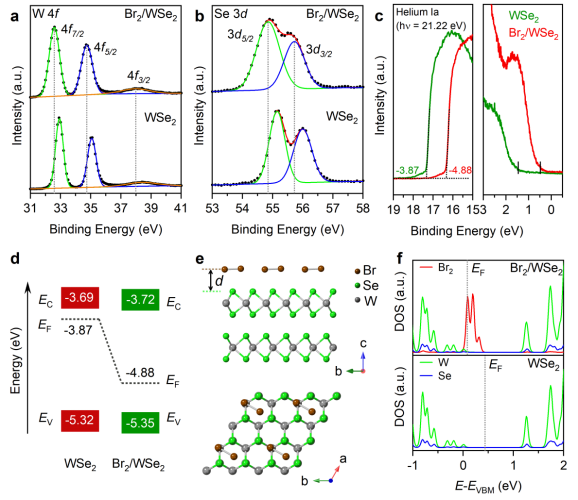

▲图 3. 光电子能谱和 DFT 计算结果。

通过XPS和UPS光电子能谱,以及DFT计算,我们也分析了Br2分子P型掺杂的机理。XPS结果显示在 Br2 处理后,W4f 和 Se3d 的结合能下移了约0.30 eV。UPS结果也显示费米能级从-3.87 eV向下移动到-4.88 eV。通过DFT计算,我们比较了WSe2和 Br2/WSe2 前后电子结构。我们发现在Br2分子吸附在WSe2表面后,最高价带附近可以引入浅受体态,从而实现P型掺杂。该浅受体态主要来源于 Br2 σp* 反键分子轨道态。

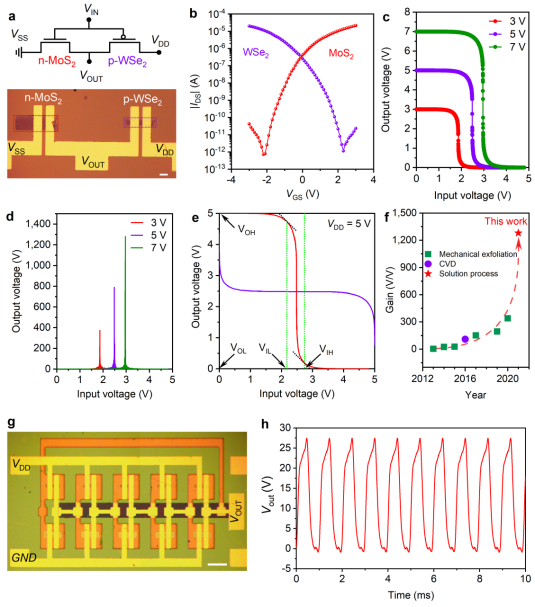

▲图 4. 溶液处理的 CMOS 反相器和环形振荡器。

最后,我们采用基于剥离的图案化方法制备了由 p-WSe2 和 n-MoS2 薄膜晶体管组成的 CMOS 反相器及环形振荡器。通过控制沟道宽度将 p-WSe2 和 n-MoS2薄膜晶体管的漏极电流调整到相同水平,从而获得高增益。结果表明在7V的驱动电压下,可以实现1280的超高增益。进一步,基于其CMOS的环形振荡器也表现出1kHz的稳定振荡频率。

05 总结与展望

总而言之,本工作通过使用卤化物分子的p型掺杂,可以实现了具有高可靠性和可重复性的高性能p型二维 WSe2 薄膜晶体管。Br2 掺杂的 WSe2 晶体管表现出出色的工作稳定性,包括快速开关、循环测试和应力测试。本工作进一步证实溶液法制备的二维材料集成器件具有优异的性能。同时,由于其低成本和易加工性,可以进一步扩展至可穿戴生物传感器和 Si CMOS 上的集成电路等应用领域。

审核编辑 :李倩

-

CMOS

+关注

关注

58文章

6236浏览量

243423 -

半导体

+关注

关注

339文章

31277浏览量

266677 -

晶体管

+关注

关注

78文章

10443浏览量

148668

原文标题:AM: 溶液法制备高性能P型WSe2薄膜晶体管及CMOS器件应用

文章出处:【微信号:Recycle-Li-Battery,微信公众号:锂电联盟会长】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

深入解析 onsemi BSS84 P 沟道增强型场效应晶体管

台阶仪在有机薄膜晶体管应用:60 nm有源层等效厚度精确测量全流程

深入解析NDS332P:P沟道逻辑电平增强型场效应晶体管

台阶仪在薄膜晶体管的应用 | 精准表征有源层厚度均匀性

MAX17112:高性能升压型DC - DC转换器的设计与应用

Diodes公司推出DXTN/P 78Q与80Q系列双极型晶体管

AM26C32:高性能差分线接收器的详细解析

IXTY2P50PA MOSFET:高性能P沟道增强型器件的深度解析

采用传输线法(TLM)探究有机薄膜晶体管的接触电阻可靠性及变异性

多值电场型电压选择晶体管结构

传输线法(TLM)优化接触电阻:实现薄膜晶体管电气性能优化

上海光机所在单层WSe2光学双稳态研究方面取得进展

下一代高速芯片晶体管解制造问题解决了!

薄膜晶体管技术架构与主流工艺路线

AM: 溶液法制备高性能P型WSe2薄膜晶体管及CMOS器件应用

AM: 溶液法制备高性能P型WSe2薄膜晶体管及CMOS器件应用

评论