相比`define的全局scope,“let” 可以只作用在局部scope。

“let”和`define一样也是定义了一个文本替换。

define是验证环境开发以及RTL开发过程中的一个非常常用的技巧,但是define是全局的,这是优点也是缺点,很容易就会对其他模块的验证环境产生干扰。

相比来说,“let” 的使用更加安全,因为“let”只会作用到局部。

module example; logic r1,r2, r3,r4,clk,clk1; let exDefLet = r1 || r2; always @ (posedge clk) begin: ablock let exDefLet = r1 & r2; r3=exDefLet; end always @ (posedge clk1) begin: bblock r4=exDefLet; end endmodule

就等价于

module example; logic r1,r2, r3,r4,clk,clk1; always @ (posedge clk) begin :ablock r3=r1 & r2; end always @ (posedge clk1) begin: bblock r4=r1 || r2 ; end endmodule

如果我们使用的是`define,而不是“let”。

module example; logic r1,r2, r3,r4,clk,clk1; `defne exDefLet r1 || r2; always @ (posedge clk) begin :ablock `defne exDefLet r1 & r2; r3=`exDefLet; end always @ (posedge clk1) begin: bblock r4=`exDefLet; end endmodule

后面的全局define会覆盖前面的define,那上面的例子就等价于

module example; logic r1,r2, r3,r4,clk,clk1; always @ (posedge clk) begin: ablock r3 = r1 & r2; end always @ (posedge clk1) begin: bblock r4 = r1 & r2; end endmodule

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

31文章

1374浏览量

114737 -

System

+关注

关注

0文章

166浏览量

38856 -

LET

+关注

关注

0文章

11浏览量

10493

原文标题:SystemVerilog中的“let”语法

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

cocotb中的基础语法与SystemVerilog中的常用语法对照总结

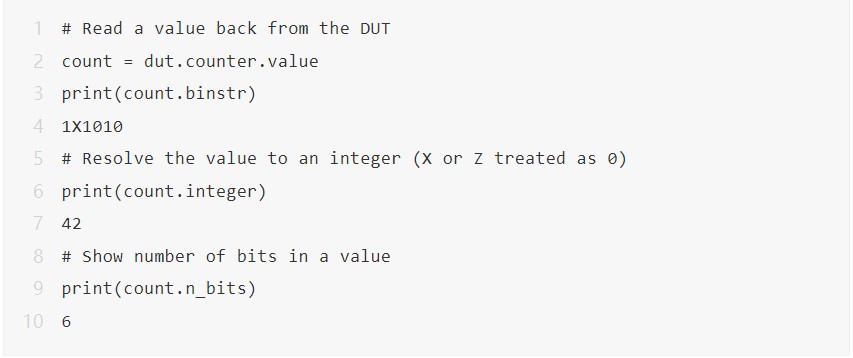

对于信号的读取,我们在SystemVerilog中,可以直接读取信号值,而在cocotb中,其为接口变量提供了value方法属性用于获取信号值。

systemverilog------Let's Go

官方的一个systemverilog详解,很详细。推荐给打算往IC方面发展的朋友。QQ群374590107欢迎有志于FPGA开发,IC设计的朋友加入一起交流。一起为中国的IC加油!!!

发表于 06-02 09:47

使用SystemVerilog来简化FPGA中接口的连接方式

开发,但现在Vivado对SystemVerilog的支持已经比较好了,完全可以使用SystemVerilog写出可综合的FPGA程序,而且FPGA开发中只会使用的SystemVerilog

发表于 01-08 17:23

刚装IC617建一个systemverilog的cell总是报语法错误怎么去解决?

如下图,先建一个systemverilog的cell,但是会报错,求帮解决下。写个最简单的也会报语法错误。

发表于 06-24 06:24

cocotb中的基础语法

cocotb的出现使得我们能够在做RTL仿真验证时依托Python来进行测试用例的构建,当我们习惯了用Verilog、SystemVerilog来构建测试用例时,切换到cocotb后最直观的方式便是我们能够建立cocotb中的基础语法

解码国产EDA数字仿真器系列之二 | 如何实现全面的SystemVerilog语法覆盖?

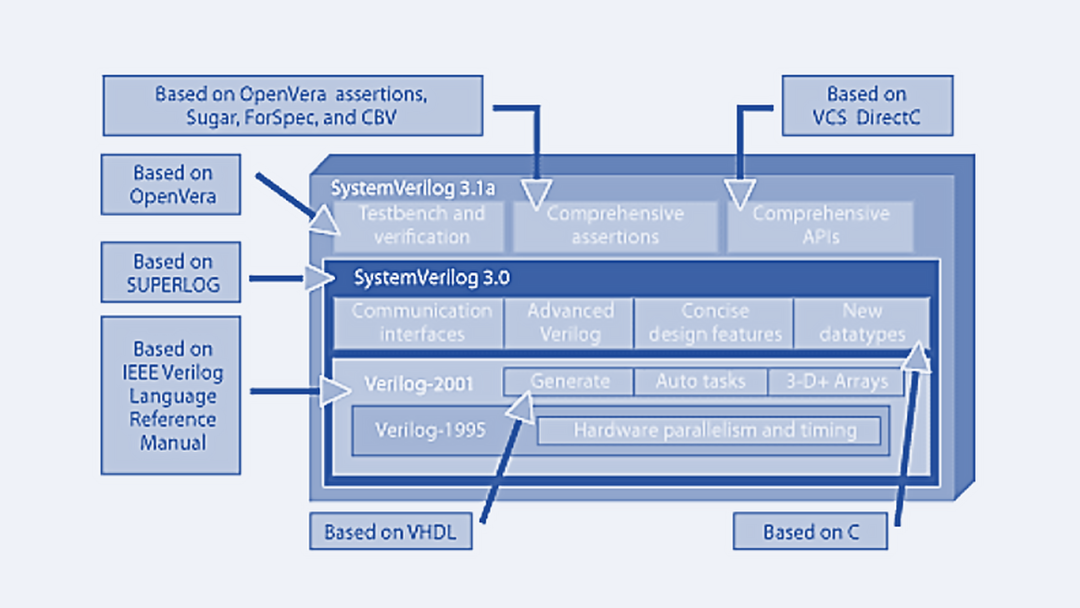

持SystemVerilog语言,是开发仿真器的一个重要任务。 SystemVerilog的发展历程 数字芯片的验证技术是随着Verilog语法的演变而演变的。 最早,Verilog是完全用来描述

发表于 04-07 14:40

•1314次阅读

如何实现全面的SystemVerilog语法覆盖

SystemVeirlog的全面支持是开发商用仿真器的第一道门槛。市面上可以找到不少基于纯Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可数。如何全面地支持SystemVerilog语言,是开发仿真器的一个重要任务。

javascript的基本语法遵循的标准

的基本语法。 变量声明与赋值 在JavaScript中,可以使用关键字 var 、 let 或 const 声明变量。其中, var 是旧版的声明方式, let 和 const 是ES

SystemVerilog中的“let”语法

SystemVerilog中的“let”语法

评论