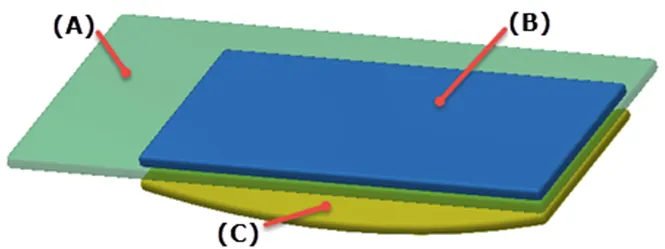

翘曲度是实测平面在空间中的弯曲程度,以翘曲量来表示,比如绝对平面的翘曲度为0。计算翘曲平面在高度方向最远的两点距离为最大翘曲变形量。

晶圆翘曲度影响着晶圆直接键合质量,翘曲度越小,表面越平整,克服弹性变形所做的工就越小,晶圆也就越容易键合。晶圆翘曲度的测量既有高精度要求,同时也有要保留其表面的光洁度要求。所以传统的百分表、塞尺一类的测量工具和测量方法都无法使用。

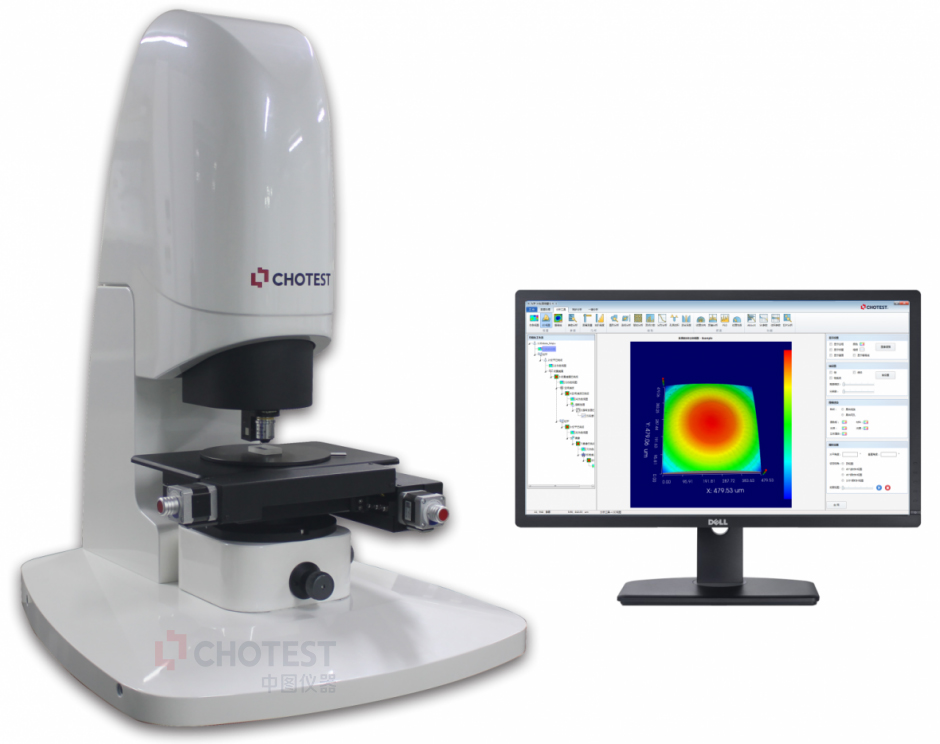

以白光干涉技术为原理的SuperViewW1光学轮廓仪,专用于超精密加工领域,其分辨率可达0.1nm。非接触高精密光学测量方式,不会划伤甚至破坏工件,不仅能进行更高精度测量,在整个测量过程还不会触碰到表面影响光洁度,能保留完整的晶圆片表面形貌。测量工序效率高,直接在屏幕上了解当前晶圆翘曲度、平面度、平整度的数据。

SuperViewW1光学3D表面轮廓仪

光学轮廓仪测量优势:

1、非接触式测量:避免物件受损。

2、三维表面测量:表面高度测量范围为1nm-10mm。

3、多重视野镜片:方便物镜的快速切换。

4、纳米级分辨率:垂直分辨率可以达到0.1nm。

5、高速数字信号处理器:实现测量仅需要几秒钟。

6、扫描仪:采用闭环控制系统。

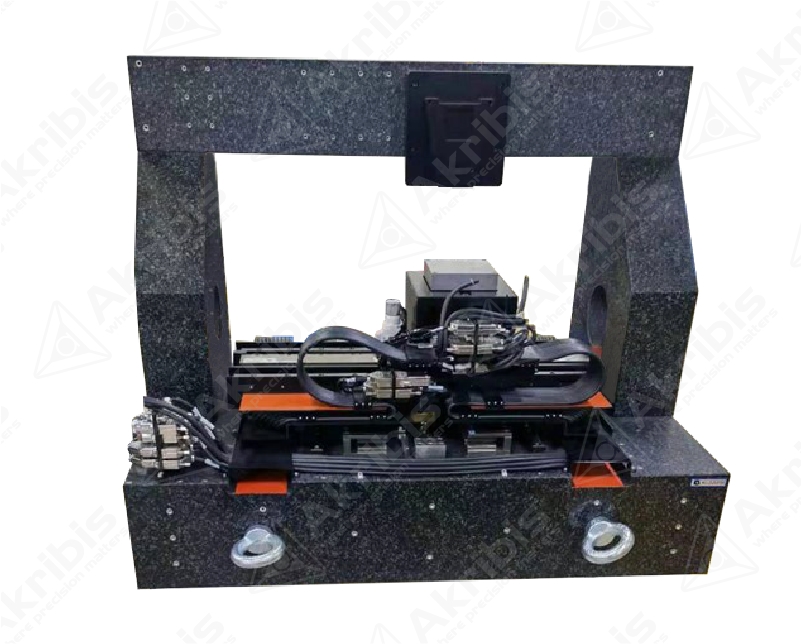

7、工作台:气动装置、抗震、抗压。

8、测量软件:基于windows操作系统的用户界面,强大而快速的运算。

审核编辑 黄昊宇

-

测试

+关注

关注

9文章

6402浏览量

131669 -

半导体

+关注

关注

339文章

31236浏览量

266484 -

晶圆

+关注

关注

53文章

5449浏览量

132749

发布评论请先 登录

适配超薄晶圆的aligner型号有哪些?能处理±1.5mm翘曲吗?

wafer晶圆厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量的设备

wafer晶圆几何形貌测量系统:厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量

wafer晶圆几何形貌测量系统:厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量

半导体晶圆翘曲度测试方法

半导体晶圆翘曲度测试方法

评论