扫描二维码获取

更多精彩

FPGA设计论坛

欢迎关注至芯科技

至芯官网:www.zxopen.com

至芯科技技术论坛:www.fpgaw.com

至芯科技淘宝网址:

https://zxopen.taobao.com

至芯科技FPGA初级课程(B站):

https://space.bilibili.com/521850676

至芯科技FPGA在线课程(腾讯课堂):

https://zxopenbj.ke.qq.com/

至芯科技-FPGA 交流群(QQ):282124839

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:SPI总线的特点、工作方式及常见错误解答

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22501浏览量

639031

原文标题:SPI总线的特点、工作方式及常见错误解答

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

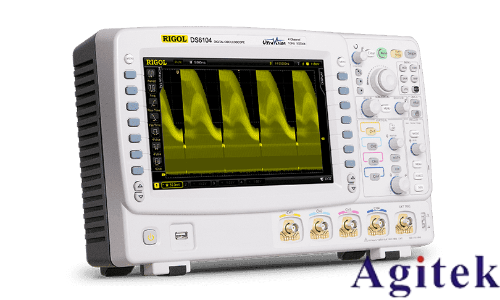

使用PicoScope示波器解码SPI总线信号

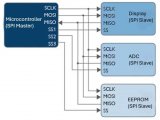

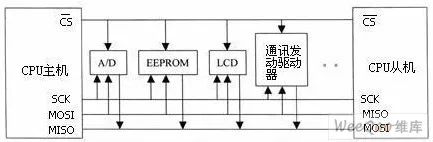

串行外设接口(SPI, Serial Peripheral Interface)总线最早由 Motorola 开发,用于其微控制器产品。由于其结构简单、实现直接,随后被其它厂商广泛采用,目前已在嵌入式系统领域的各类器件中得到普及。

示波器常见问题解答 (FAQ)

示波器是电子工程师不可或缺的“眼睛”,它能将看不见的电信号转化为可视的波形图像,帮助我们洞察电路的运行状态。为了帮助您更高效、安全地使用这一工具,我们整理了以下常见问题与解答。 1.

电缆护层保护器工作方式

电缆护层保护器是高压单芯电缆系统中的关键保护装置,其工作方式核心在于**钳制过电压并迅速恢复绝缘**,犹如一个为电缆金属护层(外屏蔽层)特设的“智能安全阀”。 其工作方式可分解如下: 1. 应对

机器学习和深度学习中需避免的 7 个常见错误与局限性

无论你是刚入门还是已经从事人工智能模型相关工作一段时间,机器学习和深度学习中都存在一些我们需要时刻关注并铭记的常见错误。如果对这些错误置之不理,日后可能会引发诸多麻烦!只要我们密切关注

EtherCAT总线节点顺序错误问题详解

,总线节点顺序错误是工程师常遇到的典型问题之一。本文将深入剖析该问题的成因、诊断方法及解决方案,并结合实际案例提供系统性指导。 一、EtherCAT总线拓扑与节点顺序原理 EtherCAT支持线型、树型

提高系统效率几个误解解析

的参数设置的,在实际应用中应结合总线工作频率和等待周期等参数进行合理调配。有时把频率降低反而可提高效率,如RAM的 存取周期是70ns,总线频率为40M时,设3个周期的存取时间,即75ns即可;若

发表于 12-15 06:09

UART、SPI、I2C 实战对比:哪个更适合你的项目?

在嵌入式开发中,设备之间的通信是绕不开的话题。常见的三种总线接口——UART、SPI、I2C——各有优缺点。不同项目需求决定了选择哪一种协议最合适。本文结合实战经验,逐项对比三者,并附带实战代码

国巨贴片电容的电压标识有哪些常见错误?

国巨贴片电容的电压标识在识别和使用过程中可能存在一些常见错误,这些错误可能源于标识本身的模糊性、不同系列产品的差异、对标识规则的误解,或使用环境的影响。以下是具体分析: 一、标识模糊或

NCS放大器DAD3350常见错误码及解决方案

NCS放大器DAD3350在工业应用中可能出现的错误码及解决方案如下: 一、常见错误码及原因 过载报警(如LV低电压报警、OVC过电流报警) 原因 : 电源电压异常(如过低或

电商API常见错误排查指南:避免集成陷阱

在电商平台开发中,API集成是连接系统、实现数据交换的核心环节。然而,许多开发者在集成过程中常遇到错误,导致项目延迟、数据丢失或用户体验下降。本文将逐步介绍常见错误类型、排查方法以及预防策略

WXZ196微机消谐装置的工作方式是什么

WXZ196微机消谐装置的工作方式是什么? 1、实时监测:微机消谐装置通过高性能的传感器,实时监测电力系统中的关键参数,尤其是PT开口三角处的电压和频率。在正常工作的情况下,PT开口三角处的电压小于

原理图和PCB设计中的常见错误

在电子设计领域,原理图和PCB设计是产品开发的基石,但设计过程中难免遇到各种问题,若不及时排查可能影响电路板的性能及可靠性,本文将列出原理图和PCB设计中的常见错误,整理成一份实用的速查清单,以供参考。

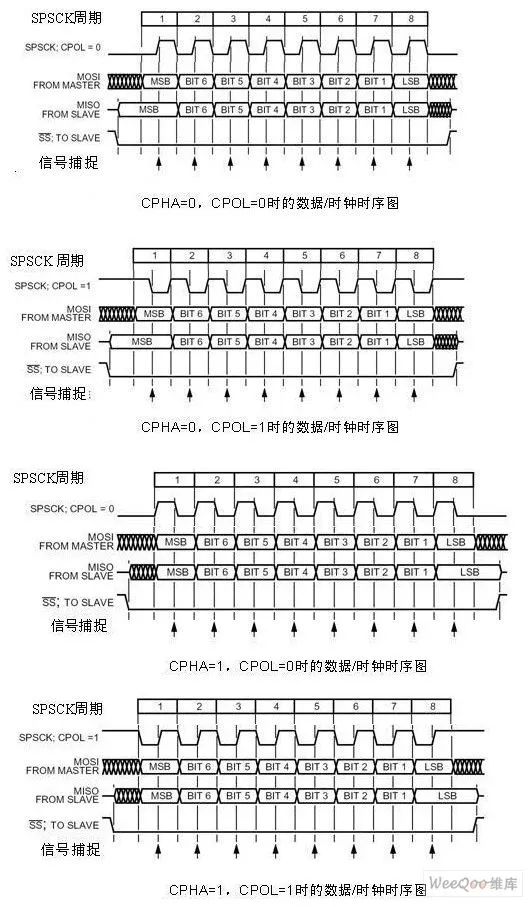

SPI总线的特点、工作方式及常见错误解答

SPI总线的特点、工作方式及常见错误解答

评论