系统级封装 (SiP) 正迅速成为越来越多应用和市场的首选封装选项,引发了围绕新材料、方法和工艺的狂热活动。

SiP是将多种功能集成到单个基板上的重要封装平台,可通过更短的互连实现更低的系统成本、设计灵活性和卓越的电气性能。SiP 出现在 5G、物联网、移动、消费者、电信和汽车应用程序中。其中,最大、或许也是最令人兴奋的细分市场是消费者和可穿戴设备——从智能耳塞到电容器疼痛贴片——纤薄、舒适的设备,可快速提供人们想要的健康和健身数据。

在许多方面,SiP 和其他类型的先进封装实现了曾经几乎完全与摩尔定律相关的性能和成本优势。“通过我们的扇出组合、倒装芯片、BGA 和嵌入式解决方案,ASE 与台积电一起努力工作,以扩展摩尔定律标准,我们希望将性能翻倍——也许不是成本的一半,但成本效益,”日月光销售和营销高级副总裁Yin Chang说。“这就是我们引入 VIP 平台以提供解决方案工具箱的原因,为架构师提供最高级别的灵活性来创建差异化系统。”

其他人同意先进封装在提高系统性能方面发挥着关键作用。“归根结底,系统级性能才是最重要的,” Lam Research旗下 Coventor总裁 David Fried 说。“我们仍在努力克服功率、性能、功率、面积和成本 (PPAC) 障碍。只要市场不断要求我们提供额外的计算能力和内存,我们只是在推动不同的参数以不断提高系统级性能。”

封装类型选择通常归结为平衡性能和成本。Yole Intelligence 的技术和市场分析师 Stefan Chitoraga 表示:“倒装芯片主导了 RF AiP 毫米波市场,但存在开发扇出 AiP(封装天线)的趋势。“与倒装芯片相比,扇出的优势包括更小的外形尺寸、利用高密度 RDL 和细间距。尽管如此,扇出仍然过于昂贵,并且需要克服技术挑战。”

这些挑战包括模具移位和翘曲,各种工具和工艺修改正在解决这些问题。

为了在单个 SiP 中实现高性能、高效率和低成本,工程师们正在将新的成型材料、双面 SiP、激光辅助键合 (LAB) 和下一代柔性基板用于扇出、倒装芯片和嵌入式 SiP。

3D的 SiP

SiP 是行业 3D 革命的一部分。除了以更精细的间距容纳更多 I/O 的趋势外,还有许多其他努力将更多内容塞进封装而不是单个芯片。这包括扇出中的多个重新分布层、桥接器和中介层以将不同的裸片连接在一起、双面封装以增加密度,以及嵌入式裸片选项以在更小的外形中实现更快的裸片到裸片处理,从而消耗更少的功率。

今天的 SiP 结合了各种组件,从 GPU 和 RF IC 到存储器、传感器、无源器件等等。“例如,ASE 的 SiP 技术支持集成不同的微控制器、ASIC、天线和传感器,从而控制连续血糖监测仪 (CGM) 中的所有功能,”ASE 企业研发副总裁 CP Hung 表示。

Hung 还描述了将四方扁平无引线 (QFN) 封装中的多个传感器重新设计为具有硅通孔的晶圆级芯片级封装 (WL-CSP),这可以提高 80% 的电气性能,同时减少其足迹减少了 30%。Hung 表示,SiP 也有生物识别应用,包括用于测试血液的微流体通道的体外诊断、基于 SiP 的助听器以及用于传感器集线器的晶圆级 SiP,其占地面积比传统封装小 77%。

SiP 还动摇了供应链和成本结构。“你每天都会在手机上看到这一点。它们变得更薄、更轻,同时执行更多功能,但这要求封装与这些设计保持同步,这意味着保持信号完整性、管理热问题、减少干扰等,” QP高级工艺工程师 Sam Sadri 说技术。“但哪里有挑战,哪里就有解决方案。使用倒装芯片时,您在进行芯片贴装时会尝试从底部散发热量,因此您在接口处使用散热器和导热硅脂。我见过带有管道和冷却液的 3D 基板。”

除了评估 SiP 中的所有流程和配置选项外,Sadri 还强调了对系统中 IP 保护的日益关注。

Yole 分析师估计,到 2025 年,SiP 市场将以 5% 的复合年增长率增长至 170 亿美元,高于 2020 年的 138 亿美元。市场领导者是 ASE、索尼、Amkor、JCET 和台积电。大约 85% 的市场是移动和消费产品,其次是电信和基础设施,然后是汽车封装。

此外,SiP I/O 间距预计将从今天的 90-350µm 收窄到 2025 年的 80-90µm。使用铜柱的嵌入式硅桥,或使用 TSV 和微凸块的硅中介层,”Chitoraga 说。

SiP 包含多种组装方法,包括倒装芯片和引线键合 SiP(收入和单位最大),其次是扇出 WLP,然后是嵌入式芯片封装。Yole Intelligence 的技术和市场分析师 Gabriela Pereira 表示:“SiP 让系统设计人员能够灵活地混合和匹配 IC 技术、优化每个功能块的性能并降低成本。”“完全集成的 SiP 解决方案使设计人员能够以最少的设计工作将蓝牙或摄像头模块等附加功能实现到系统中。”

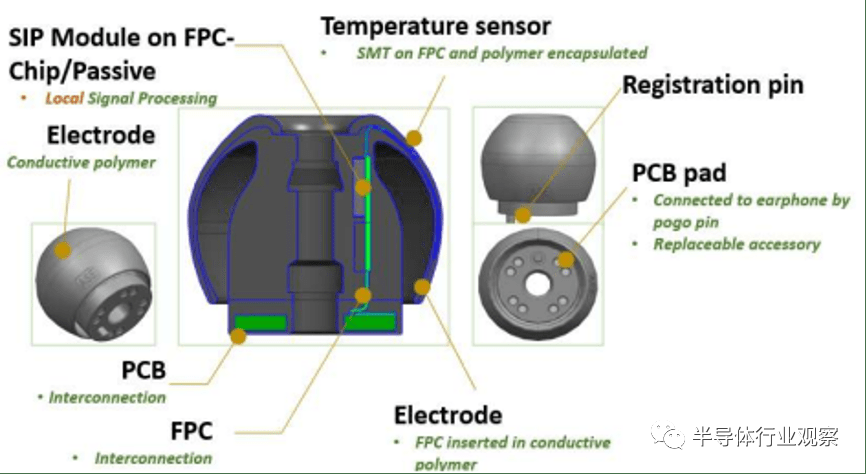

能够测量体温和拍摄心电图 (ECG) 的原型无线耳塞是 ASE 及其客户之一正在开发的可穿戴设备的最新示例(见图 2)。ASE 的 Kueihao Tseng 及其同事强调了这样一个事实,即工作电子、封装和测试框架位于耳塞外部附近,通过圆形 PCB 中的弹簧针连接。这种方法提高了信号完整性并实现了组件更换。工程师优化了成型工艺和金属聚合物材料以实现低电阻 (<0.05Ωm),同时保持柔韧性以确保舒适贴合。

图 2:柔性基板上的 3D SiP 模块将导电电极连接到温度传感器,再连接到 SiP 模块,再到智能耳塞中的圆形 PCB。

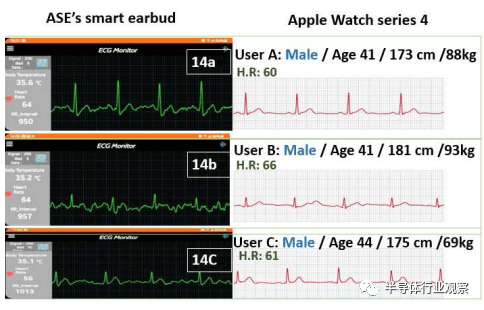

在柔性印刷电路上,信号处理 IC 和无源元件将 mV 级生物反馈信号转换为数字信号。耳塞使用热敏电阻测量温度,它比 IR LED 便宜。通过流程修改,ECG 波形能够与 Apple Watch 基准测试相匹配(见图 3)。

图 3:使用原型耳塞的心电图结果与 Apple Watch 基准相关。

不断发展的工艺

将裸片凸块连接到基板焊盘有几种主要选择。其中:

大规模回流是最成熟和最便宜的。

热压键合 (TCB) 使用力和热量,并且与低 k 电介质兼容,但它是一种较低吞吐量的工艺。

激光辅助键合 (LAB) 在比 TCB 更短的过程中提供局部加热。

“对于小芯片应用,激光辅助键合效果非常好,只要芯片尺寸不太大,”ASE 的 Chang 说。“对于更大的芯片,热压键合可在大面积上提供均匀的加热和压力。”

LAB 由 Amkor 工程师于 2014 年开发,自 2018 年以来一直用于装配线,用于倒装芯片封装。Amkor 目前正在开发下一代 LAB 技术,该技术特别针对与高性能封装中的热界面材料 (TIM) 的互连。

“最近,对细间距倒装芯片凸块和大/薄基板封装的需求增加,由于其良好的质量和高生产率,引起了业界对 LAB 的兴趣,” Amkor Technology Korea董事 SeokHo Na 表示。TIM 有助于在倒装芯片 BGA 中使用金等导电界面将热量从管芯散发到盖子。但是具有金表面的硅芯片往往会反射大部分指向它的激光,从而导致传统 LAB 的非湿式故障。

先进的 LAB 工艺将激光引导至封装背面,穿过工具的载物台真空块。工程师调整了工艺条件,包括功率和曝光时间,以使用 SnAg 尖端形成更可靠的铜柱凸块。Amkor 指出,与大规模回流焊相比,LAB 不太可能产生焊料侧壁蠕变(芯吸),并且与大规模回流焊相关,并且可以适应更精细的凸点间距。其他架构,例如 2.5D 和 3D HBM(在 EMC 中),也可能会利用 LAB。“下一代 LAB 可能是带有背面金属 (TIM) 裸片的细间距凸块器件的唯一解决方案,”Na 总结道。

嵌入式 SiP

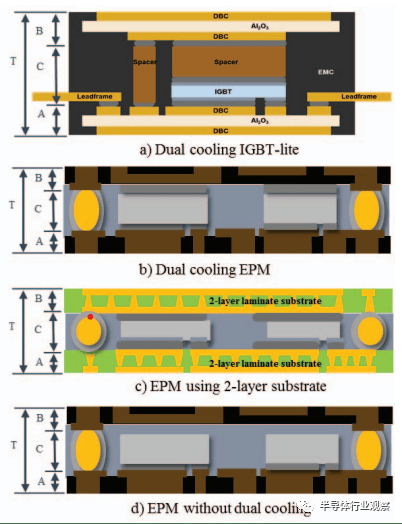

嵌入式 SiP 是一个快速发展的市场。在最近开发的 3D 嵌入式功率 SiP 中,模塑料 (EMC) 是最受关注的问题。该平台的一个特点是围绕夹在基板之间的功率 FET 的 EMC 填充工艺。EMC 必须满足杨氏模量(拉伸)和玻璃化转变温度(流动)的特定参数,以最大限度地减少封装翘曲——这在功率晶体管中尤其重要,因为它们无法获得摩尔定律缩放的好处。翘曲是使用 Ansys 的全有限元模型软件模拟的。

图 4:通过使用优化的热压结合和成型材料从层压基板切换到基于引线框架的工艺,使用单面冷却的更紧凑的嵌入式 SiP 成为可能。

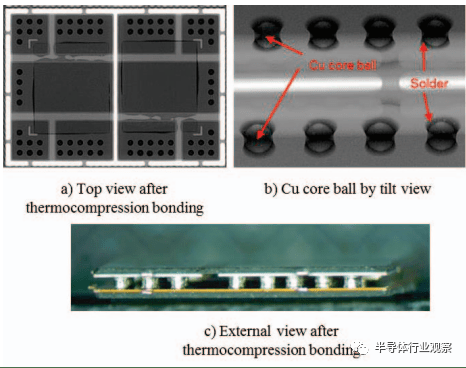

Amkor Technology Korea 高级总监 Byron Jin Kim 和他的团队使用 ICEPAK 软件比较了嵌入式 SiP 与双冷却 IGBT 在具有三个嵌入式结构的直接键合陶瓷上覆铜基板上的散热结果(见图 4)。选择 (d) 的嵌入式工艺在底部基板上使用芯片连接,并且只需要单面冷却。该团队确定基于引线框架的工艺模块表现出优于层压基板设计的热性能。此外,核心球的位置也很重要。

“铜芯球通过助焊剂印刷-球放置-回流工艺在顶部基板上进行。这种方法是在工艺参数设置中控制适当焊料润湿的关键,”报告称。展望未来,Amkor 预计会为类似系统提供各种嵌入式 SiP 选项,包括具有半桥和全桥应用的电源电路。

图 5:热压键合工艺显示芯片和铜球放置 (a),铜芯球润湿显示角度 (b) 的可布线微引线框架,以及成型前封装的侧视图 (c)。

封装天线

对于 5G 和 6G,天线技术具有挑战性。天线的相控阵取代了单个天线,因为在毫米波和太赫兹 (THz) 频率下,从半导体封装到天线的长路径会导致高损耗。这使得需要将这些天线集成到 SiP 中。

“在 2018 年之前,LGA SiP 被用于射频行业,但由于双面封装的发展,BGA 已被广泛采用,”Yole 的 Pereira 说。“博通、Qorvo 和 Skyworks 等厂商通过 DSBGA 和 DS-MBGA(双面模压 BGA)等解决方案实施逐步创新,而村田直接实施 DS-MBGA 以实现系统集成和小型化。台积电的集成扇出型封装天线 (InFO_AiP) 是另一个等待使用的创新解决方案,但由于成本效率低下而被推迟。”

除了不同的封装类型外,用于高频用途的基板也在发生变化。传统PCB材料由于介电损耗和吸水率高,无法满足5G太赫兹频率的需求。业界目前正在评估各种液晶聚合物 (LCP) 基板的电性能、气密性和材料灵活性。

“我们一直在努力寻找信号强度和信号损失之间的平衡点,就 5G 而言,我们正在研究许多不同的材料集、不同的 LCP 集成,”Chang 说。“希望这种最小损耗解决方案能够简化整体 AiP 设计。”

结论

封装公司和代工厂正在寻求各种 SiP 以满足移动消费、通信和基础设施以及汽车应用之间的不同需求。为了降低成本和提高制造可靠性,正在为倒装芯片、扇出和嵌入式 SiP 添加新材料和工艺。但是与保持信号完整性、更快地传输更多数据以及克服工具/基板限制相关的移动目标将继续鼓励下一代创新。

审核编辑:郭婷

-

SiP

+关注

关注

6文章

543浏览量

108014 -

物联网

+关注

关注

2950文章

48135浏览量

418574 -

sip封装

+关注

关注

4文章

69浏览量

16040

原文标题:SiP封装,越来越受欢迎

文章出处:【微信号:晶扬电子,微信公众号:晶扬电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

技术资讯 I 系统级封装(SiP)的关键器件

存储芯片SiP封装量产,PCB密度要求翻3倍,国内产能缺口达30%

半导体封装介绍

SiP 封装与锡膏等焊料协同进化之路

harmony-utils之PreferencesUtil,首选项工具类

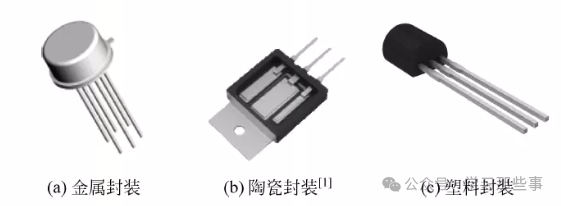

芯片传统封装形式介绍

SiP封装成为更多应用和市场的首选封装选项

SiP封装成为更多应用和市场的首选封装选项

评论