相对芯片大规模量产来说,前期的流片所需费用也不可小觑,尤其是对于不少Fabless公司来说,从第一版设计到定型,往往需要经历多次流片,从MPW、Full Mask到量产。设计失误或代工厂失误导致流片失败更是最让设计团队头疼的一件事,之所以每次流片验证是如此让人提心吊胆的过程,不仅是因为设计过程中付出的心血,还有流片所需的金钱与时间成本。

流片花费的时间

对于精力和产能都有限的这些晶圆代工厂来说,他们并不是随时都能帮助客户流片的,所以他们的MPW计划往往都有排期。首先,厂商要想找晶圆代工厂或第三方服务公司询问、预留并下达订单。排上之后提交自己的GDS数据,然后等待其他“拼车人”提交数据后再进入流片过程,最终等待芯片送到自己的手中。从设计提交截止到拿到芯片,可能需要半年以上的时间,这就是时间成本。

以三星为例,三星的12英寸和8英寸晶圆厂都有开展MPW服务,其中12英寸目前最高公开提供5LPE这一5nm的工艺。一般来说,越是先进的工艺,往往每年的MPW流片次数就越少,比如台积电的CyberShuttle可能今年就只提供一次3nm的MPW服务。如何缩短这些MPW项目的周转时间,其实也是晶圆代工厂需要考虑的问题之一。

三星MPW Shuttle 服务 / Samsung Foundry

然后就是流片的金钱成本了,以为光掩膜版的费用对于前期数量不多的试验片来说还是太贵了,所以不少厂商都选择了MPW这种共享光掩膜版的服务,定型后再走Full Mask。当然了,在MPW服务商,每家晶圆代工厂给出的定价其实并没有那么固定,而且不少先进工艺的定价也都是保密的,有的还需要签订NDA保密协议。所以我们一般只能通过第三方MPW服务公司提供的部分定价来获取公开信息。

几家晶圆厂的流片费用

格芯虽然没有参与到先进工艺的竞争中来,但无疑也是全球最大的几家晶圆代工厂之一了。格芯也与不少IC服务平台达成了合作,为不同地区提供MPW服务,所以他们的定价还算是比较公开的。以加拿大的CMC Microsystems给出的数据为例,格芯的12nm工艺12LP的定价为51525美元/mm2。还有一点需要注意的是,即便同为45nm工艺节点,但如果选择特种工艺,比如高压、硅光或射频等等,流片费用也还要再高一截的。

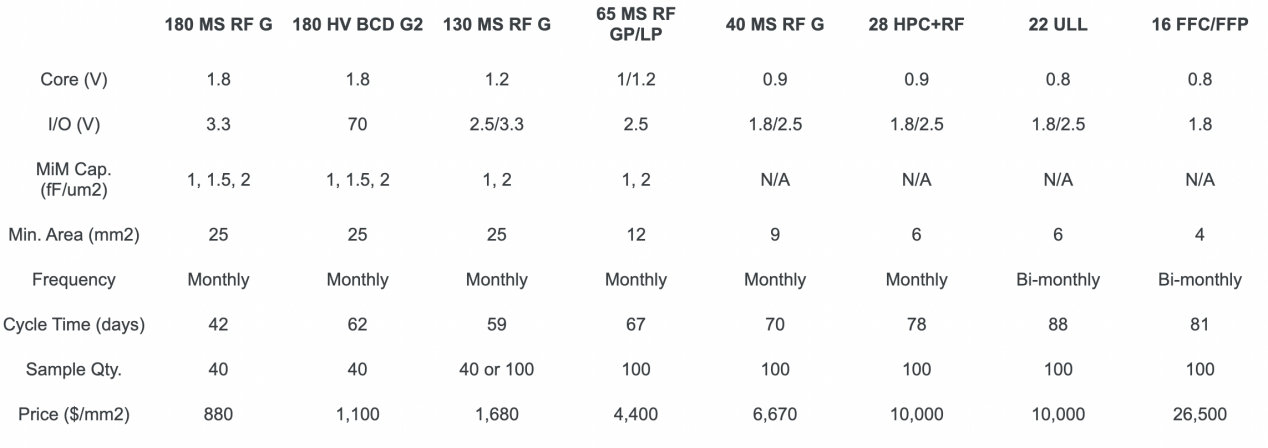

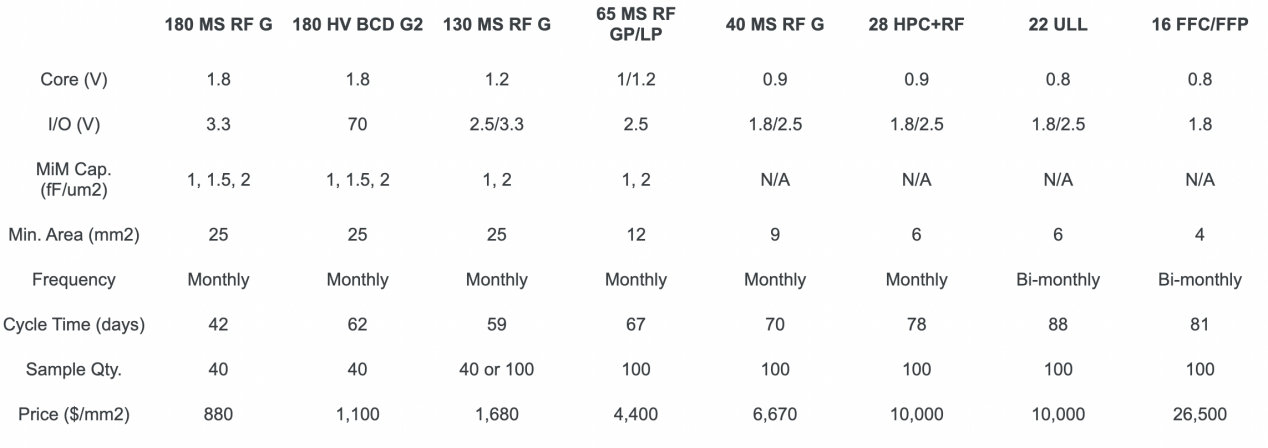

台积电部分工艺的MPW费用 / MUSE Semiconductor

在CMC提供的台积电MPW服务中,最先进的工艺为28nm的28 HPC+RF节点,定价为16850美元/mm2。而专供台积电MPW服务的MUSE Semiconductor,却最高可以提供16nm的16 FFC/FFP工艺节点,定价为26500美元/mm2。但该工艺下支持Full Block流片,有4mm2的最小面积要求,且频率为两月开展一次。

作为国内的龙头企业,中芯国际自然也提供了MPW服务,不过定价也没有公开。中芯国际在国内的MPW服务中心就有15个之多,工艺上也涵盖了0.18微米到14纳米。根据中芯国际官网的说明,除了每月根据不同工艺提供多达六次共乘服务以外,还提供一年6次55纳米和一年各四次40纳米和28纳米的MPW服务,就频率来看还是挺高的。

成本的话,我们目前可以从一些学界的项目中可以有个大致的了解。比如中科院包云岗教授开展的第一期“一生一芯”计划中,他们的教学芯片就选择了中芯国际的110nm工艺,价格在20万一个Block左右。今年西安交通大学电信学部微电子学院公开的中芯国际55nm流片服务MPW采购项目中,他们选择了中芯国际的55nm射频CMOS工艺,面积为3mm*4mm,给出的预算金额为40万元。

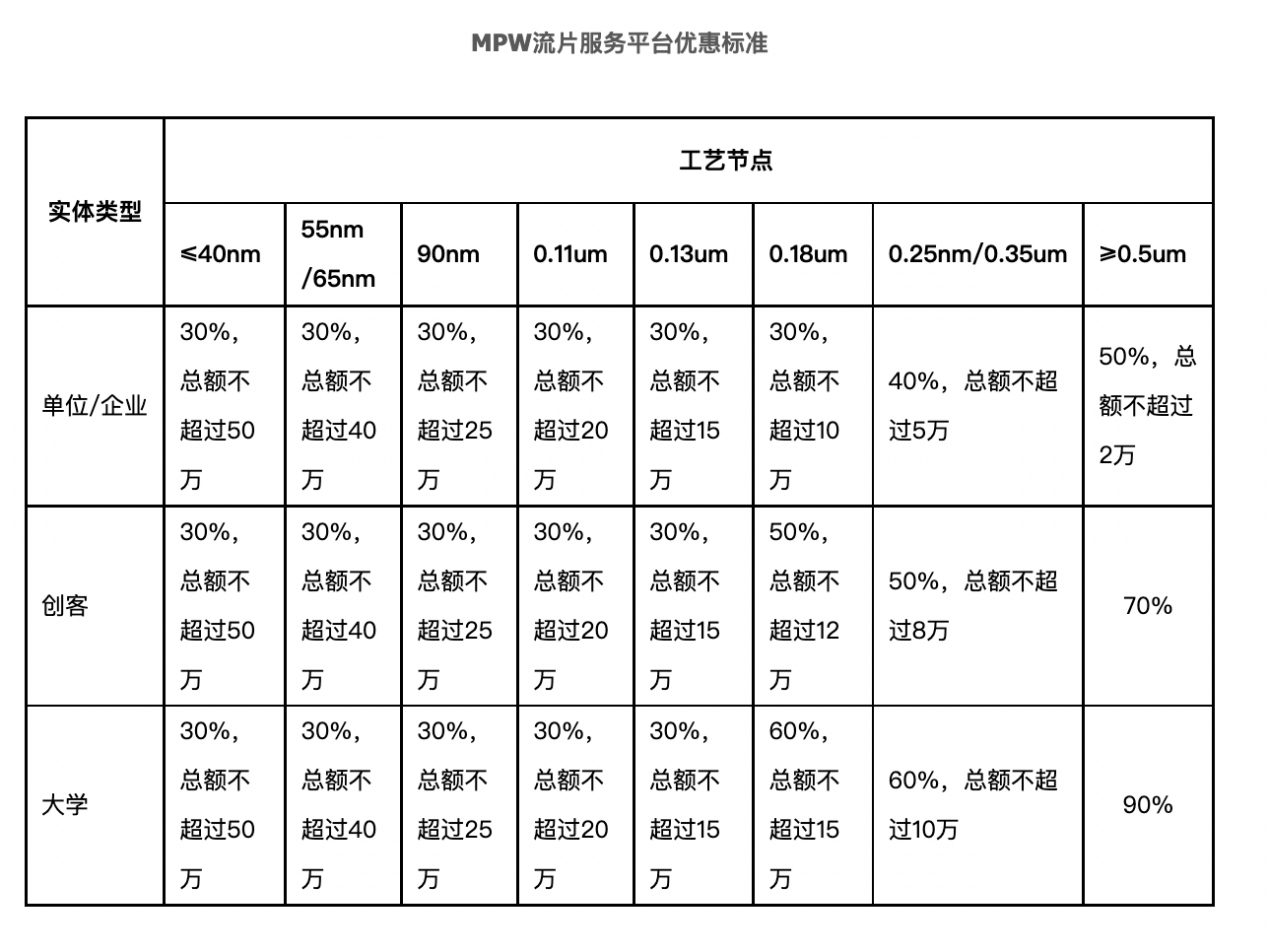

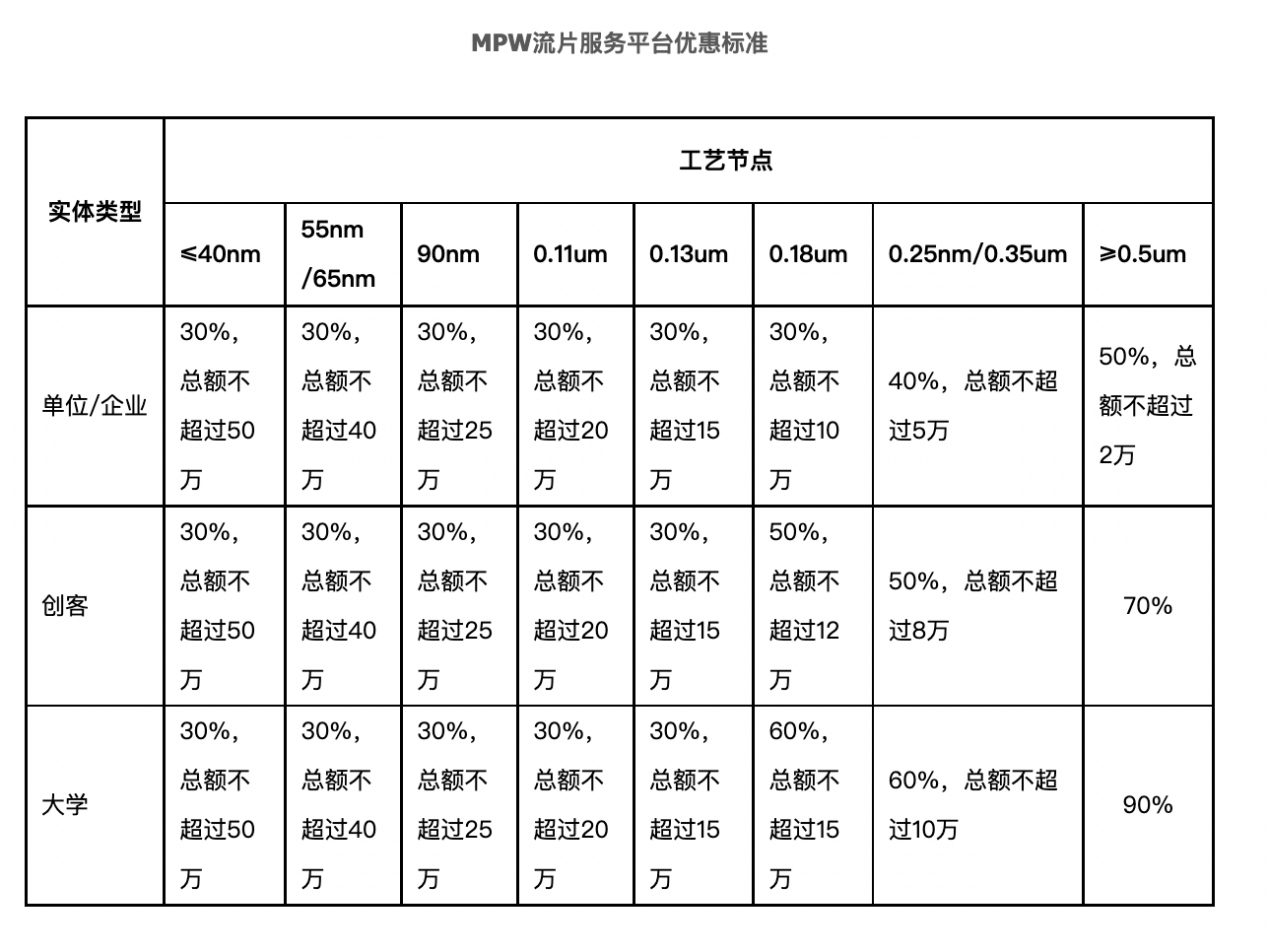

考虑到流片成本对一些初创企业和大学来说也确实很高,所以一些地方政府为了扶持集成电路设计产业的发展,也会给出一些优惠政策,比如国家集成电路设计深圳产业化基地与晶圆代工厂合作打造的MPW流片平台,就对单位/企业、创客和大学在不同的工艺节点上提供了不同程度的优惠,虽然这仅仅这对成熟工艺,但从30%到90%的优惠力度其实已经相当大了。而从上表的总额限制中,其实也可以看出这几个成熟工艺节点在成本上的差距。

晶圆厂积极参与MPW流片

与此同时,晶圆代工厂也开始积极与学研界合作,比如中芯国际就北大清华、东南大学等合作MPW项目。台积电也和台湾半导体研究中心达成合作,对于一些学界的MPW芯片项目提供优惠,甚至对于一些优秀成果产出提出更高的优惠,比如研究中心发表ISSCC论文的项目,可以享受免审查且百分百报销的服务(有工艺节点、芯片数量和总金额的限制)。

目前像美国的Skywater等晶圆代工厂也开始对开源芯片提供免费的MPW服务,只不过这些免费服务提供的工艺并不算先进,而且还是得由谷歌或者政府这样的靠山提供成本支持。不然的话别说免费或增加排期了,哪怕维持这样一个服务频率对晶圆代工厂来说都是一件吃力不讨好的事。

流片花费的时间

对于精力和产能都有限的这些晶圆代工厂来说,他们并不是随时都能帮助客户流片的,所以他们的MPW计划往往都有排期。首先,厂商要想找晶圆代工厂或第三方服务公司询问、预留并下达订单。排上之后提交自己的GDS数据,然后等待其他“拼车人”提交数据后再进入流片过程,最终等待芯片送到自己的手中。从设计提交截止到拿到芯片,可能需要半年以上的时间,这就是时间成本。

以三星为例,三星的12英寸和8英寸晶圆厂都有开展MPW服务,其中12英寸目前最高公开提供5LPE这一5nm的工艺。一般来说,越是先进的工艺,往往每年的MPW流片次数就越少,比如台积电的CyberShuttle可能今年就只提供一次3nm的MPW服务。如何缩短这些MPW项目的周转时间,其实也是晶圆代工厂需要考虑的问题之一。

三星MPW Shuttle 服务 / Samsung Foundry

然后就是流片的金钱成本了,以为光掩膜版的费用对于前期数量不多的试验片来说还是太贵了,所以不少厂商都选择了MPW这种共享光掩膜版的服务,定型后再走Full Mask。当然了,在MPW服务商,每家晶圆代工厂给出的定价其实并没有那么固定,而且不少先进工艺的定价也都是保密的,有的还需要签订NDA保密协议。所以我们一般只能通过第三方MPW服务公司提供的部分定价来获取公开信息。

几家晶圆厂的流片费用

格芯虽然没有参与到先进工艺的竞争中来,但无疑也是全球最大的几家晶圆代工厂之一了。格芯也与不少IC服务平台达成了合作,为不同地区提供MPW服务,所以他们的定价还算是比较公开的。以加拿大的CMC Microsystems给出的数据为例,格芯的12nm工艺12LP的定价为51525美元/mm2。还有一点需要注意的是,即便同为45nm工艺节点,但如果选择特种工艺,比如高压、硅光或射频等等,流片费用也还要再高一截的。

台积电部分工艺的MPW费用 / MUSE Semiconductor

作为国内的龙头企业,中芯国际自然也提供了MPW服务,不过定价也没有公开。中芯国际在国内的MPW服务中心就有15个之多,工艺上也涵盖了0.18微米到14纳米。根据中芯国际官网的说明,除了每月根据不同工艺提供多达六次共乘服务以外,还提供一年6次55纳米和一年各四次40纳米和28纳米的MPW服务,就频率来看还是挺高的。

成本的话,我们目前可以从一些学界的项目中可以有个大致的了解。比如中科院包云岗教授开展的第一期“一生一芯”计划中,他们的教学芯片就选择了中芯国际的110nm工艺,价格在20万一个Block左右。今年西安交通大学电信学部微电子学院公开的中芯国际55nm流片服务MPW采购项目中,他们选择了中芯国际的55nm射频CMOS工艺,面积为3mm*4mm,给出的预算金额为40万元。

考虑到流片成本对一些初创企业和大学来说也确实很高,所以一些地方政府为了扶持集成电路设计产业的发展,也会给出一些优惠政策,比如国家集成电路设计深圳产业化基地与晶圆代工厂合作打造的MPW流片平台,就对单位/企业、创客和大学在不同的工艺节点上提供了不同程度的优惠,虽然这仅仅这对成熟工艺,但从30%到90%的优惠力度其实已经相当大了。而从上表的总额限制中,其实也可以看出这几个成熟工艺节点在成本上的差距。

晶圆厂积极参与MPW流片

与此同时,晶圆代工厂也开始积极与学研界合作,比如中芯国际就北大清华、东南大学等合作MPW项目。台积电也和台湾半导体研究中心达成合作,对于一些学界的MPW芯片项目提供优惠,甚至对于一些优秀成果产出提出更高的优惠,比如研究中心发表ISSCC论文的项目,可以享受免审查且百分百报销的服务(有工艺节点、芯片数量和总金额的限制)。

目前像美国的Skywater等晶圆代工厂也开始对开源芯片提供免费的MPW服务,只不过这些免费服务提供的工艺并不算先进,而且还是得由谷歌或者政府这样的靠山提供成本支持。不然的话别说免费或增加排期了,哪怕维持这样一个服务频率对晶圆代工厂来说都是一件吃力不讨好的事。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

流片

+关注

关注

0文章

31浏览量

10042

发布评论请先 登录

相关推荐

热点推荐

Aigtek电压放大器基于微流控的声流混合及高效捕获在cfDNA的应用

时间,降低人工操作成本,减少干扰和污染并使样品损失降到最低。此外,由于微流控芯片的内部反应体积小,可以减少试剂消耗,更快的获得结果。cfDNA本质上是高度碎片化的DNA,并且在患者的血液中中被稀释,选择合适的样品制备方法可以显著

小华半导体车规处理器XC38流片成功

新年伊始,小华半导体汽车事业部迎来重大喜讯,匠心打造的XC38经过内部严格测试验证,正式宣布XC38流片成功。这一里程碑事件,表明小华半导体车规MCU开始进入中高端功能安全ASIL-D应用场景,且在

新思科技分享实现AI芯片一次流片成功的十大策略

由于 AI 芯片的硬件与软件之间存在高度复杂且相互依赖的关系,定制 AI 芯片已成为当今半导体行业中资金投入最高、风险最大的研发项目之一。一旦设计需要重新设计进行二次流片,成本还会大幅攀升,甚至会

首期基于华大九天EDA工具的Mini MPW流片专项学习交流会圆满落幕

近日,首期基于华大九天模拟、数字芯片设计全流程EDA工具的Mini MPW 流片专项学习交流会圆满落幕,北京华大九天科技股份有限公司和浙江省集成电路创新平台(浙江创芯集成电路有限公司)联合举办,吸引了来自全国 50余所高校及院所、企业的共约200名集成电路领域的学员参与。

Cadence公司成功流片第三代UCIe IP解决方案

为推动小芯片创新的下一波浪潮,Cadence 成功流片其第三代通用小芯片互连技术(UCIe)IP 解决方案,在台积电先进的 N3P 工艺上实现了业界领先的每通道 64Gbps 速率。随着行业向日

全链条补贴!厦门:芯片流片补60%、EDA补30%、IP补30%

、支持产品推广应用和支持产业要素保障,涉及全链条各维度补助、奖励和支持。(一)支持核心技术研发1.流片补助。(1)研发流片补助。①对开展多项目晶圆(MPW)

芯驰科技高端车规MCU E3620P成功流片并开启送样

芯驰科技宣布,其专为新能源动力系统设计的高端车规MCU——E3620P已成功流片并顺利通过回片验证。该产品已提前获得多个国内新能源头部主机厂及Tier 1定点锁定,并顺利开启客户送样。

新思科技LPDDR6 IP已在台积公司N2P工艺成功流片

新思科技近期宣布,其LPDDR6 IP已在台积公司 N2P 工艺成功流片,并完成初步功能验证。这一成果不仅巩固并强化了新思科技在先进工艺节点 IP 领域的领先地位,同时也为客户提供可信赖的、经硅片验证的IP选择,可满足移动通讯、边缘 AI 及高性能计算等更高存储带宽需求的

英伟达下一代Rubin芯片已流片

为进入市场做准备,Rubin架构将会有6个芯片,这些芯片都已经流片。这一消息在半导体和人工智能领域引起了广泛关注,预示着英伟达在芯片技术上的又一次重大飞跃。 Rubin芯片采用先进的台积电3nmEUV工艺制造,并且搭载HBM4高带宽内存,初期为8堆栈配置。这样的工艺和

什么是反时限过流保护?深入解析反时限过流保护的应用场景与优势

些具体情况下,我们应当优先考虑使用反时限过流保护。1.反时限过流保护的基本原理反时限过流保护,顾名思义,其动作时间与流过保护装置的电流大小呈反比关系。即当短路电流

微流控芯片的封合工艺有哪些

原理及操作流程:以PDMS基片微流控芯片为例,先制备带有微通道的PDMS基片,将其与盖片对准贴合,然后把对准贴合的二者置于160 - 200℃温度下保温一段时间。这种方法利用高温使材料发生一定的物理变化来实现封装。推荐设备:汶

芯片流片首次成功率仅14%?合科泰解析三大破局技术

你知道吗?把设计好的芯片图纸变成实物,这个关键步骤叫“流片”。但最近行业曝出一个惊人数据:2025年,芯片第一次流片的成功率只有14%!相比两年前的24%,几乎“腰斩”。这背后,作为深

人工合成石墨片与天然石墨片的差别

原料易得、工艺简单,成本较人工石墨低。天然石墨片与人工合成石墨的价格为1:4~5,人工合成石墨制造比天然石墨复杂且制作成本昂贵。 2、场景适配指南 ※ 天然石墨适用场景动力电池电极、工业润滑剂、电弧炉

发表于 05-23 11:22

流片的时间与金钱成本

流片的时间与金钱成本

评论