在硬件设计过程中,当原理图设计完成后需要提交EDA团队进行PCB的绘制,其中传输线阻抗的控制是重要的一项内容。在提交PCB设计说明书时,需要对线宽/线间距做出要求;在PCB设计过程中,需要与EDA设计人员进行沟通,可能会对线宽/线间距、相邻层厚度做适当调整;在提交PCB制版后,厂家会结合实际生产条件进行阻抗调整,这也需要硬件开发人员进行确认。因此,作为硬件开发人员,需要对传输线阻抗的原理和计算方法有所了解。传输线阻抗控制主要有两种:单端阻抗和差分阻抗。单端阻抗的阻值一般控制在50欧姆左右,差分阻抗一般控制在100欧姆左右。接下来介绍传输线特征阻抗的等效模型,并结合具体单板PCB设计,介绍如何利用Polar Si9000工具进行特征阻抗的计算。

一、传输线的等效模型

1. 等效模型及参数

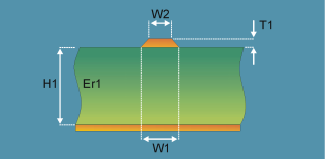

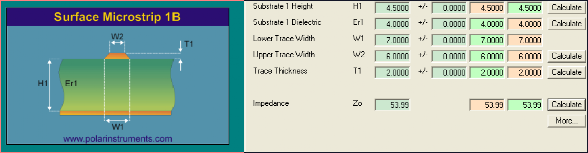

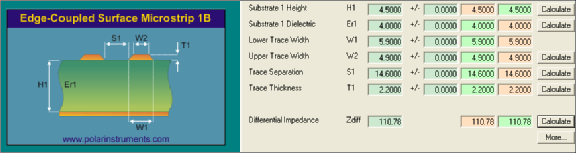

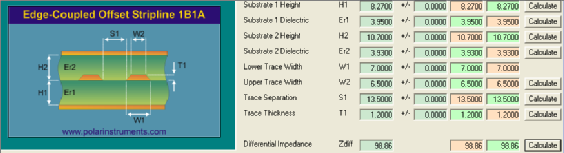

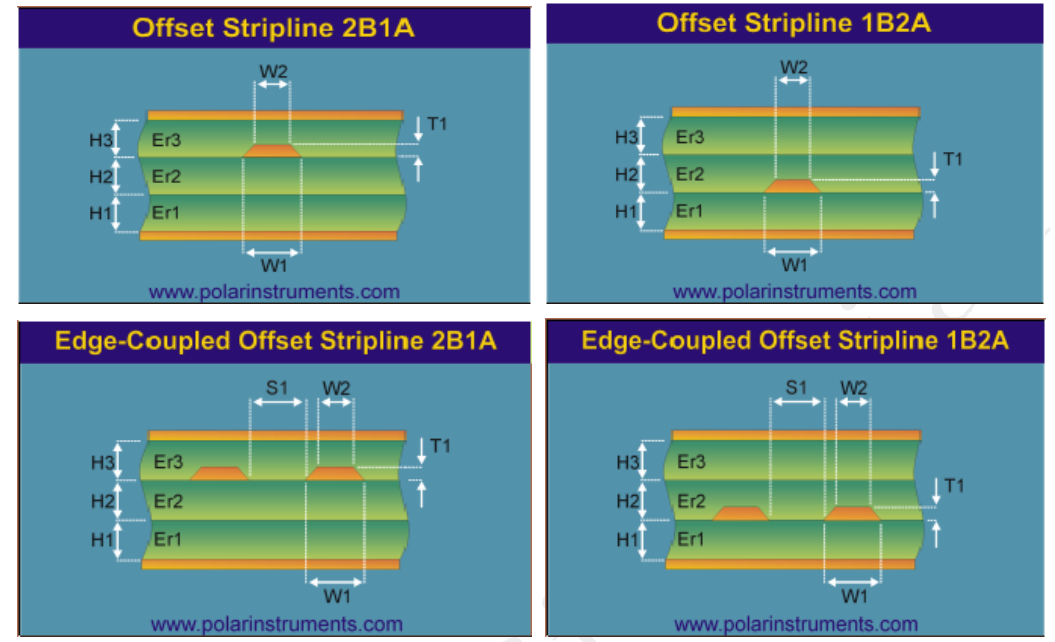

图1:传输线等效模型传输线等效模型如图1示,其中各参数如下:1、铜层厚度(T1)2、PCB板迹线的上下线宽(W2,W1)3、绝缘层厚度(H1)4、介电常数(Er1)5、若为差分线,则还有一个参数线间距(S1)。

图1:传输线等效模型传输线等效模型如图1示,其中各参数如下:1、铜层厚度(T1)2、PCB板迹线的上下线宽(W2,W1)3、绝缘层厚度(H1)4、介电常数(Er1)5、若为差分线,则还有一个参数线间距(S1)。2.参数说明

特征阻抗主要与线宽,绝缘层厚度等参数有关。线宽越大,特征阻抗越小;绝缘层越厚,相应的特征阻抗越大。阻抗控制采用以下参数:介质常数(Er1):4.0,FR4材料。下线宽(W1):设计线宽(假设为W);上线宽(W2):外层走线=W-1; 内层走线=W-0.5;铜层厚度(T1):分为表层与内层,如下表。需电镀填铜层铜厚(表层):| 电镀填铜层基铜铜厚(OZ) | 1/3 OZ | 1/2OZ | 1 OZ |

| 计算铜厚(mil) | 1.7 | 2.0 | 2.7 |

| 非电镀填铜层铜厚(OZ) | 1/2OZ | 1 OZ | 1.5OZ |

| 计算铜厚(mil) | 0.6 | 1.2 | 2.56 |

二、具体计算实例:

计算所使用的PCB模型为某低速业务板工装测试背板,有18层,其结构如下:表1:| L1 | --------------------------------------- | 0.5oz +电镀 |

| PP 2116 4.495mil | ||

| L2 | 1oz | |

| CORE 0.21 8.27mil | ||

| L3 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L4 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L5 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L6 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L7 | --------------------------------------- | 1oz |

| PP 1080+7628 9.82mil | ||

| L8 | --------------------------------------- | 1oz |

| CORE 0.15 5.9mil | ||

| L9 | --------------------------------------- | 1oz |

| PP 3313 3.42mil | ||

| CORE 1(0.5oz) 37.99mil | ||

| PP 3313 3.37mil | ||

| L10 | --------------------------------------- | 1oz |

| CORE 0.15 5.9mil | ||

| L11 | --------------------------------------- | 1oz |

| PP 1080+7628 9.8325mil | ||

| L12 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L13 | --------------------------------------- | 1oz |

| PP 1080+7628 9.4575mil | ||

| L14 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L15 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L16 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L17 | --------------------------------------- | 1oz |

| PP 2116 4.495mil | ||

| L18 | ---------------------------------------- | 0.5oz+电镀 |

| 阻抗计算值 | ||||||

| 层别 | 调整线宽/线间距 | 计算值(ohm) | H1(mil) | Er1 | H2(mil) | Er2 |

| L1/18 | 7.6 mil to 7 mil | 49.6 | 4.5 | 3.95 | ||

| L1/18 | 7/13.5 mil to 5.9/14.6 mil | 98.3 | 4.5 | 3.95 | ||

| L3/16/5/14 | 7.6 mil | 49.6 | 8.27 | 3.95 | 10.7 | 3.93 |

| L3/16/5/14 | 7/13.5 mil | 98.1 | 8.27 | 3.95 | 10.7 | 3.93 |

| L7/12 | 7.6 mil | 50 | 8.27 | 3.95 | 11.07 | 3.93 |

| L7/12 | 7/13.5 mil | 98.7 | 8.27 | 3.95 | 11.07 | 3.93 |

| L9/10 | 7.6 mil to 8 mil | 51.5 | 5.9 | 3.65 | 53.18 | 3.89 |

| L9/10 | 7/13.5 mil | 99.1 | 5.9 | 3.65 | 53.18 | 3.89 |

| L9的屏蔽层为: | L8/L11 | |||||

| L10的屏蔽层为: | L8/L11 | |||||

| 其他层邻层屏蔽 | ||||||

2.1 表层(L1/L18)单端阻抗计算:(单位:mil)

参数说明:H1为绝缘层的厚度4.5mil;W1= 7.0mil;W2= W1-1=6.0mil;T1=2. 0 mil;Er1=4;计算结果:Z0=53.99欧姆。加工后的实际阻抗应为:Z0′=Z0-3=50.99欧姆与厂家所给出的阻抗值基本一致。

参数说明:H1为绝缘层的厚度4.5mil;W1= 7.0mil;W2= W1-1=6.0mil;T1=2. 0 mil;Er1=4;计算结果:Z0=53.99欧姆。加工后的实际阻抗应为:Z0′=Z0-3=50.99欧姆与厂家所给出的阻抗值基本一致。2.2表层(L1/L18)差分线阻抗计算:(单位:mil)

参数说明:H1为绝缘层的厚度4.5mil;W1= 5.9mil;W2=4.9mil;S1= 14.6 mil;T1=2.2mil;Er1=4;计算结果:Z0=110.78欧姆。加工后的实际阻抗应为:Z0′=Z0-9=101.78欧姆与厂家所给出的阻抗值基本一致。

参数说明:H1为绝缘层的厚度4.5mil;W1= 5.9mil;W2=4.9mil;S1= 14.6 mil;T1=2.2mil;Er1=4;计算结果:Z0=110.78欧姆。加工后的实际阻抗应为:Z0′=Z0-9=101.78欧姆与厂家所给出的阻抗值基本一致。2.3内层(L3/L10)单端阻抗计算:(单位:mil)

以L3层为例,参数设置如下: 参数说明:H1为绝缘层厚度8.27mil。Er1为3.95;W1=7.6 mil;W2= W1-0.5=7.1mil;T1=1.2mil;Er2 =3.93;H2为芯板的厚度加上铜箔的厚度为10.7mil计算结果:Z0=49.91欧姆。与厂家所给出的阻抗值基本一致。

参数说明:H1为绝缘层厚度8.27mil。Er1为3.95;W1=7.6 mil;W2= W1-0.5=7.1mil;T1=1.2mil;Er2 =3.93;H2为芯板的厚度加上铜箔的厚度为10.7mil计算结果:Z0=49.91欧姆。与厂家所给出的阻抗值基本一致。2.4内层差分线(L3/L10)阻抗计算: (单位:mil)

以L3层为例,参数设置如下: 参数说明:H1为绝缘层的厚度8.27mil。Er1为3.95;W1 =7 mil;W2= W1-0.5=6.5mil;S1 =13.5 mil;T1=1.2mil;Er2 =3.93;H2为绝缘层的厚度加上铜箔的厚度,为10.7mil计算结果:Z0=98.86欧姆。与厂家所给出的阻抗值基本一致。

参数说明:H1为绝缘层的厚度8.27mil。Er1为3.95;W1 =7 mil;W2= W1-0.5=6.5mil;S1 =13.5 mil;T1=1.2mil;Er2 =3.93;H2为绝缘层的厚度加上铜箔的厚度,为10.7mil计算结果:Z0=98.86欧姆。与厂家所给出的阻抗值基本一致。2.5 相邻信号层的阻抗计算

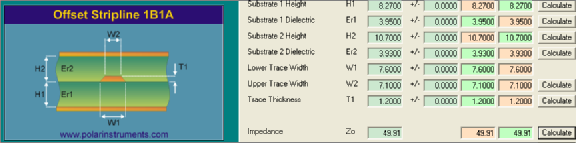

理论上相邻信号层的阻抗计算应该用如下模型,如第9第10两层。但是这样非常繁琐,可以简化成2.3,2.4中所述的模型,实际厂家给出的参数也证明了这一点。只要将H1,H2,Er1 ,Er1作相应调整即可,具体参数见表1,表2中所示。

三、总结

本文介绍了传输线特征阻抗的等效模型,并结合具体单板PCB设计,介绍了利用Polar Si9000工具计算特征阻抗的方法,希望能对大家有所帮助。审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

阻抗

+关注

关注

17文章

983浏览量

48767 -

PCB设计

+关注

关注

396文章

4907浏览量

94090 -

传输线

+关注

关注

0文章

382浏览量

25362

原文标题:【PCB设计】传输线特征阻抗的计算方法及实例

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

锂电池嵌入电极颗粒的传输线法TLM 模拟研究

中锂离子扩散行为的传输线模型TLM。该模型通过有限体积法离散化扩散方程,构建出具有明确物理意义的等效电路,不仅能与TLM测试仪所获得的实验数据形成互补,更能从微观

基于传输线模型(TLM)的特定接触电阻率测量标准化

金属-半导体欧姆接触的性能由特定接触电阻率(ρₑ)表征,其准确测量对器件性能评估至关重要。传输线模型(TLM)方法,广泛应用于从纳米级集成电路到毫米级光伏器件的特定接触电阻率测量,研究发现,不同尺寸

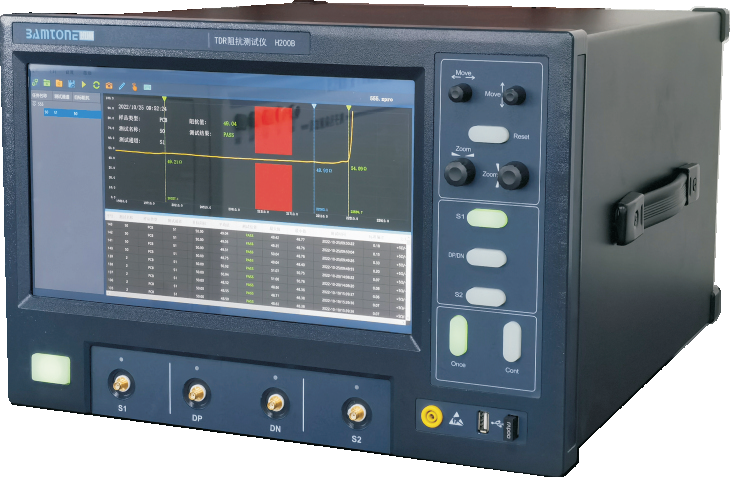

如何用TDR阻抗测量仪快速定位PCB传输线故障?

TDR阻抗测量仪是一款基于时域反射原理(TDR)设计的高带宽特性阻抗测试分析专用仪器,它非常适用于快速定位PCB传输线故障。以下是使用TDR阻抗测量仪进行故障定位的步骤和一些关键点:

Bourns 推出全新共模电感系列 专为信号传输线应用提供理想的噪声抑制解决方案

信号传输线应用中的噪声抑制而设计。Bourns® SRF1209U4 系列片式共模电感器具备薄型、紧凑尺寸的特点,能满足空间受限的设计需求。此款全新电感器在高频范围内提供高阻抗,能有效提升信噪比,非常

发表于 06-26 17:39

•1060次阅读

知识分享-传输线的返回电流(信号完整性揭秘)

信号完整性揭秘-于博士SI设计手记3.3传输线的返回电流按照传统的电路理论,电流要流到互连线的末端,然后从另一条路径回流,才能形成电流回路。如果传输线无限长,信号电压施加到传输线上后,信号永远也

传输线高频参数之Crosstalk

是由于电信号在通过传输线时,产生的电场线穿过了相邻的传输线,而导致相邻的传输线上也产生了电信号,如上图所示,用网分测试的时候,差分S参数Sdd31表示近端串扰,Sd

如何确保模拟示波器的输入阻抗匹配?

:

适用信号源输出阻抗 ≥ 1 kΩ(如逻辑分析仪、低频传感器)。

避免使用在 50 Ω 特征阻抗的传输线 上,否则会导致反射。

50 Ω 模式:

适用信号源输出

发表于 04-08 15:25

PCB制板厂加工问题很大啊,高速PCB传输线阻抗一直往上跑

都窜不高,走线越长,窜得越高!Chris给大家做个简单的仿真看看哈,假设我们设置一个内层的传输线叠层,使得差分线在线宽5mil,间距9mil的情况下满足100欧姆的阻抗要求。

首先我们设置这对差分线

发表于 04-07 17:27

PCB Layout中的三种走线策略

的情况。

不同角度走线的拐角线宽变化直角走线的对信号的影响就是主要体现在三个方面:一是拐角可以等效为传输线上的容性负载,减缓上升时间;二是阻抗

发表于 03-13 11:35

从驱动端到串联电阻之间的这一段走线应该走成多少阻抗呢?

例如,驱动器内阻为20欧,理论上采用驱动端串联30欧电阻,与50欧特征阻抗的传输线进行匹配,但是从驱动端到串联电阻之间的这一段走线应该走成多少阻抗

发表于 01-08 07:28

PCB设计中的Stub天线对信号传输的影响

。这是因为传输线瞬态阻抗计算公式为:Z=\sqrt{\frac{L}{C}}Stub就像并联在传输线上的小电容,Stub越长,电容量越大,阻抗也就越低。2.信号反射:

DAC3482的I通道输出电路,传输线变压器有什么作用?

下图是DAC3482的I通道输出电路,这里T11是1:1的传输线变压器,T4是4:1的变压器。如果IOUTA2是20mA,IOUTA1是0mA,求分析下此时IOUTA2输出是多少,为什么?这里的传输线变压器有什么作用?前面两个100欧电阻中间接地有啥作用?

发表于 12-20 07:50

阻抗对信号传输的影响 阻抗测量仪器的选择

对信号传输的影响主要体现在以下几个方面: 信号反射 :如果信号源的输出阻抗和传输线的输入阻抗不匹配,就可能会发生信号反射,使得信号无法完全进入传输线

传输线特征阻抗的等效模型

传输线特征阻抗的等效模型

评论