MS90C386B、MS90C385B/G是瑞盟2012年推出的1Port_LVDS_RxTx,MS90C386B为LVDS to LVTTL(RGB),直接替换THC63LVDF84B、DS90C386、DTC34LF86L等;MS90C385B/G为LVTTL(RGB) to LVDS,MS90C385B为TSSOP56封装,MS90C385G为TFBGA56封装,直接替换THC63LVD83D、DS90C385、DTC34LF85L等。关键特点如下:

一、MS90C386B:LVDS转LVTTL

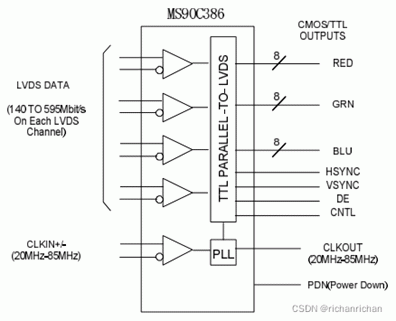

MS90C386(B)芯片能够将 4 通道的低压差分信号(LVDS)转换成 28bit 的 TTL 数据。时钟通道经过锁相之后与数据通道并行输出。在时钟频率为 85MHz 时,24bit 的 RGB 数据、3bit 的 LCD 时序数据和1bit 的控制数据以 595Mbps 的速率在每个 LVDS 数据通道中传输。输入时钟频率为85MHz时,数据的传输速率为 297.5Mbytes/sec。此款芯片配合 MS90C385,是解决高带宽、高速 TTL 信号层面的电磁干扰和电缆长度问题的理想产品。

◇Pin to Pin替代:THC63LVDF84B、DS90C386、DTC34LF86L

◇MS90C386 与 MS90C386B 仅版本差异,MS90C386B兼容MS90C386!

◇MS90C386功能框图

◇频率范围:20-85MHz 时钟信号

◇较少的总线减少了连线尺寸和费用

◇供电电源 3.3V

◇支持VGA、SVGA、XGA、SXGA,最大支持1440×1050@60Hz、1360×768@60Hz、1280×768@60Hz

◇2.38Gbps数据吞吐量

◇297.5Megabytes/sec 带宽

◇减小LVDS摆幅来减小电磁干扰(300mV LVDS 摆幅)

◇遵循 TIA/EIA-644 LVDS 标准

二、MS90C385B/G:LVTTL to LVDS

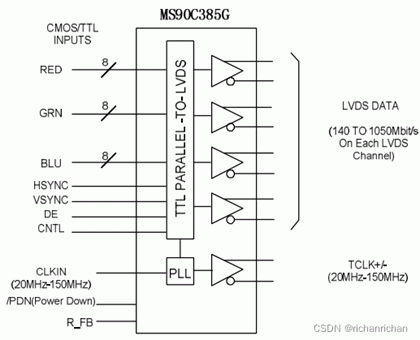

MS90C385B/G 芯片能够将28bit 的TTL 数据转换成4通道的低压差分型号(1Port LVDS)。时钟通道经过锁相之后与数据通道并行输出。在时钟频率为 150MHz 时,24bit的RGB 数据、3bit 的 LCD 时序数据和1bit的控制数据以 1050Mbps 的速率在每个 LVDS 数据通道中传输。输入时钟频率为 150MHz 时,数据的传输速率为 525Mbytes/sec。MS90C385 的R_FB 管脚可以选择在时钟的上升沿或者下降沿有效。此款芯片是解决高带宽、高速 TTL 信号层面的电磁干扰和电缆长度问题的理想产品。

◇MS90C385B/G功能框图

◇MS90C385B封装TSSOP56, MS90C385G封装TFBGA56

◇MS90C385B Pin to Pin替代:THC63LVD83D、DS90C385、DTC34LF85L

◇MS90C385B兼容MS90C385!

◇频率范围:20-150MHz 时钟信号

◇内核供电电源 3.3V

◇IO供电电源1.8V、3.3V兼容

◇支持VGA、SVGA、XGA、SXGA,最大支持1440×1050@60Hz、1360×768@60Hz、1280×768@60Hz

◇支持扩展频谱时钟产生

◇内部集成输入抖动滤波器

◇减小LVDS摆幅来减小电磁干扰(200mV、345mV LVDS摆幅可供选择)

◇PLL不需要外部结构

◇遵循 TIA/EIA-644 LVDS 标准

三、MS90C385B、MS90C386B在JEIDA-VESA模式中的具体应用

LVDS信号模式有两种: JEIDA与VESA。 LCD屏老一点的有6Bit的,现在普通的是8Bit,新的就是10Bit了,每个clock周期内7bit数据(跟TMDS标准有差别)。

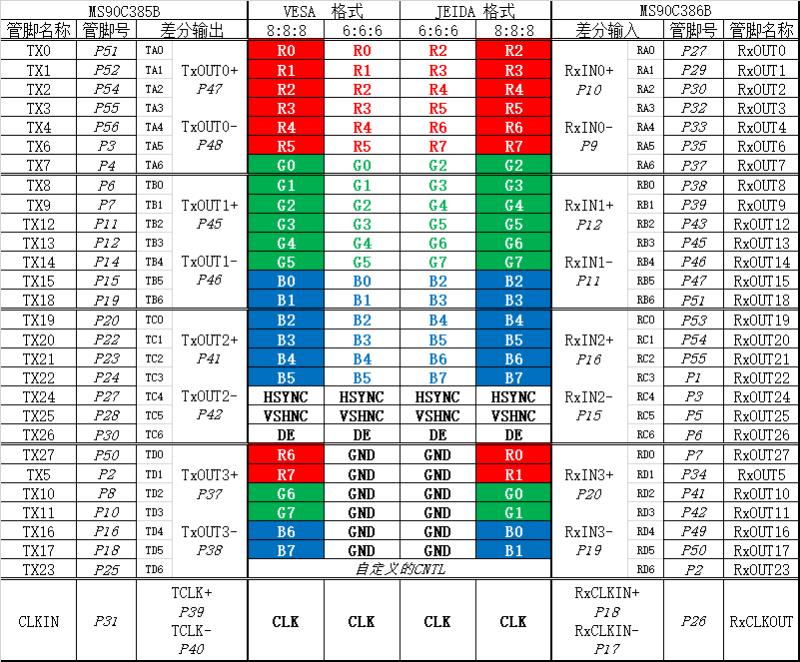

本篇以我公司代理的1Port LVDS发送(Tx)MS90C385B及接受(Rx)MS90C386B为例详解,我们根据电子产品CPU定义的JEIDA(或VESA)及输出的RGB565、RGB666、RGB888视频格式对MS90V385B、MS90C386B数据引脚作对应调整, JEIDA 、VESA模式的RGB数据对应的LVDS转换IC Pin脚参见下表。

MS90C385B MS90C386B之JEIDA VESA模式引脚对应RGB数据表

(注意:上图展示MS90C385B 6:6:6为连接18bit显示屏之Pin对应关系)

以连接18bit显示(即6Bit屏)及主板显示输出18bit/24bit、3Lane_LVDS为例,详解JEIDA、VESA模式下MS90C386B、MS90C385B对应引脚连接方法:

1、MS90C386B之RGB666输出引脚连接

1.1、VESA格式下之高位引脚空置:RGB666之高位(R6 R7 G6 G7 B6 B7)对应Pin脚7、34、41、42、49、50悬空(建议接地),屏驱动软件按VESA模式高位RGB数据(R6 R7 G6 G7 B6 B7)不使用配置,启用R0 R1 R2 R3 R4 R5 G0 G1 G2 G3 G4 G5 B0 B1 B2 B3 B4 B5 Hsync Vsync DE ,对应MS90C386B Pin脚为27 29 30 32 33 35 37 38 39 43 45 46 47 51 53 54 55 1 3 5 6脚 ,无用Pin脚接地,防止电磁干扰!

1.2、JEIDA格式下之低位引脚空置:RGB666之低位(R0 R1 G0 G1 B0 B1)对应Pin脚7、34、41、42、49、50悬空(建议接地),与上述1.1悬空引脚一致!屏驱动软件按JEIDA模式低位RGB数据(R0 R1 G0 G1 B0 B1)不使用配置,启用R2 R3 R4 R5 R6 R7 G2 G3 G4 G5 G6 G7 B2 B3 B4 B5 B6 B7 Hsync Vsync DE ,对应MS90C386B Pin脚分别为27 29 30 32 33 35 37 38 39 43 45 46 47 51 53 54 55 1 3 5 6脚 ,与上述1.1对应引脚一致!无用Pin脚接地。

1.3、RGB666视频格式下,LVDS差分输入仅用3组:JEIDA、VESA格式下3Lane数据LVDS输入与RGB666输出对应引脚一致,具体参考上面图表“MS90C385B MS90C386B之JEIDA VESA模式引脚对应RGB数据表”,即启用3Lane LVDS输入数据RxIN0±、RxIN1±、RxIN2±,对应引脚分别为10-9、12-11、16-15,还有1Lane输入时钟RxCLKIN±, 对应引脚18-17。

第4Lane LVDS RxIN3±不用(P20-P19),但需按以下电路连接:

2、MS90C385B连接18bit LVDS显示之RGB666输入引脚连接

2.1、VESA格式下之高位引脚空置:RGB666之高位(R6 R7 G6 G7 B6 B7)对应Pin脚50、2、8、10、16、18悬空(建议接地),屏驱动软件按VESA模式高位RGB数据(R6 R7 G6 G7 B6 B7)不使用配置,启用R0 R1 R2 R3 R4 R5 G0 G1 G2 G3 G4 G5 B0 B1 B2 B3 B4 B5 Hsync Vsync DE ,对应MS90C385B Pin脚为51 52 54 55 56 3 4 6 7 11 12 14 15 19 20 22 23 24 27 28 30脚,无用Pin脚接地,防止电磁干扰!

2.2、JEIDA格式下之低位引脚空置:RGB666之低位(R0 R1 G0 G1 B0 B1)对应Pin脚50、2、8、10、16、18悬空(建议接地),与上述2.1项悬空引脚一致!屏驱动软件按JEIDA模式低位RGB数据(R0 R1 G0 G1 B0 B1)不使用配置,启用R2 R3 R4 R5 R6 R7 G2 G3 G4 G5 G6 G7 B2 B3 B4 B5 B6 B7 Hsync Vsync DE ,对应MS90C385B Pin脚分别为51 52 54 55 56 3 4 6 7 11 12 14 15 19 20 22 23 24 27 28 30脚 ,与上述2.1项对应引脚一致!无用Pin脚接地。

2.3、在18bit LVDS显示之RGB666视频格式下,LVDS差分输出仅用3组:JEIDA、VESA格式下3Lane数据LVDS输出与RGB666输入对应引脚一致,具体参考上面图表“MS90C385B MS90C386B之JEIDA VESA模式引脚对应RGB数据表”,即仅用3Lane LVDS输出数据TxOut0±、TxOut1±、TxOut2±,对应引脚分别为47-48、45-46、41-42,还有1Lane输出时钟TCLK±, 对应引脚39-40。第4Lane LVDS TxOut3±悬空不用(P37、P38),建议该Pin接地。

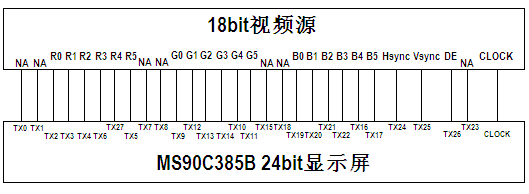

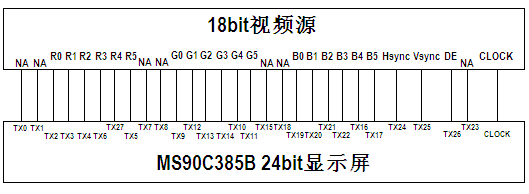

2.4、视频源为18bit(RGB666),而输出显示屏为24bit时:MS90C385B之TX0(P51)、TX1(P52)、TX7(P4) 、TX8(P6)、TX15(P15)、TX18(P19)悬空或接地,这是MS90C385B应用特殊点,切记!具体如下图所示:

3、MS90C385B、MS90C386B 在RGB888 之VESA、JEIDA模式下Pin连接方法则按上面图表“MS90C385B MS90C386B之JEIDA VESA模式引脚对应RGB数据表”对应连接即可,这里不再详细说明。

4、MS90C385B MS90C386B在RGB565格式之输入_输出引脚连接

MS90C386B之RGB565格式输入LVDS与输出RGB引脚连接与本篇上述1.1-1.3项应用一致,不同点为:JEIDA模式下R2、B2对应之引脚27、47脚悬空不用,无用引脚接地。VESA模式下R5、B5对应之引脚35 、1脚悬空不用,无用引脚接地。

MS90C385B之RGB565格式输入RGB与输出LVDS引脚连接与本篇上述2.1-2.3项应用一致,不同点为:JEIDA模式下R2、B2对应之引脚51、15脚悬空不用,无用引脚接地。但有客户将R2(P51脚)与R7(P3脚)连接,将B2(P15脚)与B7(P24脚)连接事例。VESA模式下R5、B5对应之引脚3、24脚悬空不用,无用引脚接地。

四、LVDS信号PCB Layout注意事项

1、LAYOUT时,差分信号输出端,几组线必须等长、等宽(8mil-10mil), 且阻抗必须控制在每对线100Ω。

2、电源需分成3组LVDS,Logic,PLL,其三组电源必须分开LAYOUT。

3、地不需分割,分割反而不好。

4、在电源部份要加濾波电容推荐1uF及104。

5、接收端之LVDS必须于每对线终端(靠LVDS脚位处)各接100Ω电阻(即MS90C386)。

6、输入讯号端串聯一个终端电阻为20Ω-40Ω(建议值)連接至信号端再串接一个电容(其电容值取决于EMC的频率,其建议值为100PF~400PF)。

7、RGB信号线,其尽可能要等长、等宽,不然也不可以差太多,否则信号会受影响。

8、CLOCK和信号线Fan out时,其最好可以等长、等宽,若无法等长、等宽,也不能差距太多,否则输出讯号品质会很差。

9、CLOCK走线两边包GND,其作用在于避免串音到其它信号,若无包地,与其它信号必须至少留3倍线宽的间距。

10、LAYOUT时,若正反面摆件时,须注意正面要摆放ANALONG及高频的零件 ,而背面则放置低频的零件,例如: LAYER1.ANALONG/高频零件, LAYER2.GND , LAYER3.VCC , LAYER4.低频零件。

11、电源脚须接上濾波电容,不可将濾波电容距離IC电源脚太远,否则没有虑波效果。

12、重要的信号脚预留连接IC电源(Vcc)之电阻位置(如Clock引脚)。

13、LVDS LAYOUT时, 须独立出一块(中间挖空),上下走线,其中间不走任何信号线。

14、CONNECTOR(中间挖空),上下走线,其中间不走任何信号线,其做用在于防打静电及EMI。

15、信号频率较高的信号线与信号频率较低的信号线(约相差100KHZ)平行走线时,此二线中间需加GND trace或Plane(平面,层)避免串音发生。高电压(高电流)与低电压(低电流)的信号线平行走线时,此二线中间亦需加GND Trace 或Plane(平面,层),避免串音发生。

-

电源

+关注

关注

185文章

18976浏览量

264441 -

lvds

+关注

关注

2文章

1241浏览量

70208

发布评论请先 登录

Onsemi FQP4N90C与FQPF4N90C MOSFET深度解析

onsemi FQP4N90C与FQPF4N90C MOSFET深度解析

探索DS90C032B:高性能LVDS四通道CMOS差分线接收器

MS90C031-LVDS 四通道总线驱动器数据手册

深入解析DS90C385A:高性能LVDS发射器的卓越之选

高压栅极驱动器LM5100A/B/C和LM5101A/B/C:设计与应用详解

深入解析DS90C032B LVDS Quad CMOS差分线接收器

解析DS90C031B LVDS Quad CMOS差分线驱动器

深入解析DS90CF366与DS90CF386:LVDS接收器的卓越之选

DS90CF366与DS90CF386:LVDS接收器的技术解析与应用指南

探索DS90C385A:高性能LVDS发射器的技术解析

探索DS90C383B:可编程LVDS发射器的卓越性能与应用

探索DS90C363B:高性能LVDS发射器的卓越之选

详解DS90C241与DS90C124:5 - 35MHz FPD - Link II串行器与解串器芯片组

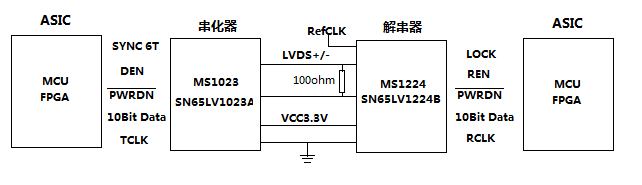

MS1023、SN65LV1023A串化器与MS1224、SN65LV1224B解串器应用

MS90C385B与MS90C386B功能特点及应用详解

MS90C385B与MS90C386B功能特点及应用详解

评论