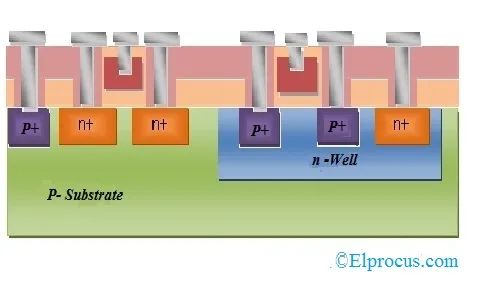

先从MOS管开始,如下图所示,是MOS管的横截面图。M-O-S管的全称称为Metal-Oxide-Semiconductor,即这三个字母,代表的是晶体管的结构,分别为金属栅极,薄氧化物绝缘体以及半导体沟道。

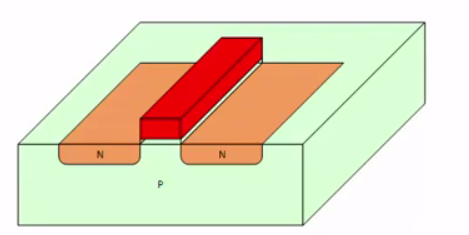

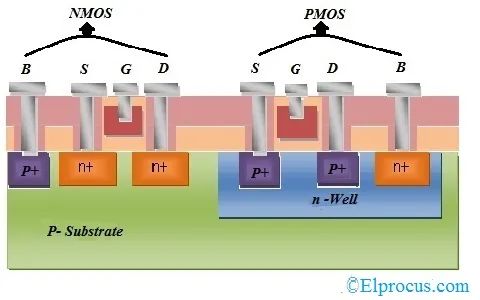

下图示NMOS晶体管。它在P型硅衬底中制造,具有重掺杂的源极、漏极。

早期的栅极是用金属制作的,但现在由导电的多晶硅取代。栅极位于一层薄薄的二氧化硅上,这是一种绝缘体。衬底,栅极,源极和漏极,通过金属端子与外界连接。

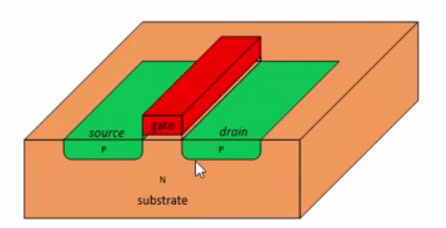

PMOS,是在N型硅衬底中制造,具有多晶硅栅极,P型源极和漏极,同样器栅极,源极和漏极以及衬底通过金属端子与外界连接。

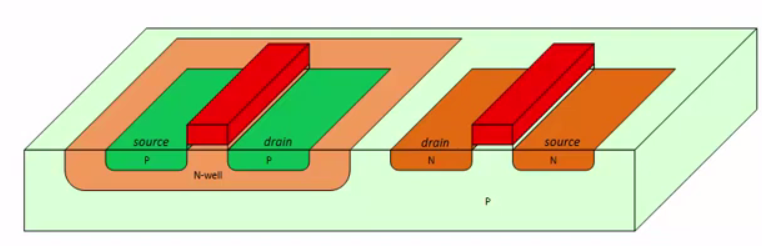

CMOS全称为 complementary MOS 。 在CMOS工艺中,在同一晶圆上,可以同时存在NMOS和PMOS,这样,给电路设计带来极大的便利。

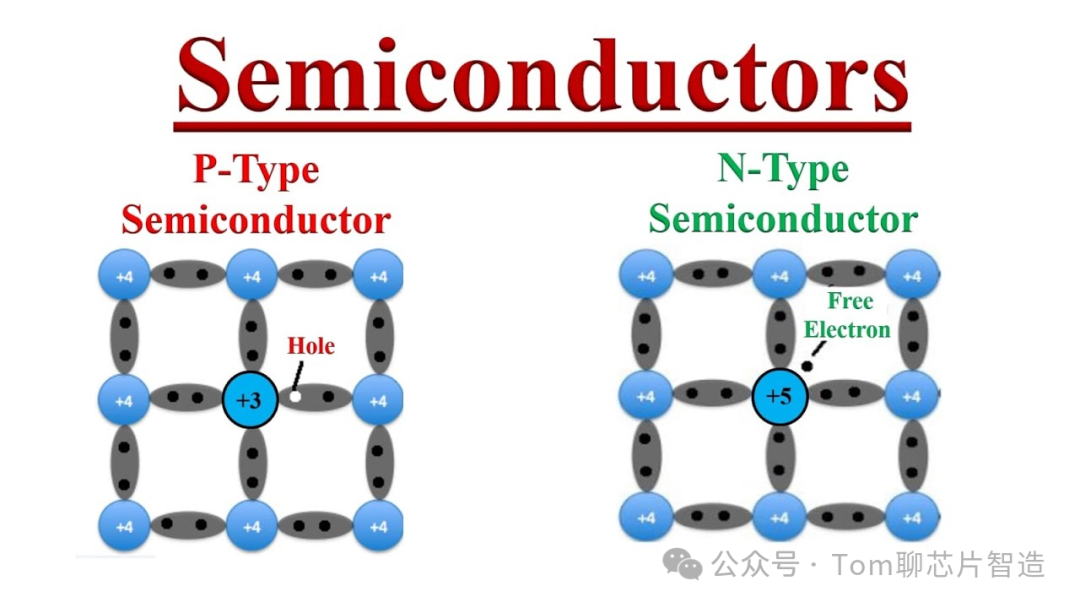

当使用晶圆来加工IC时,有两种掺杂形式的晶圆可以选择,分别为P型晶圆和N型晶圆。

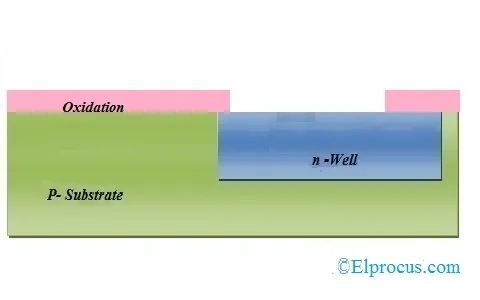

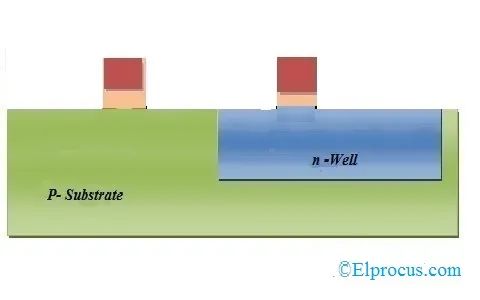

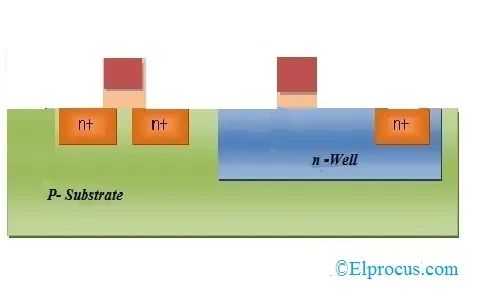

P型晶圆,可以用来制作NMOS; 但是PMOS需要的是N型衬底,怎么能在P型晶圆上实现呢?其实是采用N阱技术,PMOS管是在被称为N 阱的 N 型硅区域内制成的,如下图所示。

与 NMOS 和 BIPOLAR 技术相比,CMOS的主要优势是功耗要小得多。与 NMOS 或 BIPOLAR 电路不同,互补 MOS 电路几乎没有静态功耗。只有在电路实际切换的情况下才会消耗功率。这允许在 IC 上集成比 NMOS 或双极技术更多的 CMOS 门。

CMOS制造步骤和PCB加工也很类似,使用二十个基本制造步骤完成制造。以用N阱制作CMOS为例。

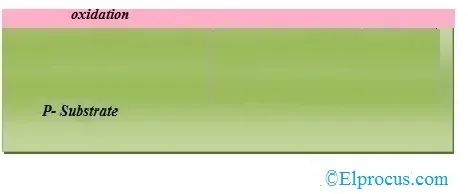

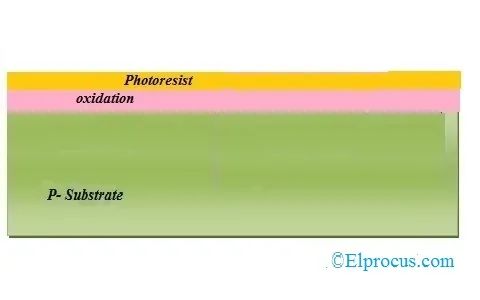

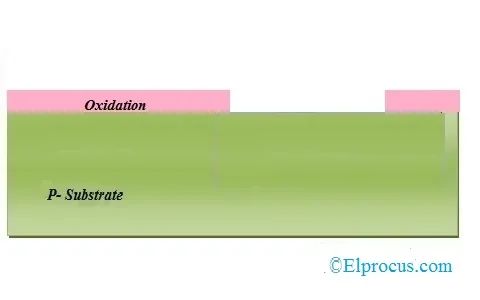

步骤 1:首先我们选择一个基板作为制造的基础。对于N-阱,选择P-型硅衬底。

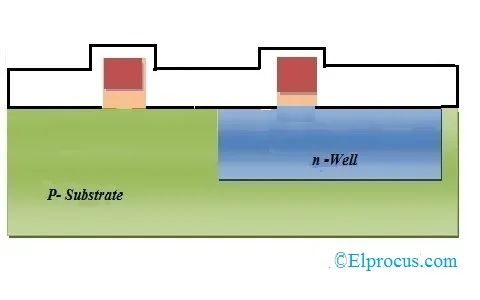

第 2 步 – 氧化:n 型杂质的选择性扩散是使用 SiO2 作为屏障来完成的,该屏障保护晶圆的某些部分免受基板的污染。

SiO 2是通过在大约 10000c的氧化室中将衬底暴露于高质量氧气和氢气的氧化工艺来布局的

第 3 步——光刻胶的生长:在这个阶段,为了进行选择性蚀刻,对 SiO2 层进行光刻工艺。在这个过程中,晶片被涂上一层均匀的感光乳剂膜。

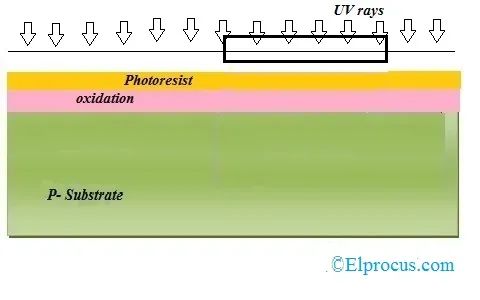

第 4 步 – 掩膜:此步骤是光刻工艺的延续。在此步骤中,使用模板制作所需的开放图案。该模板用作光刻胶上的掩模。衬底现在暴露于紫外线下,掩模暴露区域下的光刻胶被聚合。

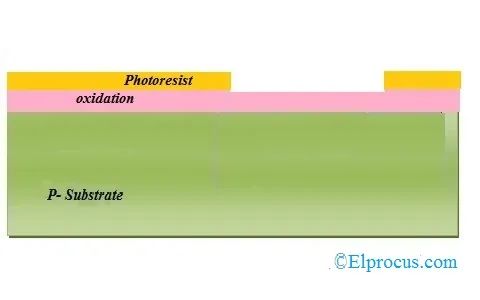

第 5 步 - 去除未曝光的光刻胶:去除掩模,并通过使用三氯乙烯等化学品显影晶片来溶解未曝光的光刻胶区域。

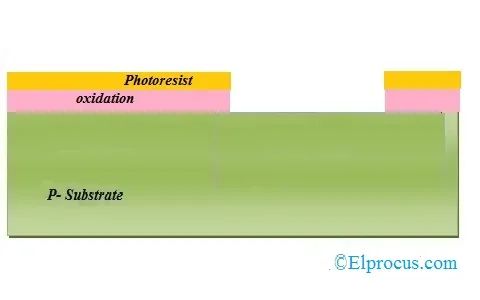

第 6 步 - 蚀刻:将晶片浸入氢氟酸蚀刻溶液中,去除掺杂剂扩散区域的氧化物。

第 7 步 – 去除整个光刻胶层:在蚀刻过程中,受光刻胶层保护的 SiO2 部分不受影响。现在用化学溶剂(热 H2SO4)剥离光刻胶掩模。

步骤 8 – N 阱的形成:n 型杂质通过暴露区域扩散到 p 型衬底中,从而形成 N 阱。

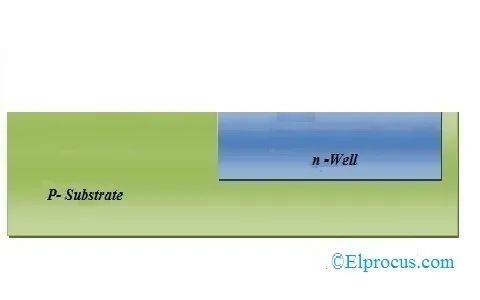

第 9 步 – 去除 SiO2:现在使用氢氟酸去除 SiO2 层。

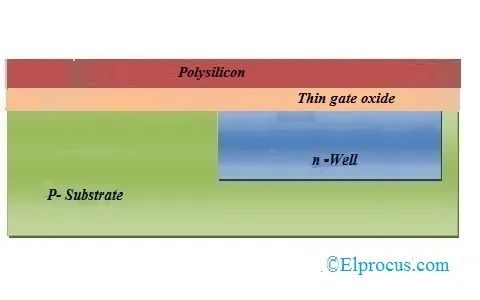

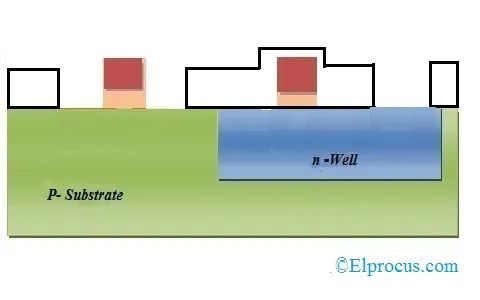

第 10 步 - 多晶硅沉积:CMOS 晶体管的栅极未对准会导致不需要的电容,从而损坏电路。因此,为了防止这种“自对准栅极工艺”,最好在使用离子注入形成源极和漏极之前形成栅极区域。

多晶硅用于栅极的形成是因为它可以承受大于80000℃的高温,当晶片经过退火方法形成源极和漏极时。多晶硅通过使用化学沉积工艺沉积在栅极氧化物薄层上。多晶硅层下方的这种薄栅极氧化物可防止栅极区域下方的进一步掺杂。 步骤 11 - 栅极区域的形成:除了为NMOS 和 PMOS 晶体管形成栅极所需的两个区域外,多晶硅的剩余部分被剥离。

第 12 步 – 氧化工艺:在晶圆上沉积一层氧化层,作为进一步扩散和金属化工艺的屏蔽层。

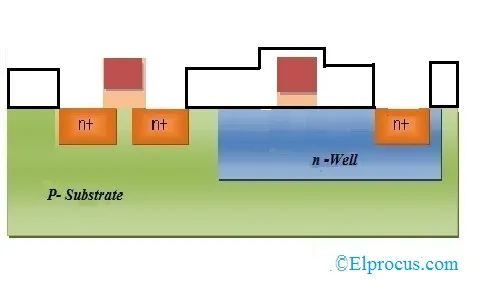

第 13 步 – 掩蔽和扩散:为了使用掩蔽工艺制作用于扩散 n 型杂质的区域,制作小间隙。

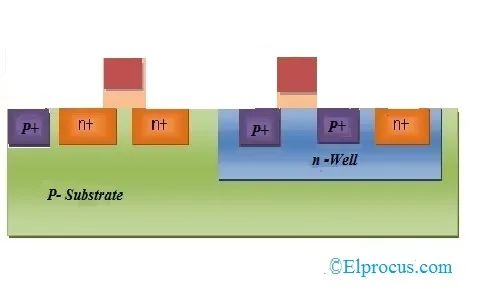

使用扩散工艺开发了三个 n+ 区域,用于形成 NMOS 的端子。

第 14 步 – 去除氧化物:剥去氧化层。

第 15 步 – P 型扩散:类似于用于形成 PMOS 的 p 型扩散端子的 n 型扩散。

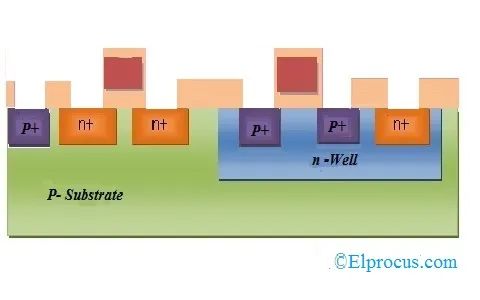

第 16 步 - 厚场氧化层的铺设:在形成金属端子之前,铺设厚场氧化层,以便为不需要端子的晶圆区域形成保护层。

步骤 17 – 金属化:此步骤用于形成可以提供互连的金属端子。铝被涂在整个晶片上。

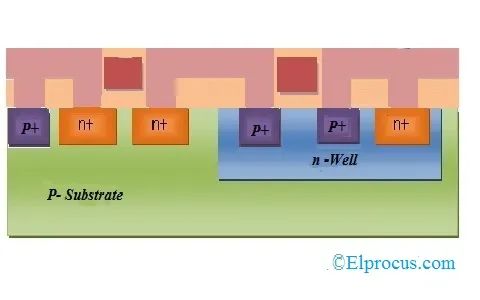

第 18 步 – 去除多余金属:从晶圆上去除多余的金属。 步骤 19 - 端子的形成:在去除多余金属端子后形成的间隙中,形成互连。

第 20 步 – 分配端子名称:为NMOS 和 PMOS 晶体管的端子分配名称。

审核编辑:刘清

-

CMOS

+关注

关注

58文章

6236浏览量

243436 -

MOS管

+关注

关注

111文章

2814浏览量

77930 -

PMOS

+关注

关注

4文章

274浏览量

31731

原文标题:CMOS技术

文章出处:【微信号:加油射频工程师,微信公众号:加油射频工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AFM Microelectronics射频微波MLCC领军制造商

芯片制造的步骤

“点沙成金”的科技奇迹:深入解读芯片制造三大阶段与五大步骤

芯片引脚成型与整形:电子制造中不可或缺的两种精密工艺

MES - 制造执行系统

干式变压器线圈制造详细步骤解析

下一代高速芯片晶体管解制造问题解决了!

CMOS图像传感器的制造步骤

使用二十个基本制造步骤完成CMOS制造

使用二十个基本制造步骤完成CMOS制造

评论