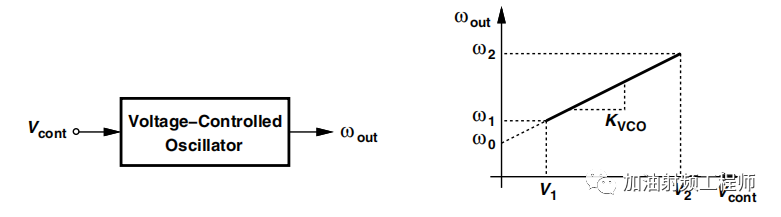

VCO是这样一个器件,当控制电压Vcont从V1变化到V2时,VCO的输出频率从w1变到w2,如下图所示.

其中,曲线的斜率称为Kvco,称为VCO的增益(gain)或者灵敏度(sensitivity),单位为rad/Hz/V。而且希望这个Kvco在整个调谐范围内变化不要太大。

用一个等式,表征VCO的这个特性,即为:

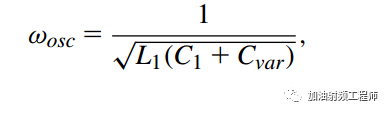

为了能够对LC振荡器的频率进行调谐,则LC谐振器的谐振频率需要改变。

想让电感随着电压变化是很难的,所以就考虑让电容随着电压变化。

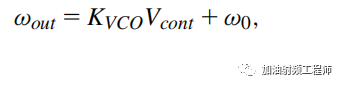

(1) 架构1

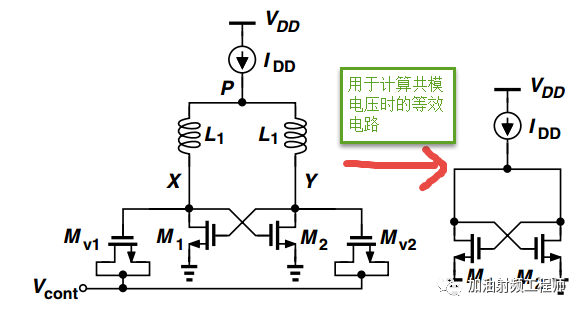

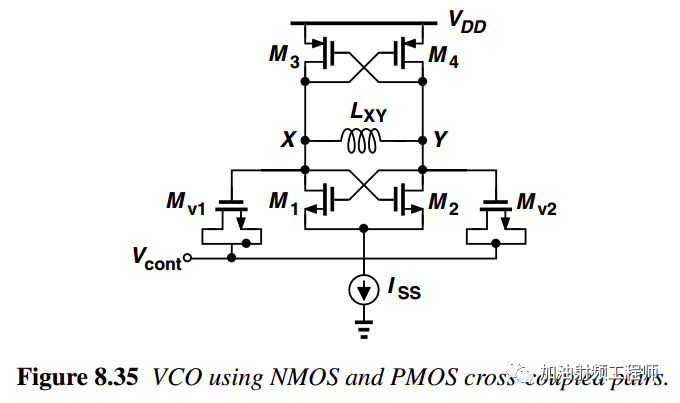

如下图所示的VCO架构,变容管Mv1和Mv2与谐振器并联。

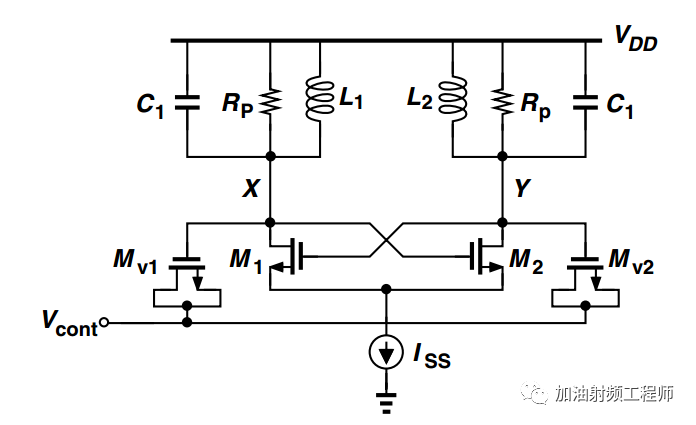

这边变容管的栅极与振荡器的结点(X和Y)相连,S/D极与Vcont连接。这样可以避免X/Y结点与变容管中n-well与substrate之间的电容连接。

这句话是什么意思呢?看一下下图,就知道了。

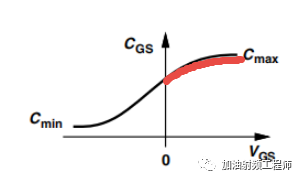

变容管Mv1和Mv2的栅极的平均电压为VDD。当Vcont从0V变化到VDD时,VGS从VDD变化到0,始终为正值。

所以变容管,在上述架构中,变化范围取正值的那一段。

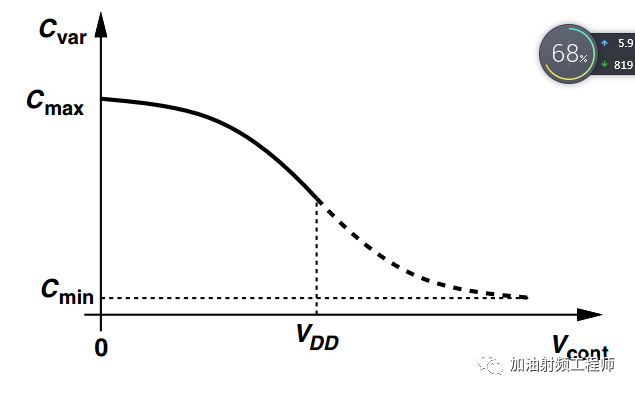

所以,当VGS从VDD变化为0时,即Vcont从0V变化到VDD时,变容管的容值从Cmax降为Cgs(vgs=0)。

此时,VCO的振荡频率可以由下式表示。

上述架构中的C1,虽然很想把它踢出去,因为它降低了VCO的频率调谐范围。

但是,对它无可奈何。这是因为,它代表的是管子M1和M2的寄生电容,电感的寄生电容,下一级的输入电容等。

为什么C1的存在会降低VCO的频率调谐范围呢?

一般Cvar都是C1的一小部分,所以假设一下,Cvar的变化范围为0.1C1~0.2C1,则此时频率的变化比值为1.04.

而如果没有C1的存在的话,则频率的变化范围为1.4。

但是上述架构中,有两个问题:

(1) 当Vcont接近于0V,而VX和VY的输出大于VDD,也就是处在正弦波的正半轴,此时变容管的Vgs要大于VDD,也就是说变容管处于一个过压的状态;

(2) 只用到了变容管一半的调谐范围,另一半被浪费了。

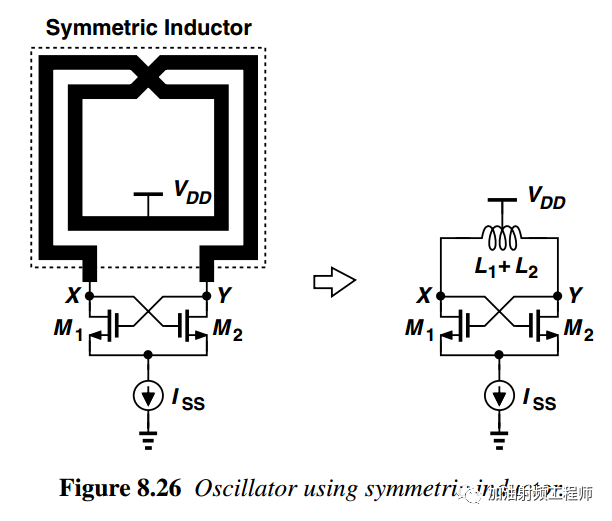

差分电感的Q值要优于单端电感,所以上述架构中的L1和L2可以用差分电感来实现。电感的对称点(中心抽头)与VDD两连。有时候进行电路分析时,为了简单起见,会省略中心抽头的连接。

(2) 架构2

上面讲到的架构中,变容管的调谐范围硬生生地被浪费掉了一半。那怎样才能把那一半也用起来呢。

改架构,让变容管两端的电压可正可负。

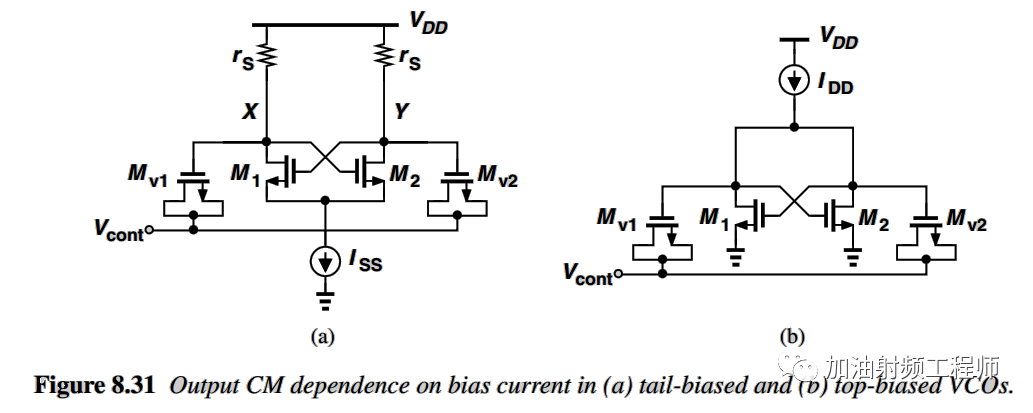

如下图所示,把尾电流源去掉,改用top电流源,就是把电流源放在管子的漏极端。

先计算X和Y结点处的共模电压,即无振荡时的直流电压。

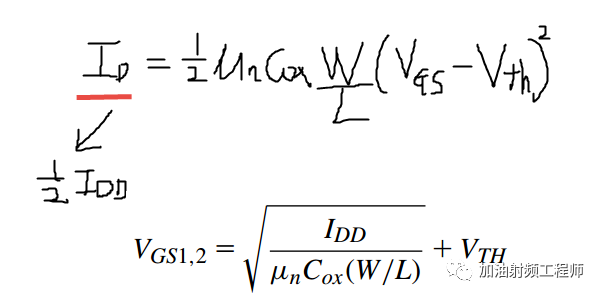

当不考虑交流,只考虑直流特性时,L1和L2短路,M1和M2完全对称,分摊电流源IDD,即每路的电流为IDD/2。

VGS>Vth,VGD=0

所以:

此时,可以选择合适的MOS管尺寸,使得X和Y结点的共模电压为VDD/2左右。这样,当变容管的调谐电压Vcont从0变化到VDD时,变容管两端的电压从VDD/2变化到-VDD/2,基本能够用上变容管的整个调谐范围。

把尾电流源改成顶电流源,虽然调谐范围变大,但是相噪也会恶化。

假设两种电流源的电流都变化△I。

对于尾电流源而言,由于X和Y结点直接通过电感与VDD相连,而电感的ESR很小,假设为rs,则 △VCM=(△I/2)rs.

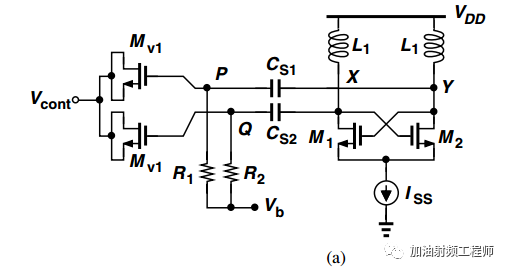

对于顶电流源而言,为△VCM=(△I/2)(1/gm)。这由MOS管工作在饱和区时的小信号模型公式△I=gm△Vgs得到的。而1/gm>>rs,所以当电流源有噪声时,当其作为尾电流源时,对VCO整体相噪的影响小。(3) 架构3那如果又想要大的调谐范围,又想避免顶电流源对VCO相噪的影响,怎么弄呢?仍然延用尾电流源的架构,但是将变容管与X和Y结点之间通过电容隔开。如下图所示,并将图中Vb的电压设置为VDD/2,使得变容管两端的电压的变化范围为-VDD/2~VDD/2。

但是交流耦合电容的寄生参数会对VCO的性能产生影响,而且,Cs1和Cs2的值必须远大于Cmax(变容管能调谐到的最大电容),否则还是会减小调谐范围。

另外,此种架构还有三点需要注意:

(1) R 1和R2 近似与谐振网络并联,所以其值的选择需要远大于Rp(tank的寄生电阻)

(2) Vb的噪声也会对变容管两端的电压产生影响,所以需要减小Vb的噪声

(3) R1和R2的噪声也会变容管两端的电压产生影响,进而影响VCO的相噪

(4) 架构4

另外一种使得CM输出电压为VDD/2的架构,如下图所示。

这种架构,是联合采用了交叉耦合NMOS对和交叉耦合PMOS对。

合理选择MOS管的尺寸,可以使得X和Y结点的共模电压为VDD/2,从而最大化调谐范围。

而且,这种架构还有一个重要的优点,就是在相同的偏置电流和电感设计下,其电压幅度输出是单纯的尾电流源架构的2倍。

不过这种架构也有缺点:

(1) 为了使得|VGS3|+VGS1+VISS=VDD,PMOS管必须很宽,则就会相当大的电容,从而限制调谐范围

(2) 尾电流源的噪声会影响共模输出电压,进而影响变容管的电容。

审核编辑:汤梓红

-

CMOS

+关注

关注

58文章

6233浏览量

243407 -

振荡器

+关注

关注

28文章

4192浏览量

143170 -

VCO

+关注

关注

14文章

321浏览量

71443

原文标题:CMOS VCO的架构

文章出处:【微信号:加油射频工程师,微信公众号:加油射频工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

VCO的架构设计

VCO的架构设计

评论