控制类寄存器2种实现方式

在数据处理过程中,需要一些可配置的寄存器,用于控制数据处理过程中的行为,如果各类处理信号的使能信号,还有功能模块的特定控制信号。

例如:在ETH处理过程中,有数据流使能控制,最大包长度控制信号。

例如:在PCIE中,存在bus master enable信号,max payload size等控制信号。

那么这类可配置的控制类寄存器是如何在数据处理过程中起作用的呢?有哪些实现方式呢?

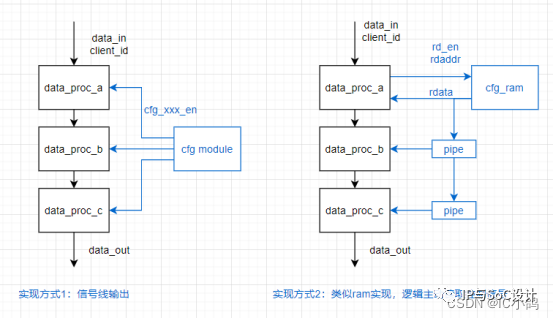

下图所示,data_in为输入数据,data_out是处理后的数据,处理过程中data_proc_a/b/c需要用到控制寄存器对处理进行处理,client_id表示data的id号,模块采用时分复用的方式处理不同id的data。

实现方式1: 寄存器信号线输出

通过寄存器信号线的方式输出给需要的模块,如图方式1,cfg module把所有的控制信号都暴露出来,送给需要的模块data_proc_a/b/c,data有效时,根据client_id选择需要的控制信号。

优点:

-此类设计简单,容易理解与实现。

-此设计限制小,可以用于各类情况下的设计

缺点:

-控制信号线较多,高频设计不利于布局布线

-不利于规模扩展,例如client_id数量从8增加到16,需要修改大量的代码。

此设计中,控制寄存器以ram(或者类似)的方式实现,数据处理模块data_proc_a主动读取控制信号,当有效数据来临时,以client_id作为rdaddr读取,一次读取处理流程中所需的控制信号(rdata),进行数据处理,并且将控制信号(rdata)进行pipe与data对齐,提供给后期模块data_proc_b/c

优点:

-规模扩展方便,例如client_id数量从8增加到16,仅限cfg_ram的规模修改,data_proc_a/b/c仅仅需要修改client_id位宽参数。

-控制信号线较少,有利于时序优化和布局布线

缺点:

-此设计适用于数据的pipeline处理,并且ram读出存在一定的读延时,存在一定限制。

一种主动的流控实现方式

1、流控机制

在数据发送过程中,发送者向接收者发送数据,通常需要接收者通知发送者自身是否可以接收数据,当接收者即将无法接收数据时(如FIFO快满时),发送者需要停止发送数据,这就是流控机制。

2、流控机制过程

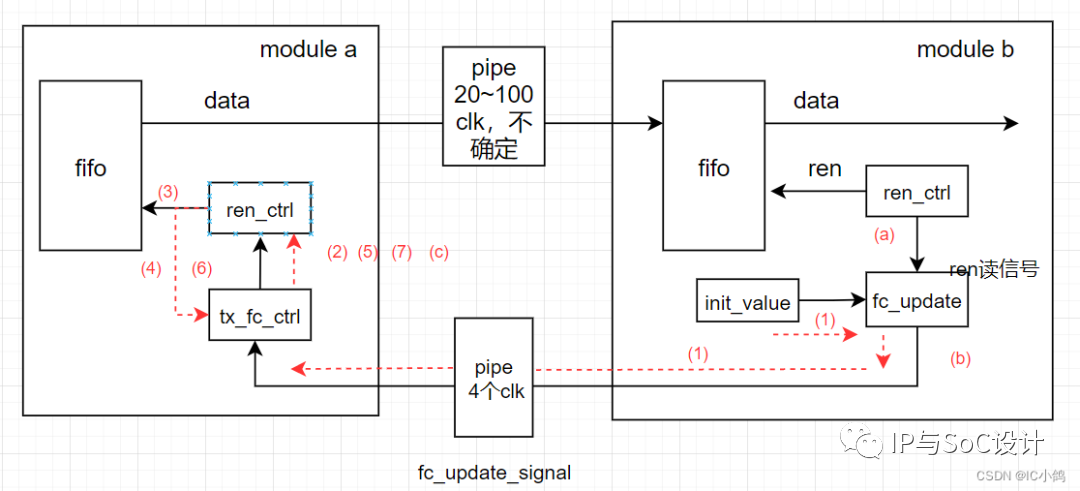

初始化流程:

(1)复位释放后,初始化,module b 通过信号fc_update_signal 通知module a 自身fifo深度是多少

(2)Tx_fc_ctrl 收到初始化信息后,得知module b存在有效fifo 缓存,通知ren_ctrl允许产生读使能ren

(3)ren_ctrl产生读使能ren

(4)ren输出给tx_fc_ctrl,module b的有效fifo深度减一

(5)tx_fc_ctrl计算module b是否存在有效数据,有则允许ren_ctrl产生读使能

(6)ren_ctrl产生读使能ren,并通知到tx_fc_ctrl,module b的有效fifo深度减一

(7)tx_fc_ctrl计算module b是否存在有效数据,有则允许ren_ctrl产生读使能,没有则不允许ren_ctrl产生读使能

(a)Module b模块fifo已存在有效数据,从fifo读取一个数据,此时已释放出一个fifo深度

(b)Fc_update更新fc_update_signal,通知tx_fc_ctrl模块module b已释放一个fifo空间,tx_fc_ctrl记录的有效深度加1

(c)此时tx_fc_ctrl允许ren_ctrl产生读使能

3、特点说明

此种流控机制需要发送端和接收端配合管理有效缓存空间。相对比单一bit的flow ctrl信号来说,稍微复杂一些,但是有个显著的优点,相对于被动流控机制(见IC设计高级006:流控反压机制导致的路径延时),能够有效减少module b中的Data fifo的深度。

如图,data pipeline的深度是不确定的,可能是20~100个周期,而流控信号只有4个pipe,在考虑其他方面的延时有3拍,

不考虑性能的情况下:保证不溢出,module b的fifo深度最小需要:

本文流控机制:深度为1 ; 被动流控机制:深度为1+100+4+3

满足最大性能的情况下,保证下游不断流:module b的fifo深度需要:

本文流控机制:100+4+3+1 ; 被动流控机制:2*(100+4+3+1)

审核编辑 :李倩

-

寄存器

+关注

关注

31文章

5620浏览量

130450 -

控制信号

+关注

关注

0文章

200浏览量

12728

原文标题:IC设计知识点:控制类寄存器两种实现方式等

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

ICSSSTUB32866B:DDR2可配置寄存器缓冲器的技术解析

深入解析IDT74SSTUBH32865A:DDR2的28位1:2寄存器缓冲器

解读 IDT74SSTUBF32868A:DDR2 应用的 28 位可配置寄存器缓冲器

74AHC594:8位移位寄存器的详细解析与应用

74LV595A:8位移位寄存器的全方位解析

深入解析CY74FCT399T:一款高性能的四2输入寄存器

探索IDT74SSTUBF32866B:DDR2的25位可配置寄存器缓冲器

探索IDT74SSTUBF32866B:DDR2的25位可配置寄存器缓冲器

蜂鸟内核中DMA的硬件实现——寄存器配置

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析2

SN74HCT595 8位移位寄存器技术解析与应用指南

SN74LV594A:2-5.5V带输出寄存器的8位移位寄存器技术解析

使用寄存器点亮LED灯

第四章 什么是寄存器

控制类寄存器2种实现方式

控制类寄存器2种实现方式

评论