电子发烧友网报道(文/周凯扬)对于汽车电子产品来说,开发周期长车规认证麻烦已经是业界共识了,这意味着RISC-V也不例外,哪怕这个ISA正在以迅雷不及掩耳之势渗透进各个行业中。

基于RISC-V的车规芯片必须经过AEC-Q100的可靠性认证,如果是汽车网关之类的芯片还得过ISO/SAE 21434的网络安全认证。RISC-V IP本身也必须通过ISO 26262的功能安全认证,软件上要想直接完成平台兼容也必须符合AUTOSAR的规范。

在ISO26262规范中,控制网关、座舱和一些简单传感器的芯片IP往往需要过ASIL-B的认证,而实现ADAS、电池管理和与动力控制等复杂功能的芯片IP则需要更高的ASIL-D认证。与此同时,随着汽车架构从Domain架构慢慢转向计算集中的Zone架构迁移,汽车芯片的算力也在提升,因此RISC-V IP核在性能上也不能马虎。

以上要求可以看出,车规芯片的设计有多么烦琐,打造一款RISC-V车规芯片的第一步,就是选择或设计一款功能安全合规的RISC-V IP。好在RISC-V上车的进程已经提速,不少厂商都已经准备或布局了ISO 26262的处理器IP,帮助IC设计公司解决随机硬件失效、系统失效等安全问题。

晶心科技

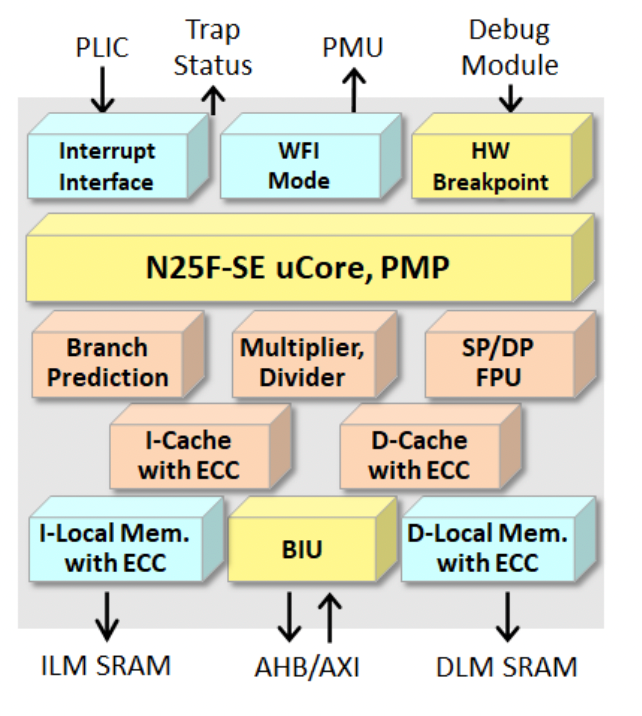

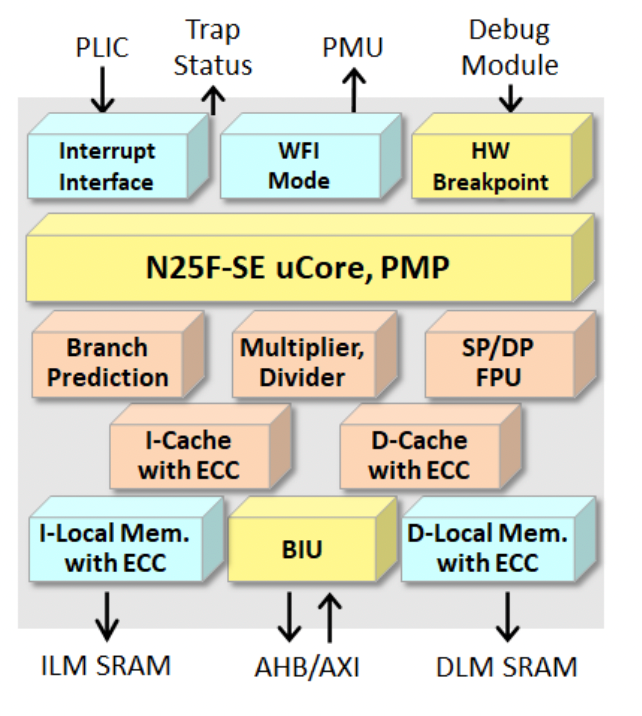

晶心科技的N25F-SE就是这样一款汽车功能安全IP核心,预计今年上半年完成ISO 26262 ASIL-B认证。该IP基于晶心自己的AndeStar V5指令集架构(兼容RISC-V),并采用了32位、5级流水线的设计,集成了单浮点精度/双浮点精度的FPU,指令缓存和数据缓存最高32KB,指令和数据本地内存最高可达16MB。

N25F-SE可以看做是N25F的功能安全加强版,引入了不少安全机制。比如利用基于SECDED的ECC内存保护机制来杜绝数据损坏,在软件上强制实施特权与访问规则来保护物理内存,以及自动检测栈溢出的StackSafe机制等等。

N25F-SE原理图 / 晶心科技

晶心科技也为其N25F-SE IP在车规上的诸多应用场景做了构想,比如舱内毫米波雷达系统。N25F-SE既控制雷达子系统,又作为主机控制器,用于舱内存在监控系统,通过检测人体的头部运动和身体语言来判断驾驶员的疲劳状态。此外,N25F-SE也可用于中控的触控与显示驱动芯片(TDDI)或是汽车MCU等。

芯来科技

芯来除了有着N、NX和UX这一系列完整的商业级IP产品线以外,也在ASIL-B和ASIL-D车规功能安全上做了一些安全机制的实现,比如利用软件自测试检测硬件故障,在ILM、DLC、I-Cache和系统总线上实现ECC纠错和奇偶校验保护,以及延迟双核锁步的冗余设计等等。

N900发动机ECU主控(ASIL-D等级)设计方案 / 芯来科技

芯来计划在今年Q3到Q4左右完成NA900(32位)的ASIL-D认证,并在今年启动NA900(32位/64位)和NA300(32位)的ASIL-B认证流程,明年启动NA300(32位)的ASIL-D认证流程。其中300系列为3流水线单发射,900系列为9级流水线双发射的,通过认证后,NA900可以说是目前的车规RISC-V IP中性能最高的了。

NSITEXE

日本也有一个专注于设计与开发RISC-V IP的公司,那就是日本电装的全资子公司NSITEXE。要说RISC-V车规产品商用化最快的厂商,还得是他们,NSITEXE的RISC-V协处理器IP DR1000C早就在去年授权给了瑞萨,并用于瑞萨的汽车MCU RH850/U2B。

DR1000C在该MCU内主要作为矢量扩展,卸载一些计算处理任务来减轻负担,比如AI推理、传感器数据处理等等,其本身已经通过了ISO 26262的ASIL-D认证。不过NSITEXE倒也不想局限于DR系列的数据流处理器,毕竟这类处理器主要还是在汽车MCU中作为辅助计算单元,于是也开始推出RISC-V的车规CPU IP方案,比如NS31A。

NS31A原理图 / NSITEXE

NS31A是一款通用RISC-V CPU,基于32位RV32IMAF的架构,采用了单发射、4级流水线的设计,可选单浮点精度的FPU。NS31A的指令集缓存大小最高32KB,指令本地内存最高512KB,数据本地内存最高512KB。在功能安全上,NS31A同样集成了存储ECC纠错、双核锁步架构等机制,而且还支持AUTOSAR平台所需的特权模式。

设计与验证

对于这些RISC-V IP设计公司来说,即便其工程师有着资深的汽车市场开发经验,在走向车规认证的道路上,也有不少需要克服的坎,这也就是为何他们不少都选择了与工具厂商合作,尤其是帮助他们完成开发和验证工作的EDA厂商,比如新思、Imperas、IAR Systems等等,毕竟这些厂商早在其他ISA的车规认证上就已经积累了不少功能安全验证经验和故障模型集,而且这些工具本身也有通过功能安全认证。

由此看来,RISC-V也算是享受到了这些红利,能以最快的速度切入汽车这类关键任务的应用。除此之外还有航天航空的DO-254/172、工业的IEC 61511/61513、医疗的IEC 62304、机器人的IEC 62061、ISO13849等等标准。这也是RISC-V作为后起之秀的优势所在,前人走过的老路可以再走一遍,而前人犯过的错却可以规避。

比如过去的设计思路是等到起量后再为已有的核心添加安全机制,然后走功能安全认证,但现在的IP核从设计之初就可以考虑功能安全,是和PPA一样关键的参数。在购买这些通过认证的IP后,除了RTL,IP厂商也会给到一个功能安全包,其中涵盖了安全手册、安全分析报告等文档,辅助使用者在功能安全性上的开发设计。

写在最后

综上所述,国内公司在设计汽车芯片时不妨考虑下RISC-V,毕竟目前RISC-V IP的车规已经纷纷提上日程,接下来就看车规芯片厂商的动作了。固然车规芯片的替代是一个艰巨的任务,且不用说ISA架构,就连替代国外厂商都是一个耗时耗力的过程。但就国内市场而言,目前自己设计RISC-V IP没有ARM那样高额的授权费用,商用IP已经提供了足够的优势,也没有潜在的IP产权风险,或许是时候将目光看向RISC-V了。至于RISC-V IP厂商们也还有更大的发展空间,比如车机系统的适配、更高的图形性能、做好虚拟化和软件隔离等等,真正释放RISC-V在汽车上的潜力。

基于RISC-V的车规芯片必须经过AEC-Q100的可靠性认证,如果是汽车网关之类的芯片还得过ISO/SAE 21434的网络安全认证。RISC-V IP本身也必须通过ISO 26262的功能安全认证,软件上要想直接完成平台兼容也必须符合AUTOSAR的规范。

在ISO26262规范中,控制网关、座舱和一些简单传感器的芯片IP往往需要过ASIL-B的认证,而实现ADAS、电池管理和与动力控制等复杂功能的芯片IP则需要更高的ASIL-D认证。与此同时,随着汽车架构从Domain架构慢慢转向计算集中的Zone架构迁移,汽车芯片的算力也在提升,因此RISC-V IP核在性能上也不能马虎。

以上要求可以看出,车规芯片的设计有多么烦琐,打造一款RISC-V车规芯片的第一步,就是选择或设计一款功能安全合规的RISC-V IP。好在RISC-V上车的进程已经提速,不少厂商都已经准备或布局了ISO 26262的处理器IP,帮助IC设计公司解决随机硬件失效、系统失效等安全问题。

晶心科技

晶心科技的N25F-SE就是这样一款汽车功能安全IP核心,预计今年上半年完成ISO 26262 ASIL-B认证。该IP基于晶心自己的AndeStar V5指令集架构(兼容RISC-V),并采用了32位、5级流水线的设计,集成了单浮点精度/双浮点精度的FPU,指令缓存和数据缓存最高32KB,指令和数据本地内存最高可达16MB。

N25F-SE可以看做是N25F的功能安全加强版,引入了不少安全机制。比如利用基于SECDED的ECC内存保护机制来杜绝数据损坏,在软件上强制实施特权与访问规则来保护物理内存,以及自动检测栈溢出的StackSafe机制等等。

N25F-SE原理图 / 晶心科技

晶心科技也为其N25F-SE IP在车规上的诸多应用场景做了构想,比如舱内毫米波雷达系统。N25F-SE既控制雷达子系统,又作为主机控制器,用于舱内存在监控系统,通过检测人体的头部运动和身体语言来判断驾驶员的疲劳状态。此外,N25F-SE也可用于中控的触控与显示驱动芯片(TDDI)或是汽车MCU等。

芯来科技

芯来除了有着N、NX和UX这一系列完整的商业级IP产品线以外,也在ASIL-B和ASIL-D车规功能安全上做了一些安全机制的实现,比如利用软件自测试检测硬件故障,在ILM、DLC、I-Cache和系统总线上实现ECC纠错和奇偶校验保护,以及延迟双核锁步的冗余设计等等。

N900发动机ECU主控(ASIL-D等级)设计方案 / 芯来科技

芯来计划在今年Q3到Q4左右完成NA900(32位)的ASIL-D认证,并在今年启动NA900(32位/64位)和NA300(32位)的ASIL-B认证流程,明年启动NA300(32位)的ASIL-D认证流程。其中300系列为3流水线单发射,900系列为9级流水线双发射的,通过认证后,NA900可以说是目前的车规RISC-V IP中性能最高的了。

NSITEXE

日本也有一个专注于设计与开发RISC-V IP的公司,那就是日本电装的全资子公司NSITEXE。要说RISC-V车规产品商用化最快的厂商,还得是他们,NSITEXE的RISC-V协处理器IP DR1000C早就在去年授权给了瑞萨,并用于瑞萨的汽车MCU RH850/U2B。

DR1000C在该MCU内主要作为矢量扩展,卸载一些计算处理任务来减轻负担,比如AI推理、传感器数据处理等等,其本身已经通过了ISO 26262的ASIL-D认证。不过NSITEXE倒也不想局限于DR系列的数据流处理器,毕竟这类处理器主要还是在汽车MCU中作为辅助计算单元,于是也开始推出RISC-V的车规CPU IP方案,比如NS31A。

NS31A原理图 / NSITEXE

设计与验证

对于这些RISC-V IP设计公司来说,即便其工程师有着资深的汽车市场开发经验,在走向车规认证的道路上,也有不少需要克服的坎,这也就是为何他们不少都选择了与工具厂商合作,尤其是帮助他们完成开发和验证工作的EDA厂商,比如新思、Imperas、IAR Systems等等,毕竟这些厂商早在其他ISA的车规认证上就已经积累了不少功能安全验证经验和故障模型集,而且这些工具本身也有通过功能安全认证。

由此看来,RISC-V也算是享受到了这些红利,能以最快的速度切入汽车这类关键任务的应用。除此之外还有航天航空的DO-254/172、工业的IEC 61511/61513、医疗的IEC 62304、机器人的IEC 62061、ISO13849等等标准。这也是RISC-V作为后起之秀的优势所在,前人走过的老路可以再走一遍,而前人犯过的错却可以规避。

比如过去的设计思路是等到起量后再为已有的核心添加安全机制,然后走功能安全认证,但现在的IP核从设计之初就可以考虑功能安全,是和PPA一样关键的参数。在购买这些通过认证的IP后,除了RTL,IP厂商也会给到一个功能安全包,其中涵盖了安全手册、安全分析报告等文档,辅助使用者在功能安全性上的开发设计。

写在最后

综上所述,国内公司在设计汽车芯片时不妨考虑下RISC-V,毕竟目前RISC-V IP的车规已经纷纷提上日程,接下来就看车规芯片厂商的动作了。固然车规芯片的替代是一个艰巨的任务,且不用说ISA架构,就连替代国外厂商都是一个耗时耗力的过程。但就国内市场而言,目前自己设计RISC-V IP没有ARM那样高额的授权费用,商用IP已经提供了足够的优势,也没有潜在的IP产权风险,或许是时候将目光看向RISC-V了。至于RISC-V IP厂商们也还有更大的发展空间,比如车机系统的适配、更高的图形性能、做好虚拟化和软件隔离等等,真正释放RISC-V在汽车上的潜力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RISC-V

+关注

关注

49文章

2976浏览量

53645

发布评论请先 登录

相关推荐

热点推荐

中国汽车芯片产业创新战略联盟RISC-V车规芯片专委会正式成立

2026 年 4 月 26 日,中国汽车芯片产业创新战略联盟 RISC-V车规芯片专委会在北京车展中国芯展区正式成立。专委会汇聚汽车及汽车电子、芯片设计、IP、软件工具链、制造、测试认

你的RISC-V芯片,合规吗?

本文转自:半导体行业观察验证涉及多个学科,每个学科都至关重要,而且都变得日益复杂。RISC-V又增加了一个学科——架构一致性——直到最近,这方面的研究还只是少数几家公司在私下进行。采用RISC-V

新思科技STING助力破局RISC-V架构验证复杂度

RISC-V 指令集因其开源、模块化设计特点,以及在嵌入式设备、人工智能、车规 MCU、边缘计算和数据中心等多种应用领域的广泛适用性而日益普及,以前所未有的速度迈向主流商业化。随着

新思科技ARC-V处理器驱动RISC-V市场无限机遇

,RISC-V 发展得极快。据咨询公司 The SHD Group 在 2025 北美 RISC-V 峰会上发布的报告中给出的市场增长预测,到 2031 年,RISC-V 芯片出货量将突破 200 亿颗,

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

据科技区角报道半导体解决方案提供商 Quintauris 最近宣布和 RISC-V 处理器 IP 领域的头部厂商 SiFive 达成战略合作,目标直接瞄准加速 RISC-V 在嵌入式、AI 系统等

发表于 12-18 12:01

新思科技全栈工具链助力RISC-V设计高效进阶

在RISC-V 架构席卷全球的当下,新思科技(Synopsys)通过在整个硅生命周期开发工具、验证平台与定制 IP 方面的深厚积累,成为 RISC-V 生态中最为关键的“隐形推手”,在整个 R

喜讯|昊芯RISC-V DSP荣获“中国芯”RISC-V生态推广奖

11月14日,2025“中国芯”集成电路产业促进大会暨第二十届“中国芯”优秀产品征集评选结果在珠海横琴正式揭晓。昊芯车规级RISC-VDSP芯片F280025凭借在汽车及工业领域的创新突破与生态建设

为什么RISC-V是嵌入式应用的最佳选择

最近RISC-V基金会在社交媒体上发文,文章说物联网和嵌入式系统正在迅速发展,需要更高的计算性能、更低的功耗和人工智能。RISC-V是为未来而建的,包括超高效的MCU到高性能应用处理器,RISC-V使开发人员能够设计以下解决方案

兆松科技ZCC-FuSa编译器全面支持晶心科技车规级RISC-V处理器IP核

2025 年 8 月 26 日,兆松科技宣布其车规编译器 ZCC-FuSa 全面支持 Andes 晶心科技各系列车规级的 AndesCore RISC-V CPU

RISC-V 手册

以下是关于RISC-V的详细介绍,结合其核心技术特点与当前发展现状:核心概念RISC-V(第五代精简指令集)是一种基于精简指令集(RISC)的开源指令集架构(ISA),由加州大学伯克利分校于2010

发表于 07-28 16:27

•11次下载

2025新思科技RISC-V科技日活动圆满结束

新思科技深度参与2025 RISC-V中国峰会并于2025年7月16日举办同期活动“新思科技RISC-V科技日”技术论坛,聚焦“从芯片到系统重构RISC-V创新”主题,议题覆盖当前最前沿的技术领域

IAR携手矽力杰与普华基础软件加速RISC-V车规芯片发展

IAR嵌入式开发解决方案现已全面支持矽力杰SA32B系列和即将量产的SA32D系列车规级MCU,其中SA32D系列作为基于RISC-V架构的高功能安全等级(ASIL D)芯片,正成为国产车规

RISC-V 服务器标准化之路:固件安全与接口规范的探索

服务器标准化之路” 展开了深入分享,从多个关键技术领域和实践探索方面,为大家呈现了 RISC-V 服务器发展的现状与未来方向。 刘振首先介绍了当前 RISC-V 服务器相关标准的制定

发表于 07-18 14:05

•5207次阅读

RISC-V如何盈利?本土企业率先破局

了全行业对RISC-V美好未来的信心。 RISC-V崛起:芯片产业高质量发展的必由之路 当前,全球两大处理器架构中,x86完全封闭,Arm需付费购买。关键技术被境外垄断,相关芯片也依赖境外的生态和软件,使国内供应链面临着巨大的风

RISC-V车规芯片加速 芯来NA900汽车电子客户矽力杰与普华达成战略合作

可靠的车规级芯片与软件解决方案,助力车企和零部件供应商快速响应智能网联新需求的同时,实现降本增效的目的,为车企应对智能化挑战提供强有力的技术支持。至此,

RISC-V IP的车规之路

RISC-V IP的车规之路

评论