全局综合(Global Synthesis)

全局综合意味着整个设计在一个Synthesis Design Run流程中完成,这样会带来几个好处。一是使得综合工具能够最大化地进行设计优化,尤其是层次间的优化(这些优化是其他综合流程不能实现的)。二是对于综合后的设计分析带来了很大的便利。当然,其不足之处也是很明显的,那就是编译时间会很长。但这一不足之处可以借助增量综合得以缓解。需要注意的是因为是全局综合,所以XDC中描述的约束是以顶层为基准进行索引的。

IPI综合(Block Design Synthesis)

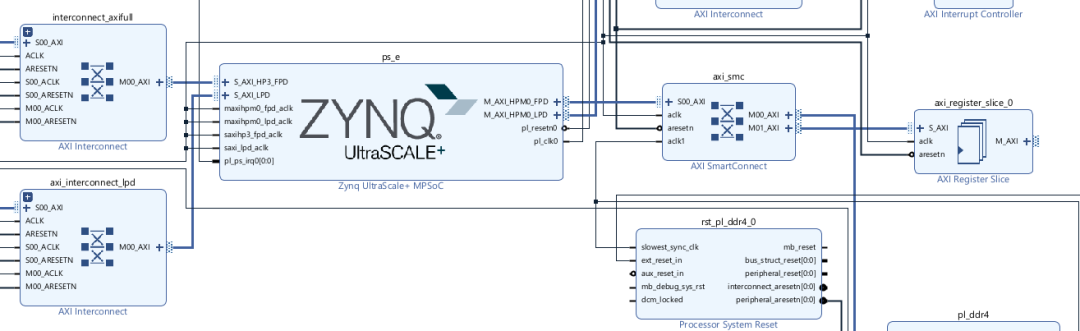

Vivado IPI (IP Integrator)提供了直观的模块化的设计方法。用户可以将Vivado IP Catalog中的IP、用户自己的RTL代码、或者用户已有的BD文件添加到IP Integrator中构成Block Design,设计更复杂的系统,如下图所示。

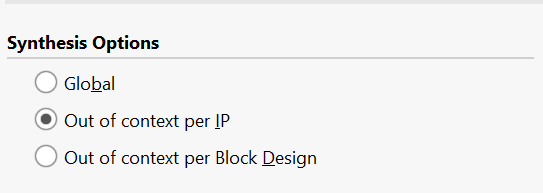

IPI使得用户可以方便地将特定功能打包放入设计中,这样用户可以将焦点放在整个系统上,而非系统的某个部分。对于Block Design,Vivado提供了如下图所示的三种综合方式。其中Global为全局综合方式,其余两种均为OOC(Out-of-Context)综合方式,只是OOC的粒度不同而已。OOC可以有效缩短编译时间。

OOC综合方式

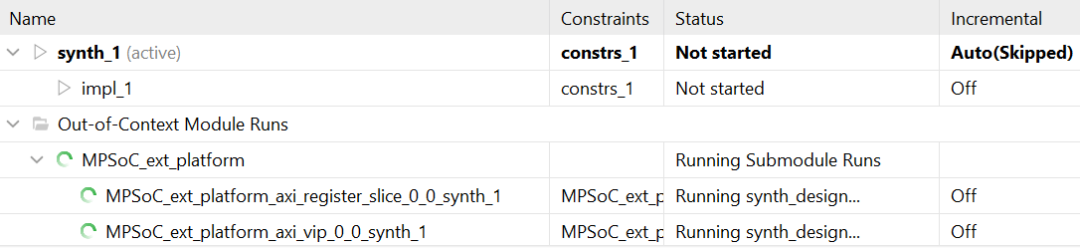

OOC综合方式可以使用户单独对设计的某个层次进行综合,然后再对整个设计进行综合,此时,OOC综合的对象会被当作黑盒子对待。通常,对于Xilinx的IP,我们建议采用OOC综合方式。OOC可以缩短后续整个设计综合所需时间,同时,若设计发生改变,而OOC综合对象没有改变,那么整个设计的综合就不需要再对OOC对象进行综合。一旦采用OOC综合方式,在Design Runs窗口中就会看到相应的OOC Module Runs,如下图所示。

增量综合(Incremental Synthesis)

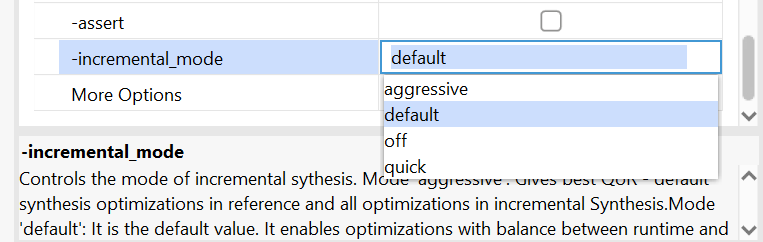

增量综合可以使综合工具复用之前已有的综合结果,从而缩短编译时间。但增量综合是有前提条件的,即设计可以形成至少4个分割(Partitions),而每个分割至少包含25000个模块。这里的“模块”既包含设计层次也包含RTL原语。Vivado提供了四种增量综合模式,如下图所示。其中off表明关闭增量综合,quick模式不会进行边界优化。default模式会执行大部分逻辑优化包括边界优化,相对于非增量模式,能显著缩短编译时间。aggressive模式会执行所有的逻辑优化,编译时间缩短程度最为明显。对于低性能设计需求,可以使用quick模式,而对于高性能设计需求,建议采用其余三种模式。

模块化综合(Block-level Synthesis)

本身Vivado提供了多种综合策略和各种综合设置选项,但其面向的对象是整个设计,换言之,这是一种全局设置。Block-level综合技术则打破了这一常规,可以对不同层次的设计设置不同的选项或应用不同的综合策略,从而达到更好的综合质量。

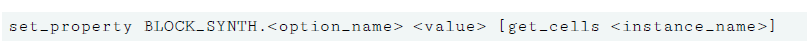

Block-level综合技术需要通过XDC约束来实现,如下图所示。

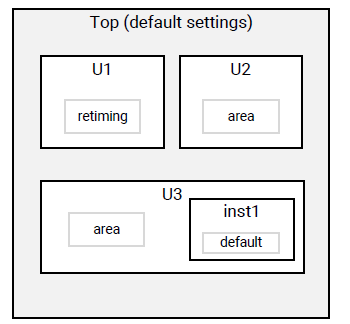

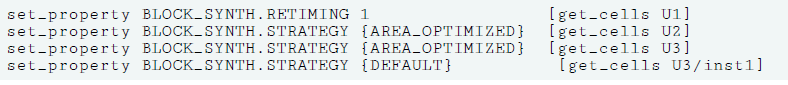

我们来看一个例子:设计中有4个模块U1、U2、U3和inst1,而inst1又嵌入在U3里。现在我们需要对U1使能RETIMING,对U2和U3使用AREA_OPTIMIZED策略,对inst1使用DEFAULT综合策略,那么我们就可以通过下图所示约束实现。

审核编辑 :李倩

-

模块化

+关注

关注

0文章

359浏览量

22817 -

Vivado

+关注

关注

19文章

860浏览量

71428

发布评论请先 登录

Vivado时序约束中invert参数的作用和应用场景

AMD Vivado Design Suite 2025.2版本现已发布

FPGA板下载运行调试流程

FPGA板下载调试流程

vcs和vivado联合仿真

FPGA开发板vivado综合、下载程序问题汇总

Vivado中向FPGA的Flash烧录e203的方法

AMD Vivado ChipScope助力硬件调试

Vivado无法选中开发板的常见原因及解决方法

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

Vivado Synthesis的各种流程

Vivado Synthesis的各种流程

评论