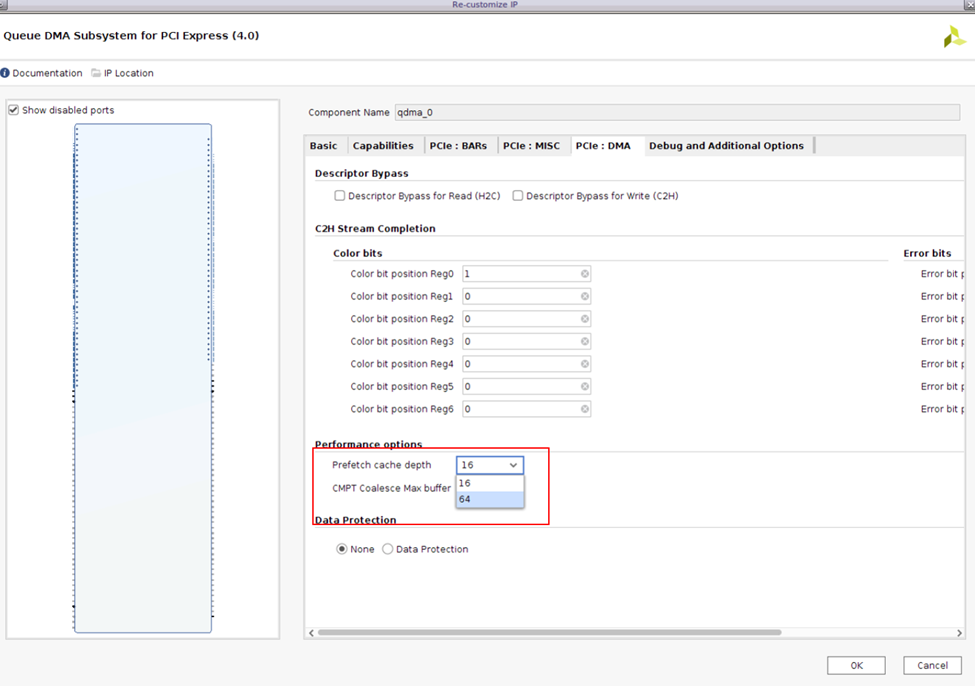

QDMA的驱动在进行版本升级时,可能会对部分寄存器的数值进行变更,用户如果要进行升级,推荐升级到最新的Vivado和驱动版本。如果驱动和Vivado之间的版本相差较大,有时会遇到c2h_cmpt_ready为0的情况,此时IP无法进行数据的传输,这种情况通常在传输大包或者大流量数据的时会出现,遇到这种情况可将QDMA IP的prefetch depth参数进行修改,以改善传输性能。

如果是IP在传输中发生了错误或者出现了丢包的情况,就需要使用ILA IP来抓取QDMA IP中的信号和Dump QDMA IP中的寄存器来进行分析,下面重点讲解下如何Dump IP中的寄存器、重点对哪些寄存器进行分析以及寄存器的意义。

Dump 寄存器:

通过以下网站下载QDMA driver, 运行test app中的reg_dump指令来dump QDMA 寄存器的值和context data。

https://github.com/Xilinx/dma_ip_drivers

寄存器的dump操作可以参考下面网址中的user guide界面。

https://xilinx.github.io/dma_ip_drivers/master/QDMA/DPDK/html/userguide.html

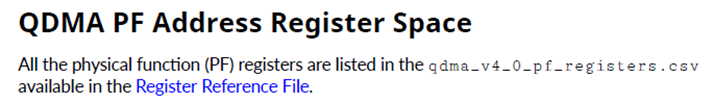

寄存器数值代表的意义可以从在PG302的124页的Register Reference File可以下载到,如下图所示:

对dump出的寄存器进行分析:

使用test app dump出的寄存器的数目太多,本文重点以下几个寄存器进行分析并举例说明:

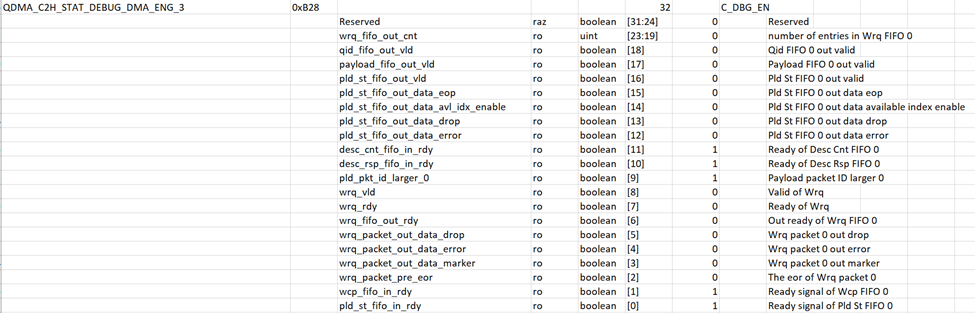

QDMA_C2H_STAT_DEBUG_DMA_ENG_3

QDMA_C2H_STAT_DEBUG_DMA_ENG_4

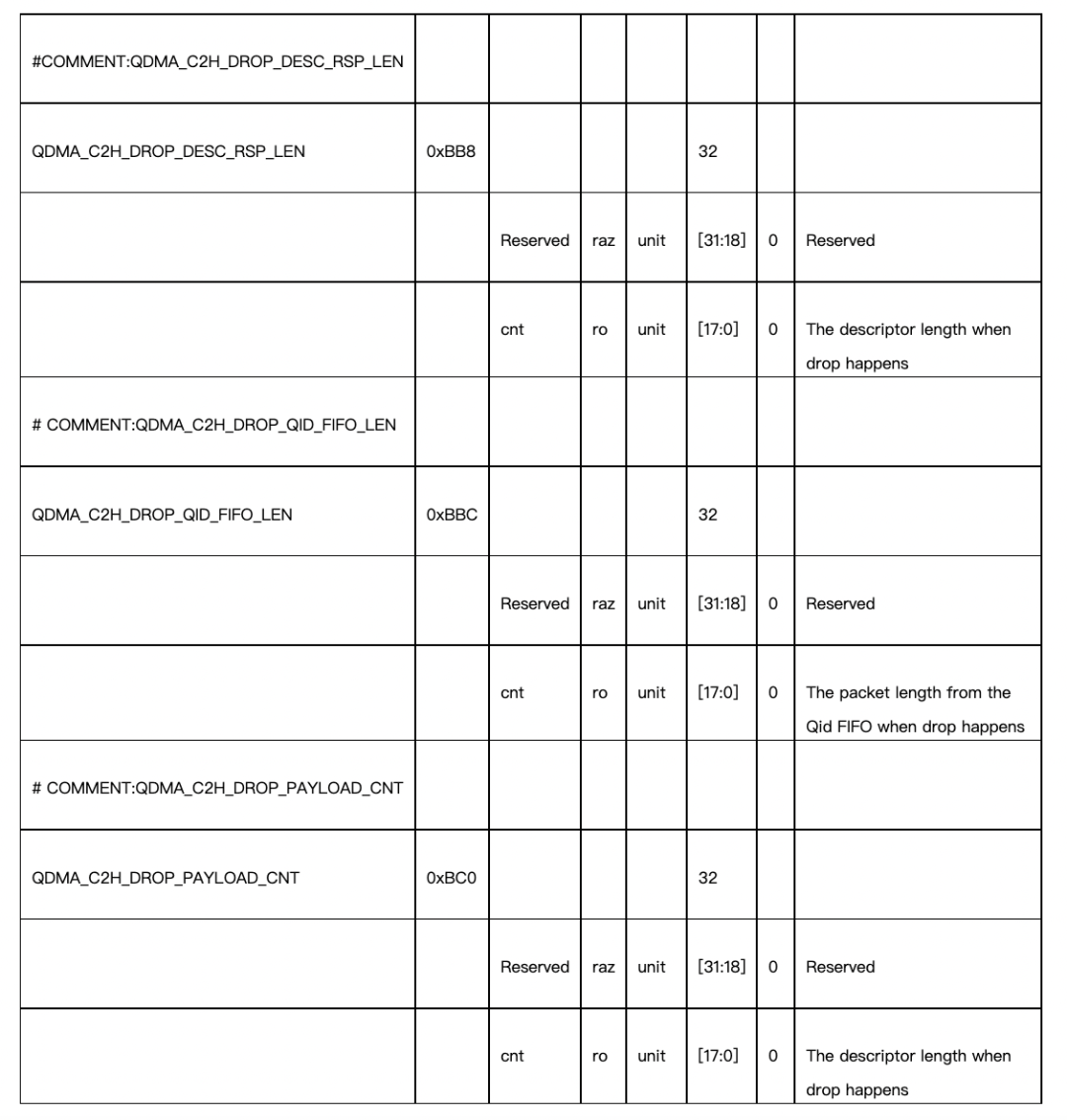

C2H_DROP_DESC_RSP_LEN

C2H_DROP_QID_FIFO_LEN

C2H_DROP_PLD_CNT

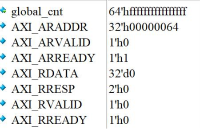

QDMA_C2H_STAT_DEBUG_DMA_ENG_3 是一个32 bit的寄存器,涵盖了许多重要信号的状态信息,是非常重要的debug寄存器,每一个bit位代表的意义及寄存器默认的数值如下:

在对寄存器的数值进行分析时,需要重点关注3、4、5比特,当3、4、5为低是表明IP并未遇到传输错误,那么错误应该是发生在IP传输数据之前,需要对在数据传输前的驱动配置阶段进行分析和定位。

一般IP内发生传输错误时,此寄存器的3、4、5位比特会被置高,当wrq_packet_out_data_marker为高时,需要检查在工程设计中是否使用了s_axis_c2h_cmpt_ctrl_no_wrb_marker信号,此信号的意义如下:

The DMA also has an option not to send completion information to completion ring during a

Marker packet. Port s_axis_c2h_cmpt_ctrl_no_wrb_marker can be set during a marker

packet. This option disables any write to completion ring when that Marker packet is generated.

When this signal is set for a Maker packet, the DMA has no data or completion transfers, but will

respond with maker response on qsts_out_op[7:0].

如果没有使用此信号,说明IP的传输出现了不可修复的错误,需要通过其他的寄存器进行进一步的分析,通常在3、4、5bit被置为高时,此寄存器的0,1bit不会全为高,IP会挂起并停止数据的传输。IP的传输错误有可能是发送了过量的描述符,时序问题及逻辑设计的不规范,下面对在遇到IP 传输错误时的定位方法进行举例说明:

当发现QDMA_C2H_STAT_DEBUG_DMA_ENG_3的3,4,5比特为高时,可以去查找与丢包相关的寄存器,例如:C2H_DROP_DESC_RSP_LEN,C2H_DROP_QID_FIFO_LEN和C2H_DROP_PLD_CNT。这三个寄存器所代表的意义分别如下所示:

因为操作不当导致IP发生丢包时,C2H_DROP_DESC_RSP_LEN,C2H_DROP_QID_FIFO_LEN和C2H_DROP_PLD_CNT 三个寄存器的数值分别为在IP丢包时:描述符的长度、Qid Fifo中的包长和负载Fifo 0中的信用值。当IP发生丢包时,根据以上三个寄存器的前18bit的数值,会比较容易判断驱动或者工程中可能存在的问题。

原文标题:开发者分享|QDMA与driver的问题定位和分析

文章出处:【微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

-

寄存器

+关注

关注

31文章

5621浏览量

130459 -

数据

+关注

关注

8文章

7349浏览量

95058 -

bit

+关注

关注

0文章

48浏览量

32878

原文标题:开发者分享|QDMA与driver的问题定位和分析

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IDT SSTVF16857AGLF DDR寄存器:特性与应用解析

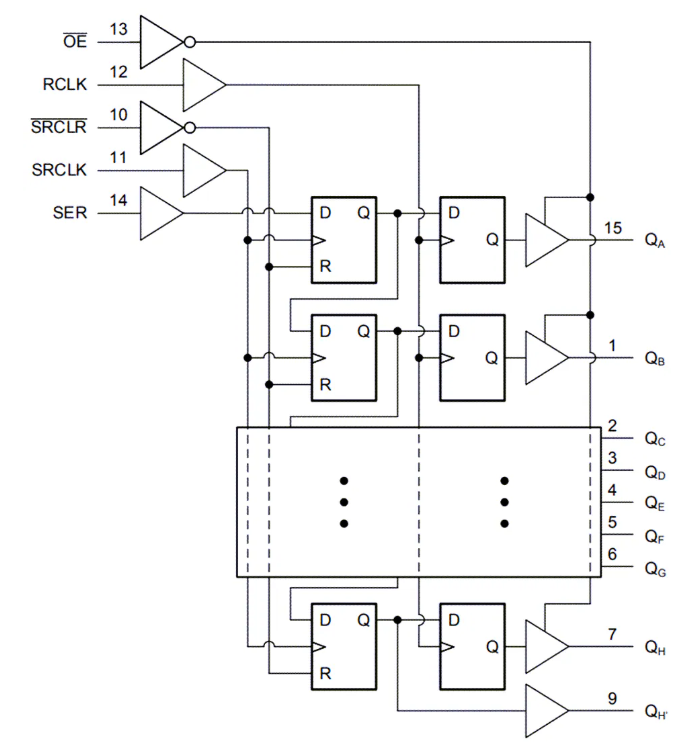

74AHC594:8位移位寄存器的详细解析与应用

74HC595 8位移位寄存器:设计与应用全解析

74LV595A:8位移位寄存器的全方位解析

LAT1170+如何理解 RAMECC FAR 寄存器的值

【NCS随笔】nRF54L15使用UICR寄存器保存数据

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析2

SN74LVC595A 8位移位寄存器技术文档总结

SN74HCT595 8位移位寄存器技术解析与应用指南

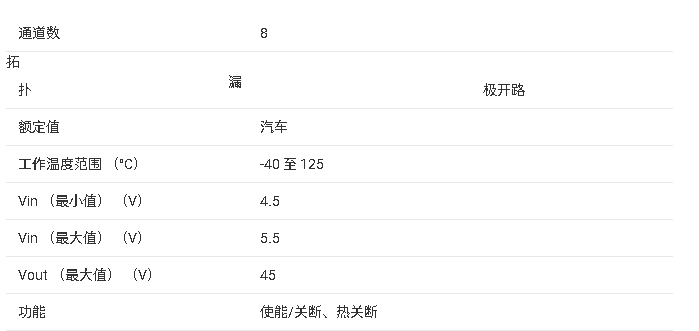

TPIC6595 8位功率移位寄存器技术文档摘要

TPIC6B595 8位功率移位寄存器技术文档总结

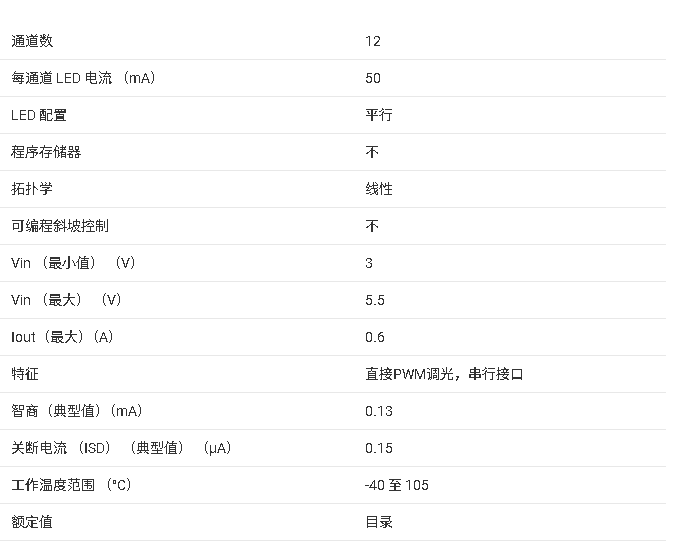

TLC6C5912 12通道移位寄存器LED驱动器技术文档总结

使用寄存器点亮LED灯

第四章 什么是寄存器

如何Dump IP中的寄存器及寄存器的意义

如何Dump IP中的寄存器及寄存器的意义

评论