引言

IGBT是综合MOS管和双极型晶体管优势特征的一种半导体复合器件,作为功率半导体分离器件的代表,广泛应用于新能源汽车、消费电子、工业控制领域,所涉及领域几乎涵盖社会的各个方面,市场需求增长空间巨大。近几年中国IGBT产业在国家政策推动及市场牵引下得到迅速发展,但技术方面与国际大厂仍有较大差距,国际大厂中以英飞凌为代表,技术已发展到微沟槽性IGBT,并达到量产水平。

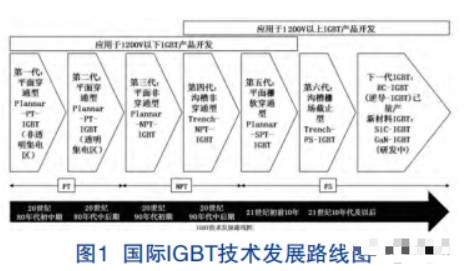

从1980年至今,IGBT经历了六代技术的发展演变,过程如图1所示,分别是第一代平面穿通型(P.PT),第二代改进的平面穿通型(P.PT),第三代平面非穿通型(P.NPT),第四代沟槽非穿通型(Trench.NPT),第五代平面栅软穿通型(P.SPT)和第六代沟槽栅电场-截止型(FS-Trench)。主要是围绕以下3种核心技术及与其同步的载流子浓度分布优化技术发展:(1)体结构(又称衬底):PT(穿通)→NPT(非穿通)→FS/SPT/LPT(软穿通)。(2)栅结构:平面栅→沟槽栅。(3)集电极区结构:透明集电极→内透明集电极结构。

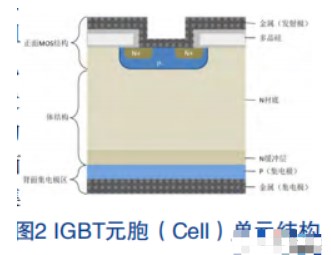

IBGT芯片在结构上是由数万个元胞(Cell)重复组成,工艺上采用大规模集成电路技术和功率器件技术制造而成。每个元胞(Cell)结构如图2所示,可将其分为正面MOS结构、体结构和背面集电极区的结构三部分。

1 体结构的发展

IGBT 的体结构设计技术发展经历从穿通(PT)-非穿通(NTP)-软穿通(SPT)的历程。

(1)穿通结构(Punch Through,PT)特点。随着外延技术的发展,引入N型缓冲区形成穿通结构,降低了背部空穴注入效率,实现了批量应用,但限制了高压IGBT的发展,最高电压1 700V。

(2)非穿通结构(Non Punch Through ,NPT)特点。随着区熔薄晶圆技术发展,基于N型衬底的非穿通结构IGBT推动了电压等级的不断提升,并通过空穴注入效率控制技术使IGBT具有正温度系数,能够较快地实现并联应用、高短路能力,提高应用功率等级,并且不需要外延工艺从而降低成本。NPT技术缺点为器件漂移区较长,电场呈三角形分布,硅片较厚,静态和动态损耗较大。

(3)软穿通结构(Soft Punch Throughput,SPT)特点。NPT结构随着电压等级的不断提高,芯片衬底厚度也随之增加,导致通态压降增大,静态和动态损耗较大。为了优化通态压降与耐压的关系,局部穿通结构(又称为软穿通)应运而生,ABB称之为软穿通(Soft Punch Throng,SPT);英飞凌称之为电场截止(Field Stop,FS);三菱称之为弱穿通(Light Punch Through,LPT)等多种不同名称。在相同的耐压能力下,软穿通结构(SPT)比非穿通结构(NPT)的芯片厚度降低30%,芯片尺寸大幅度减小,动静态性能可扩至30%以上。同时仍保持非穿通结构(NPT)的正温度系数的特点。 近年来出现的各种增强型技术及超薄片技术都是基于软穿通的结构。

2 正面MOS结构的发展

IGBT的正面MOS结构包括栅极和发射区,其中栅的结构从平面栅(Planar)发展为沟槽栅(Trench)。

(1)平面栅。平面栅有较好的栅氧化层质量,栅电容较小,不会在栅极下方造成电场集中而影响耐压,经过优化也可改善器件工作特性,如降低开关损耗等,在高压IGBT(3300V及以下电压等级)中被普遍采用。

(2)沟槽栅。沟槽栅结构将多晶硅栅从横向变为纵向,有效提高元胞(Cell)密度,有利于降低功耗,同时载流子分布更理想,沟道电流大,被广泛应用于中、低(1700V及以下)电压等级的IGBT器件中。沟槽栅的缺点是相对于平面栅结构工艺较复杂、成品率与可靠性降低,栅电容比平面栅结构大,目前先进的增强型技术通过优化正面MOS结构,靠近发射极一端的电子注入效率,从而优化导通压降与关断损耗的折中关系。

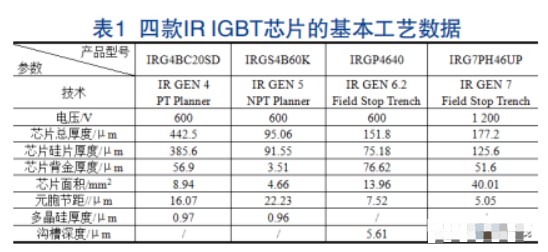

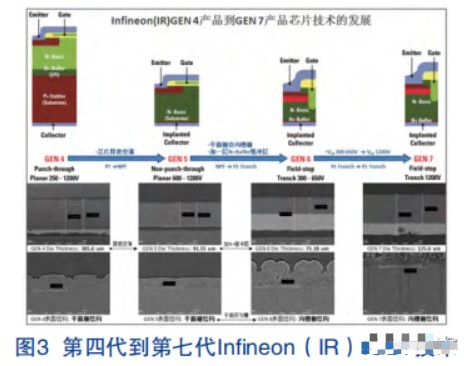

技术发展具有阶段性,每种产品都存在多种技术共同使用的情况。IGBT产品从1980年代初期的非穿通平面栅结构(NPT Planar)发展到现在的主流的场沟道截止结构(Field Stop Trench),发展趋势无疑是朝着芯片更薄、更小,性能更优越的方向前进。通过在Infineon(IR)官网进行选型及对产品资料查找,查找到由IR公司制造的IGBT产品结构及每代产品的特点。经过对已生产的包含上述技术的IGBT产品进行详细工艺分析,以Infineon(IR)的历代产品为例得到一些数据。

经过对4款产品的基本分析,整理出以下信息。由于栅节距(Gate Pitch)在IGBT器件中可作为元胞节距(Cell Pitch),在表1中以元胞节距(CellPitch)进行统计。分析得出:

(1)IR公司结合自有的生产工艺及国际通用IGBT技术定义产品代,并基本处于技术领先的位置。

(2)在不同代产品中的相关技术保持工艺一致,如平面栅结构中的多晶硅厚度为1μm左右,沟槽栅结构中的沟槽深度为5.5μm左右。将以上Infineon(IR)第四代到第七代产品的实验数据与其发布的技术发展示意图结合,整理出如图3所示产品技术发展的参考示意图。

3 IGBT的分析方法

对于IGBT的分析,形成的分析方法主要包含4个步骤:

(1)查找相应的理论支撑;(2)选取适合的样品;(3)使用平面及纵向分析进行实验;(4)实验数据与理论支撑比对分析。使用平面及纵向分析进行实验。对样品进行平面及纵向分析是集成电路中常用的实验方式,本文提到的分析方法中,选取适合产品及技术的实验方案是进行实验这个步骤的重要前提,只有实验方案正确,才能够获取真实的数据并与理论支持比对,得到合理的判断。

IGBT主要平面分析方法:使用反应离子刻蚀机去除IGBT产品中的钝化层或介质层,配合使用研磨机去除IGBT产品中的金属层,可以进行平面逐层分析。使用光学显微镜和扫描电子显微镜观测去除不同层次前后的产品。观测内容涉及芯片形貌特征、元胞尺寸测量等。

IGBT主要纵向分析方法:IGBT纵向分析主要包括基本纵向分析以及纵向染色分析,主要使用到研磨机进行样品制备。经过样品制备后,需要使用扫描电镜观测纵向形貌、层次结构、尺寸测量以及各层成分的分析。纵向染色分析需要使用光学显微镜配合扫描电子显微镜,观测染结的结构、形貌尺寸等。在项目过程中,一般会同时使用以上两种分析方法。

4 结语

基于EDA仿真验证进行芯片研发的方法在业内已广泛使用,与集成电路芯片不同,分立器件的研发由于种类繁多,工艺差异明显、仿真工具有限等,无法使用通用的此类方法,而是需要针对器件或工艺制定具体方法并实施项目。

审核编辑:刘清

-

IGBT

+关注

关注

1291文章

4452浏览量

264326 -

eda

+关注

关注

72文章

3143浏览量

183710 -

MOS

+关注

关注

32文章

1757浏览量

101225

原文标题:IGBT器件结构及其分析

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】跟着本书来看EDA的奥秘和EDA发展

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--中国EDA的发展

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】+ 芯片“卡脖子”引发对EDA的重视

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】+ 全书概览

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--EDA了解与发展概况

70%营收砸向研发!这家EDA企业破局高密度存储EDA、数字EDA

思尔芯荣登“国产EDA工具口碑榜”,以“芯神瞳”原型验证解决方案赋能芯片创新

【书籍评测活动NO.69】解码中国”芯“基石,洞见EDA突围路《芯片设计基石——EDA产业全景与未来展望》

AI+EDA如何重塑验证效率

Vivado仿真之后没有出现仿真结果的解决方法

Wisim DC电源完整性EDA物理验证仿真工具介绍

华大九天物理验证EDA工具Empyrean Argus助力芯片设计

基于EDA仿真验证进行IGBT芯片研发的方法使用

基于EDA仿真验证进行IGBT芯片研发的方法使用

评论