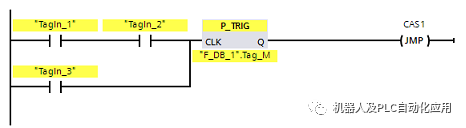

P_TRIG:扫描 RLO 的信号上升沿;

使用“ 扫描 RLO 的信号上升沿”指令,可查询逻辑运算结果的信号状态是否从“0”变为“1”。

该指令将逻辑运算结果 (RLO) 的当前信号状态与先前查询并保存在边沿存储位中的信号状态(< 操作数> )进行比较。如果该指令检测到 RLO 从“0”变为“1”,则说明出现了一个上升沿。

如果检测到上升沿,该指令输出的信号状态为“1”。在其它任何情况下,该指令输出的信号状态均为“0”。

上一次逻辑运算的 RLO 将保存在边沿存储位“"F_DB_1".Tag_M” 中。如果检测到 RLO 的信号状态从“0”变为“1”,则程序将跳转到跳转标签 CAS1 处。

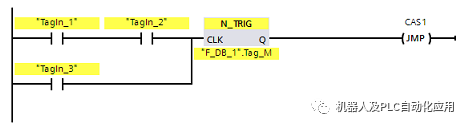

N_TRIG:扫描 RLO 的信号下降沿;

使用“ 扫描 RLO 的信号下降沿”指令,可查询逻辑运算结果的信号状态是否从“1”变为“0”。

该指令将逻辑运算结果的当前信号状态与保存在边沿存储位中上一次查询的信号状态(<操作数>)进行比较。如果该指令检测到 RLO 从“1”变为“0”,则说明出现了一个下降沿。

如果检测到下降沿,该指令输出的信号状态将为“1”。在其它任何情况下,该指令输出的信号状态均为“0”。

上一次逻辑运算的 RLO 将保存在边沿存储位“"F_DB_1".Tag_M” 中。如果检测到 RLO 的信号状态从“1”变为“0”,则程序将跳转到跳转标签 CAS1 处。

审核编辑 :李倩

-

信号

+关注

关注

12文章

2930浏览量

80403 -

逻辑运算

+关注

关注

0文章

58浏览量

10297

原文标题:博途:P_TRIG:扫描 RLO 的信号上升沿/N_TRIG:扫描 RLO 的信号下降沿

文章出处:【微信号:gh_a8b121171b08,微信公众号:机器人及PLC自动化应用】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FS26是否支持上升沿唤醒?

探索NTA4151P和NTE4151P:P沟道小信号MOSFET的卓越性能

探索NTR2101P:小信号P沟道MOSFET的卓越性能与应用潜力

安森美 NTZS3151P P 沟道小信号 MOSFET 深度解析

基于STM32F103C8T6的智能超声波测距尺:从原理到代码的完整实现

优化三极管驱动设计与上升沿性能提升

P_TRIG:扫描RLO的信号上升沿

P_TRIG:扫描RLO的信号上升沿

评论