由于测试芯片的复杂性和覆盖范围的原因,单个小芯片对复合材料成品率下降的影响正在为晶圆测试带来新的性能要求。从测试的角度来看,使小芯片成为主流技术取决于确保以合理的测试成本获得“足够好的模具”

在异构集成系统中,由于单个小芯片而导致的复合成品率下降的影响,就晶圆复杂度和测试复杂性而言,为晶圆测试带来了新的性能要求。

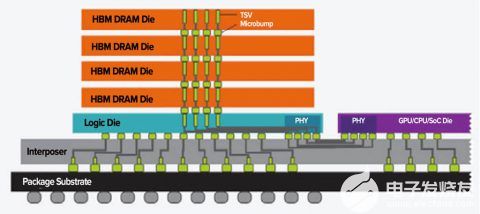

从测试的角度来看,使小芯片成为主流技术取决于确保以合理的测试成本获得“足够好的模具”。 晶圆级测试在小芯片制造过程中扮演着至关重要的角色。以HBM(高带宽内存)为例,它可以及早发现有缺陷的DRAM和逻辑芯片,以便可以在复杂而昂贵的堆叠阶段之前将其删除。堆叠后晶圆的进一步测试可确保完成的堆叠在切割成独立组件之前具有完整的功能。

理想情况下,每个DRAM芯片在堆叠之前都应进行已知良好芯片(KGD)测试,以独立验证其性能。但这在经济上通常是不可行的。在某些时候,测试成本超过了系统完成后增加的价值。

因此,需要一种平衡测试成本和未做芯片不良率检测的测试策略,以将异构集成引入大批量生产。得益于MEMS探针卡技术的创新,FormFactor的产品可以帮助客户实现全流程的KGD测试(例如支持45μm栅格阵列间距微凸点测试的Altius™探针卡,用于高速HBM和Interposer插入连接器的良品率验证),并且可以接受有限的测试成本(例如SmartMatrix™探针卡,通过同时测试300mm晶圆上的数千个芯片,大大降低了每个芯片的测试成本)。

最终,我们在小型芯片制造过程的每个阶段获得有关产品性能和成品率的更多信息,从而帮助客户降低总体制造成本。

审核编辑:符乾江

-

芯片

+关注

关注

463文章

54440浏览量

469414 -

晶圆测试

+关注

关注

1文章

46浏览量

13873

发布评论请先 登录

纵慧芯光:AR-VCSEL正在成为主流激光雷达光源

内置氮化镓成主流?AHB技术你又了解多少?

AI Agent发展浪潮下,芯片级安全为何成为关键?主流芯片厂商如何布局?

离线语音芯片哪些品牌好用?如何选择?

虹科分享 | 为什么MPDO成为电梯通信的关键技术?从CiA417标准说起

芯知识|如何选择核心语音IC?盘点广州唯创电子主流语音芯片方案

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

远距MEMS/固态vsTOF近距方案,哪种会成为主流?

普诚PT2513B芯片在冰箱风机的应用

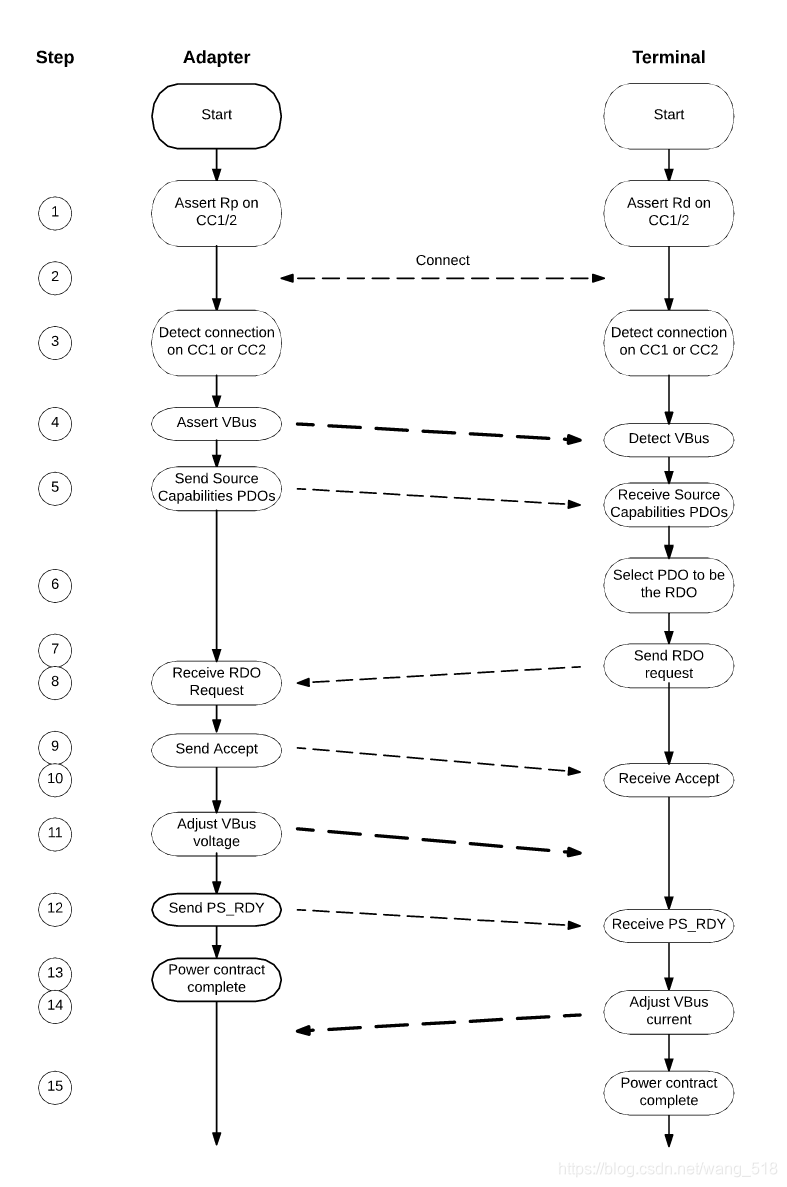

QC/PD/FCP/AFC快充协议,快充电压诱骗芯片 - PD和QC快充电压诱骗芯片

主流汽车电子SoC芯片对比分析

灵动微电子MM32MCU的主流型芯片选型

小芯片成为主流技术的最大挑战是什么

小芯片成为主流技术的最大挑战是什么

评论