为了加速SiTime MEMS硅晶振产品的应用普及,让中国电子工程师能快速体验MEMS硅晶振的高稳定性、高可靠性、超小封装、超低功耗、超低抖动等更多优势,SiTime公司联合本土半导体分销商北京晶圆电子有限公司共同建立SiTime样品中心,为用户提供免费样品申请,小批量试产、现货应急、特价申请、技术支持等便捷服务,更多信息请访问www.sitimechina.com,客户服务热线400-888-2483。

1、SiT9120简介

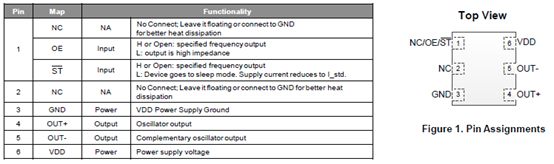

SiT9120是SiTime公司推出的低抖动、高性能差分晶振,SiT9120支持LVPECL和LVDS信号输出。

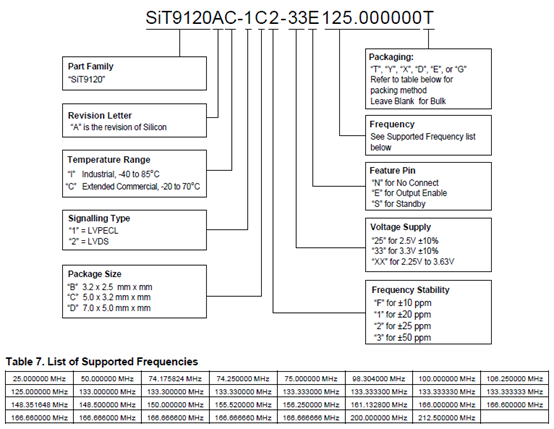

SiT9120的支持25 MHz - 212.5 MHz之间31个标准频率,SiT9120频率稳定度达10ppm、相位抖动0.6ps,频率精度达小数点后六位,目前SiTime实现了这两项的结合。

SiT9120经过50000G抗冲击及70G抗振测试,MTBF(平均无故障时间)达12亿小时。

2、SiT9120产品系列参数

振荡器类型 | 差分振荡器 |

频率 | 25MHz -212.5MHz之间31个频率 |

频率稳定性 (ppm) | ±10、±20、±25、±50 |

输出类型 | LVPECL、LVDS |

工作温度范围 (℃) | -20 ~ +70,-40 ~ +85 |

抖动 | 0.6ps |

电源电压 (V) | 2.5 ~ 3.3 |

封装尺寸 (mm²) | 3.2 x 2.5、5.0 x 3.2、7.0 x 5.0 |

可用性 | 生产中 |

3、SiT9120产品系列型号命名规则

4、SiT9120特点

0.6 ps RMS相位抖动 (12 kHz至20 MHz) | 对于最严格的应用(例如10GbE和SONET)具有出色的抖动容限 |

卓越的频率稳定性, 低至±10 ppm | 更好的定时裕度,增强系统稳定性和鲁棒性 广泛的可编程性 25至212.5 MHz之间的31个固定频率 LVPECL和LVDS输出信令类型 电源电压为2.5 V和3.3 V 频率稳定性为±10 ppm和±50 ppm 定制规格以实现最佳系统性能 性价比高 在操作范围内轻松提供任何设备规格 |

三个行业标准包 | 100%替换石英、SAW和泛音振荡器,无需任何设计变更 极短交付周期 减少库存管理费用 缓解短缺风险 |

5、SiT9120应用

1Gb到10Gb以太网

光学模块

PCIe

光纤通道

系统计时

无线和回程

光纤、电缆、DSL

CPE和家庭网关

安全设备

数据中心

精密GNSS

GPS/GNSS模块

零售电子产品

远程通信

智能农业

VR和AR

个人计算机

音频和视频

关于SiTime公司

SiTime是一家专注于全硅MEMS时钟解决方案的Fabless半导体设计公司。公司成立于2005年,于2019年在美国纳斯达克上市。截至2021年底,全球累积出货量已超过20亿片,占据全球MEMS硅晶振市场90%以上份额。

SiTime采用MEMS技术与CMOS半导体技术相结合,依托先进的堆叠封装工艺制作而成。无需更改PCB设计,即可P2P完全替代所有传统石英振荡器产品。大尺度频率覆盖范围、国际标准封装、灵活的产品组合,快捷的可编程交付方式。所有产品可在24小时内提供32KHz--725MHz任一频率样品供应,实现更高性能时钟样品的快速交付。SiTime硅晶振以稳定的性能和超高的性价比成为了大多数高性能主控芯片的理想时钟选择和强健的心脏。不仅可以缩短研发周期,节约开发调试成本,而能降低未来产品返修风险,快给你的电路换上一颗SiTime硅晶振吧。

关于SiTime样品中心

SiTime样品中心成立于2014年,由SiTime公司联合北京晶圆电子有限公司共同创立,并由晶圆电子全权负责全面运营、客户服务以及国内的交付任务。SiTime样品中心宗旨是致力于加速SiTime硅晶振市场在大中华地区的应用普及,助力中国客户产品时钟解决方案升级换代。提供售前售后技术服务、24小时快速供样、以及国内中小批量现货支持和重要客户的全方位策略服务。更多资讯可访问SiTime样品中心官网(www.sitimechina.com)。

-

FPGA

+关注

关注

1664文章

22504浏览量

639313 -

差分晶振

+关注

关注

0文章

189浏览量

2099

发布评论请先 登录

攻克网络通信时钟挑战:高性能差分晶振解决方案

差分输出VCXO振荡器 | FCom富士晶振 - 低抖动时钟解决方案

SiT9120:低抖动、高性能差分晶振,FPGA时钟伴侣

SiT9120:低抖动、高性能差分晶振,FPGA时钟伴侣

评论