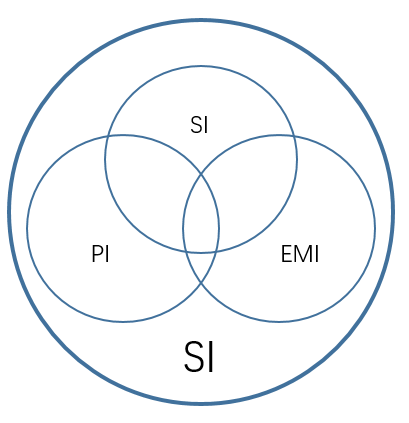

先说一下,信号完整性为什么写电源完整性?SI 只是针对高速信号的部分,这样的理解没有问题。如果提高认知,将SI 以大类来看,SI&PI&EMI 三者的关系:

所以,基础知识系列里还是得讲讲电源完整性。话不多说,直接上图:

01

区别

记得刚接触信号完整性的时候,对电源完整性(PI)和电源工程师之间的关系是分不清的。后来才渐渐了解这里面的千差万别。简单来说,电源的产生与转化,比如Buck电路,LDO,DC-DC等,源端部分这些是电源工程师来确定的。

电源工程师也会进行相关的电源可靠性设计与测试,比如耐压余量,耐电流余量,保护设计(过压、过温、过流等)。这些工作是电源工程师的专业范畴。电源这一块很复杂,光各种拓扑结构就已经让人云里雾里了,绝对是可以深究的一份职业。

02

PDN

电源完整性(PI)更关注于电源路径及终端,也就是电源分配网络(PDN)。从源端稳压模块(VRM)经过路径(单层直达或过孔转换的几个层面),到达终端,最终流向使用芯片或经过线缆到使用设备。

电源路径与信号路径是有区别的,电源分配网络中一个电源路径可以在一个节点分成多个路径,或者说转换成多个电源,终端挂多个元器件,可以理解为一对多。而信号路径只能一对一。

既然电源分配网络是为终端设备提供所需电源,那就是有要求,就需要对电源分配网络管控。如信号路径,除了保证返回电流,还要尽量保证返回路径的低阻抗。由于是一对多的情况,这样的管控,才能保证返回电流不相互重叠,不会发生地弹,即尽量避免开关噪声(SSN)。

基本要求是,保证供电电压稳定,至少能够维持在一个很小的容差范围内,通常在+/-5%以内。电源的测试中有纹波测试,这个纹波测试标准就是+/-5%。

讲到返回电流,这里就要分为直流部分和交流部分。

直流部分:

终端设备需要稳定的电压输出,电源分配网络互连之间串联电阻的存在,直流部分通过,就会产生压降,通常称为IR 压降。当电流发生波动时,压降也会随之波动,从而影响终端设备的识别。之前的USB设备好像最低电压值4.75 V。

交流部分:

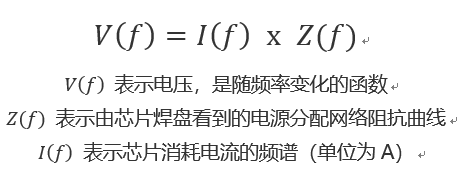

当交流电流通过电源路径时,电源分配网络上也将产生电压降,这个压降会随着频率发生变化:

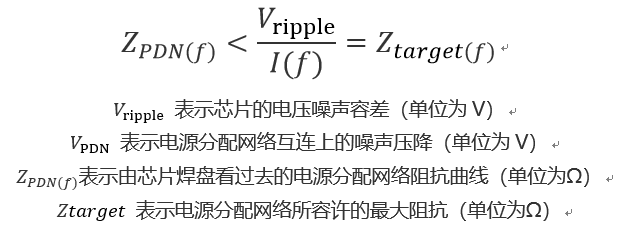

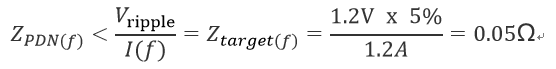

电源路径的不同(层数&Shape宽度等),造成的压降变化是不同的,输出稳定电压到终端的难度很大,我们所要做的只是保证电压的变化在一定的范围之内,也就是所谓的噪声容差。上式就可能转换为目标阻抗:

既然保证不了路径上电压的稳定,那么电源分配网络的电流在波动的情况下,就需要保持电源分配网络阻抗低于目标阻抗。

需要注意的是,即使同一个电源芯片或模块,针对不同的产品,也会给出不同的标准。即使相同的标准,因为不同的电源路径,不同的版图走线,也会有千差万别。所以,电源分配网络目标阻抗才是最基本的要求。

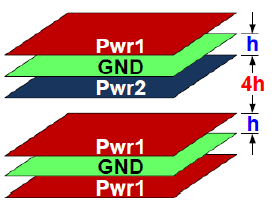

目标阻抗的管控说到底就是路径管控。两个因素:电源和地平面之间介质尽量薄,尽量短而宽的走线。

03

电源树(Power tree)

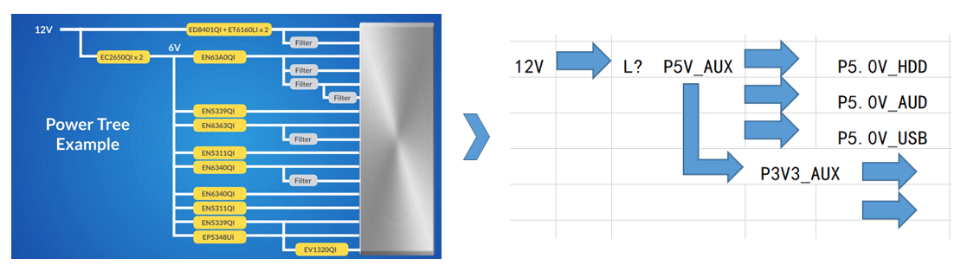

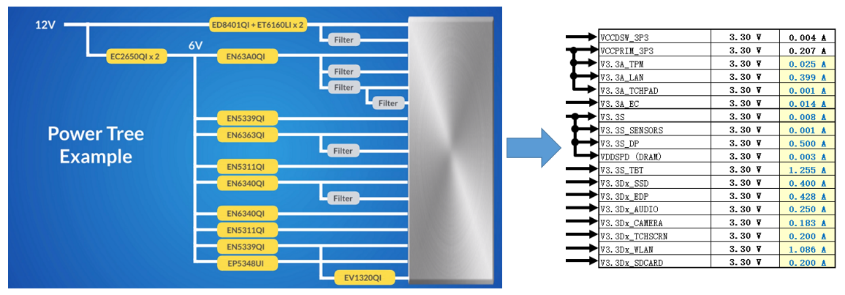

先期评估,确认各个电所需层面和路径的时候,我们会预先根据相关规范或标准,制定一个电源树(Power tree)。个人觉得电源树的概念提的特别好。一个主干道有很多分支,分支上再有分叉,一直到末端。

电源分配网络可以有很多分支,也就是说路径上可以挂很多设备,比如5V电源下挂HDD,USB设备等。

电源的分类

比如12 V的电转出5V,5V总电分出分支,给到各种设备。5V经过LDO转换电路出3.3V电,,3.3V总电分出分支,再往下继续……

同时列出各个分支所需电流的多少,为后面路径规划(所需电源Shape大小给出标准),同时给出对应的层面及评估。

在做电源路径规划,建议先做电源树Power Tree,对所做设计的终端设备所需电压路径及所需电流大小一一评估,产品的不同,有的产品可能会使用几十种电压值。检查的时候,建议从终端往前反推,这样保证没有遗漏。

04

频段管控

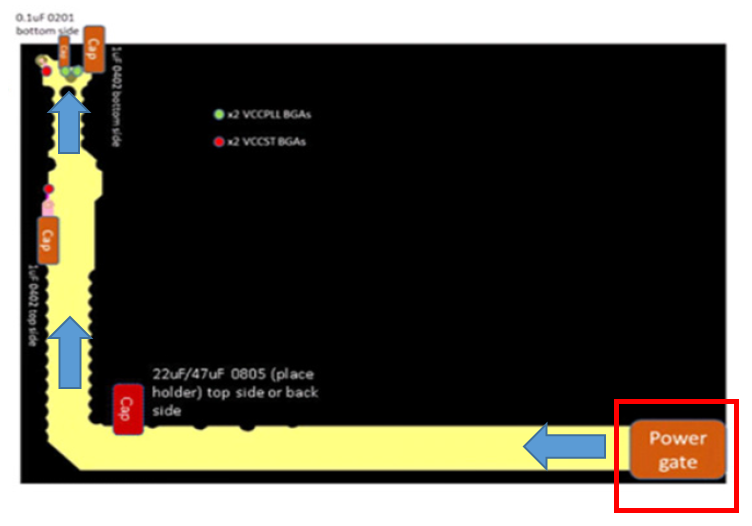

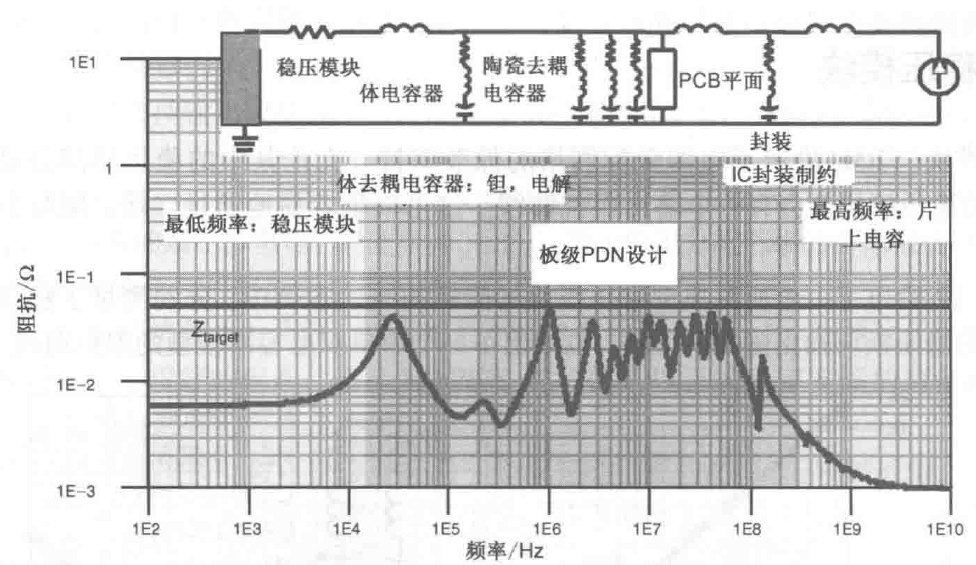

上面提到一款产品,有几十种电压,每个电压的目标阻抗随着频率是改变的,这个时候就需要对路径进行频段分类:

片选电容

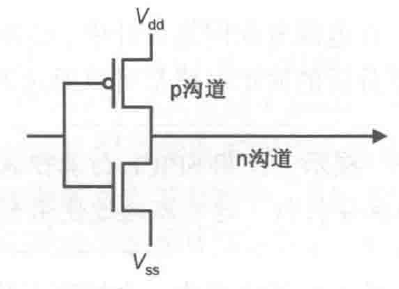

芯片是由晶体管组成,不管是P沟道还是n沟道导通,都会形成栅极电容,随着制程工艺的提升,沟道长度变短,单位面积电容增大。所以,高频时,片上电容为电源分配网络提供了低阻抗。

稳压模块

稳压模块( VRM)决定了电源分配网络的低频阻抗。稳压模块是为了保证输出阻抗低频的阻抗曲线。

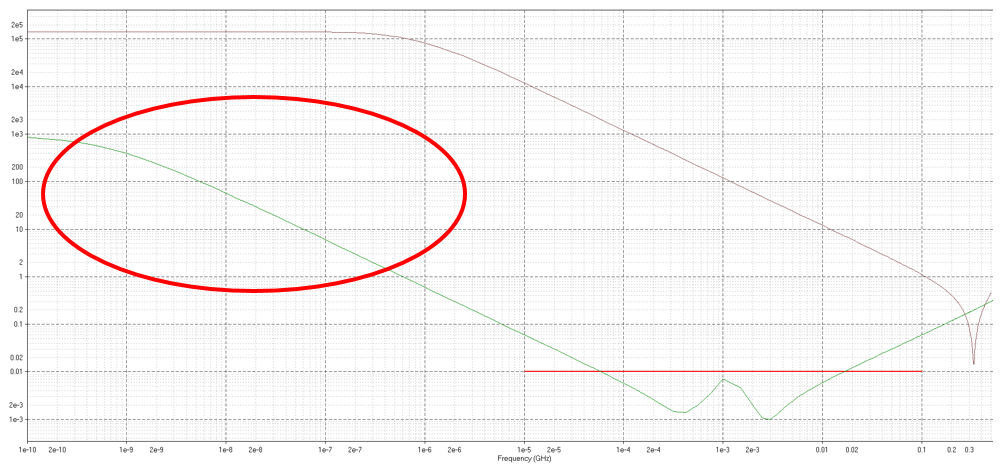

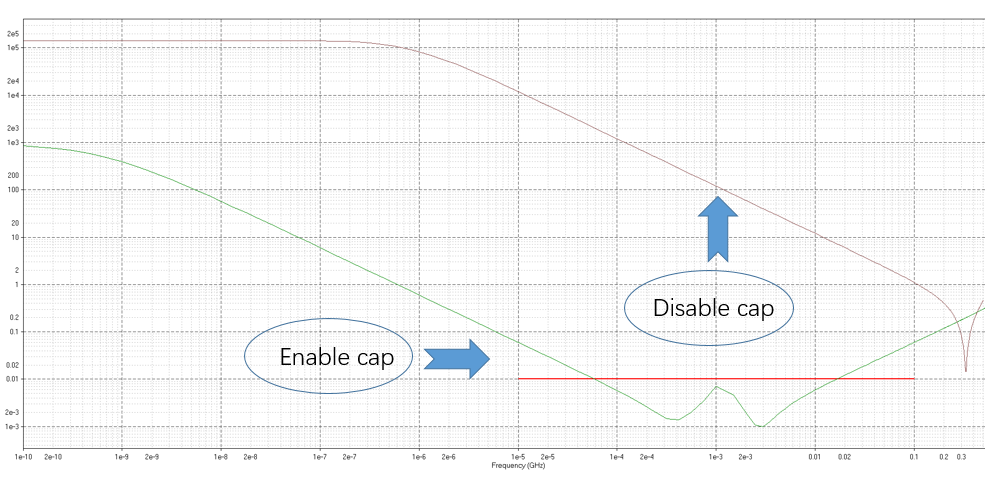

实际中VRM没有相关模型,所以我们仿真的曲线见下图。所以在低频(10K以下)阻抗反而很高。

PCB板级

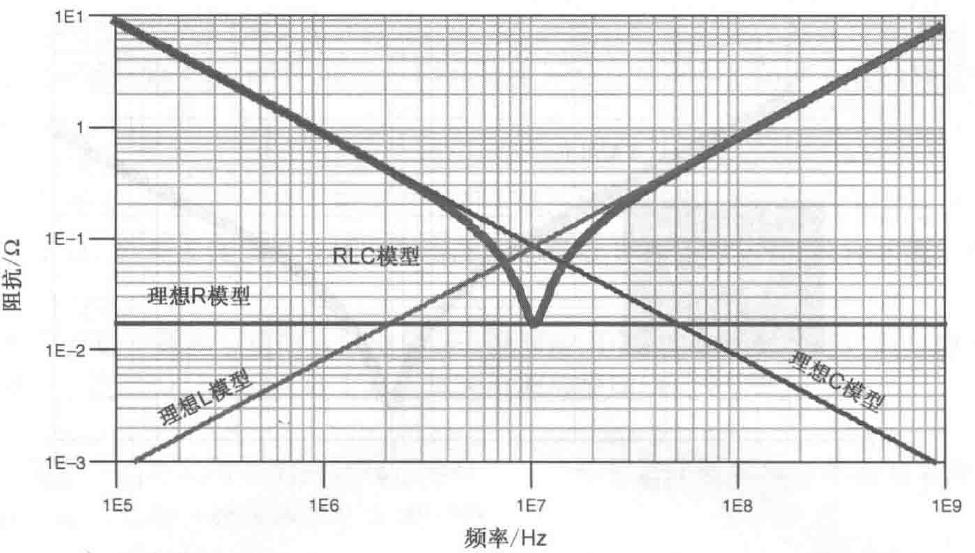

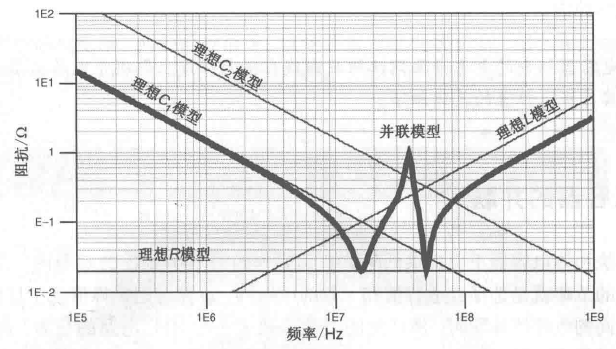

为了确定板级电源分配网络的设计目标阻抗,可以先找出上限频率,即找出PCB板的阻抗开始超过目标阻抗时的频率点。如果要整个单独分析,会比较麻烦。在低频时,RLC 电路的阻抗取决于理想电容,在高频时则取决于理想电感。而理想电阻则决定了 RLC 的最低阻抗。

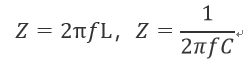

简单点,分为电感和电容的两个部分。相关公式为:

注意其和截止频率公式区分。

电感方面考虑封装引脚、过孔和扩散电感等共同作用。

封装引脚是串联在芯片焊盘到电路板焊盘之间,可能有数百个电源/地平面对,开关数量的不同,封装引脚电感是变化的,一般不超过1 nH。还有过孔及电源/地平面上运送电流过程中的扩散电感,共同决定了回路电感。

当然,这里面过孔与过孔之间,平面之间,表层传输线之间等,这些情况的回路电感,这里就不做展开。

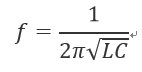

电容方面从摆放位置、电容容值&个数、反谐振三个方面来说。不同的容值,不同封装,耦合半径的不同,所以摆放的位置需要考虑。还有,电容器的相关组合,摆放位置都是尽量靠近封装,那是因为电流重叠,扩散电感增加,电容器摆放可以减小增加量。

所以,电容器组合对电源分配网络阻抗曲线的影响,在很大程度上取决于摆放在PCB板上位置。

电容除了摆放位置还要分为容值相同和容值不同的两种情况。在通常的板级应用中,使用较少个数的不同容值的电容器(而不是使用相同容值的电容器)往往能使阻抗最低的原因。为了使电容器的个数最少 ,一般选择不同的容值。

选择不同容值的电容器,还有一个原因:反谐振。容值的不同,自谐振频率也不同,电容之间的并联,让其之间有一个新的特性,即阻抗的峰值,称为并联谐振峰值,它发生在并联谐振频率( Parallel Resonant Frequency, PRF)处。这时候就需要添加一个其自谐振频率介于它们之间的电容器加以降低。

需要注意的是,当需要采用多个电容并联来满足容值要求时,最好采用同类型的电容进行并联。这里的同类型是指封装。

板级电源分配网络设计的频率范围约从 100 kHz 到 100 MHz。这正是电路板平面和多层陶瓷贴片电容器( MLCC) 发挥作用的频率范围 。这也是仿真时,重点关注的频率范围。

本例以1.2V的CPU用电为例,来举例说明PDN阻抗仿真。纹波百分比5%,最大电流为1.2A,根据公式

上图说明,是否使能电容对PDN阻抗的影响很大。

05

总结

在电源树里,我们给出的都是产品规格或者设计规范里给出的峰值电流,实际的应用中,这种情况出现的机率很小。所以,消费类产品,在成本的管控之下,会给出不同配置的产品。低配版本,这时候,会减小MLCC的使用种类和数量,OptimizePI是一项很重要的工作,这个后面有机会再讲。通过优化,来降低产品成本,这也是电源完整性的关键所在。

审核编辑 :李倩

-

电源

+关注

关注

185文章

18982浏览量

264500 -

阻抗

+关注

关注

17文章

993浏览量

49497 -

信号完整性

+关注

关注

68文章

1497浏览量

98242

原文标题:电源完整性基础知识

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IDT信号完整性产品:解决高速信号传输难题

罗德与施瓦茨示波器RTO2014破解信号完整性难题的全面指南

信号完整性(SI)/ 电源完整性(PI)工程师的核心技能树体系

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

信号完整性为什么写电源完整性?

信号完整性为什么写电源完整性?

评论