一.前言

在驱动一些较大电流的负载时,有时候由于单个MOS管的通流能力有限,很多人喜欢把几个MOS管并联起来,从而实现更大电流负载的开关,这种应用也比较广泛了,但是其中存在一些问题需要我们注意,今天我们就讲一下对应的问题以及解决方案。

二.MOS管并联的问题以及解决方案

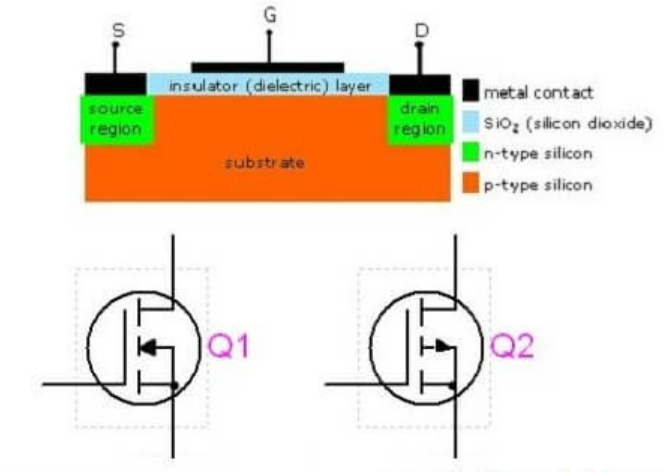

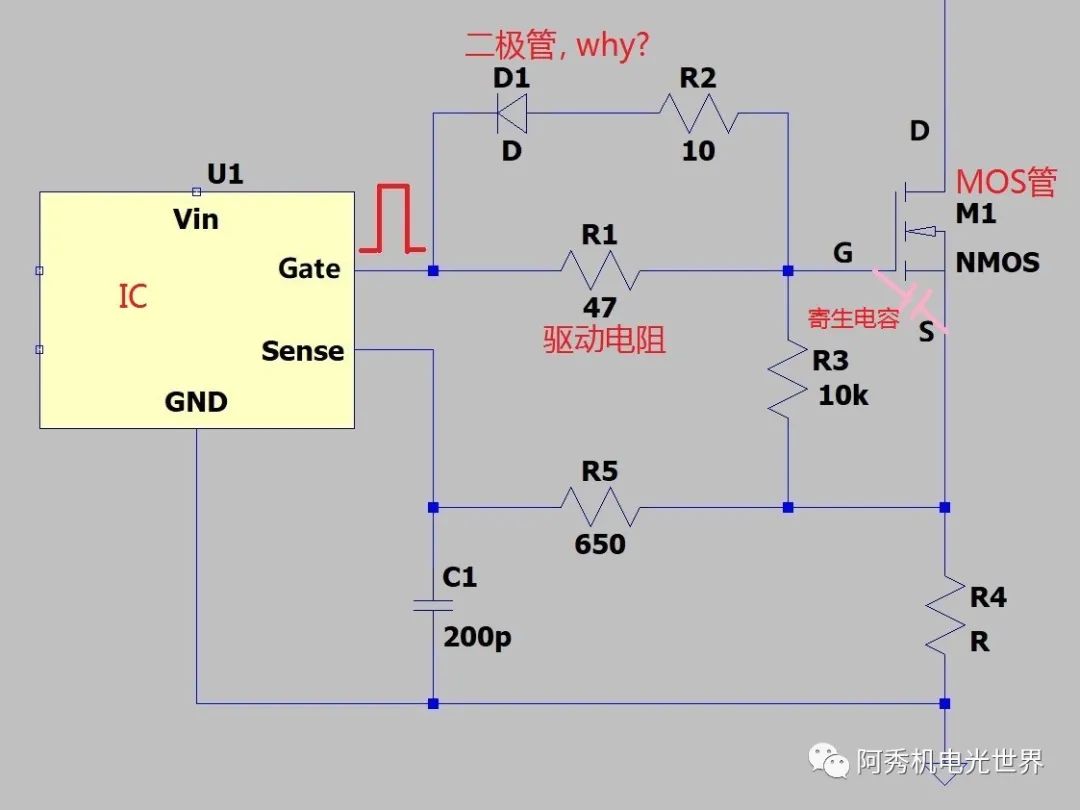

对于NMOS而言,我们在G极施加正电压,会吸引负电荷从而形成导通沟道,从MOS管的结构可以看出由于G和S以及D之间存在绝缘层,从而会产生寄生电容的问题。

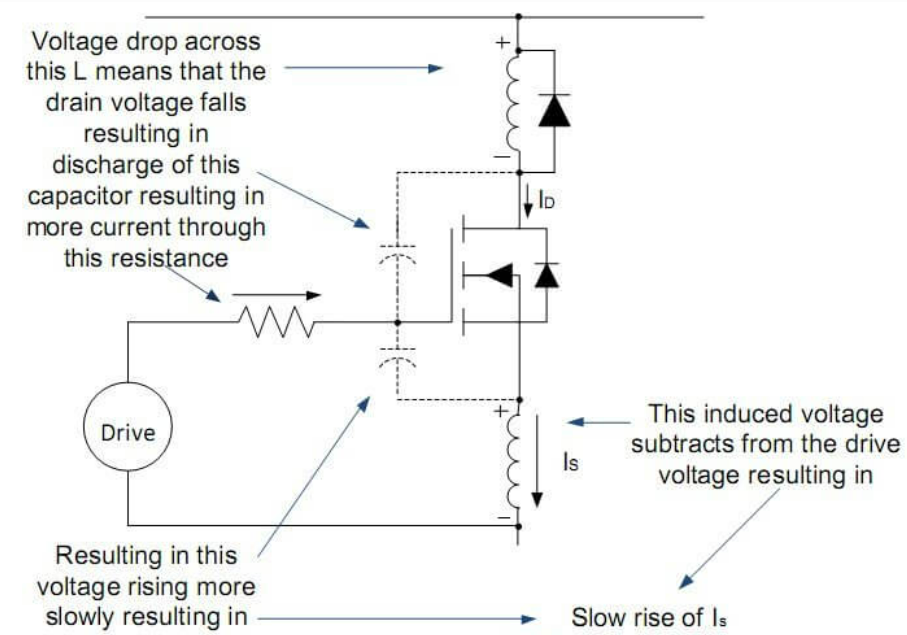

当我们在开关电机这种感性负载时,当感性负载两端的压降降低后,GD之间寄生电容的存在会导致流经栅极电阻的电流增大,并且在dv/dt较大时,干扰会通过GD在栅极形成较大的干扰电压,可能会使得MOS管误导通。而GS之间的寄生电容的存在则会导致驱动波形变得畸形,MOS管的开关产生延时。

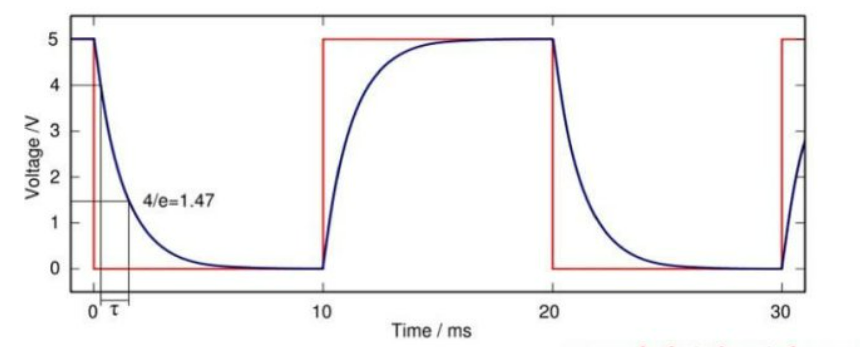

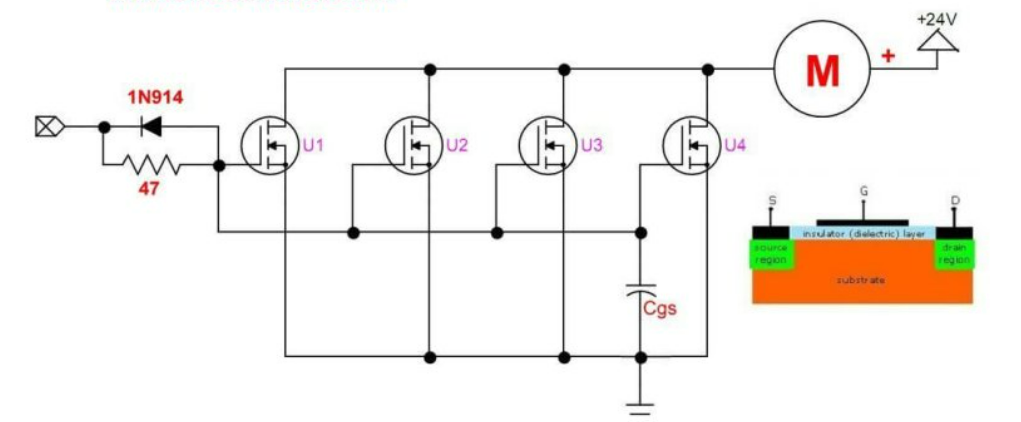

通过下图能明显看出从驱动器出来的方波驱动波形倒是MOS管栅极后就变了样,所以问题就来了,一个MOS的栅极电容可能不算什么,但是当你把几个MOS并联起来后你会发现这个时候的栅极电容已经足够大了,你完全不能忽略他了,所以你一定要测一下栅极的驱动波形,看看是不是已经畸变的不成样子了。或者你也可以在设计之前先评估一下由于寄生电容导致的波形上升时间,我们可以在规格书中找到MOS的栅极寄生电容C,如果你的4个MOS并联在一起,那总电容约等于4*C,如果栅极串联的电阻是100R,那么时间常数就是4*C*100,一般3-5RC可以完成电容的充电,所以驱动波形上升时间大概是3*4*C*100。

知道了问题所在,接下来就谈谈怎么解决问题,寄生电容是MOS的固有特性,只要不换MOS型号,那么我们是没法减小MOS的寄生电容容值的,所以我们只能从减小栅极电阻R出发,把所有栅极连在一起,只用一个栅极电阻,给电阻并联一个二极管,这样MOS关断时由于二极管导通,电阻相当于被二极管短路,可以加速MOS关断。或者选用驱动能力比较强的驱动IC也能改善此问题。

三.总结

MOS管并联的应用,大家一定要注意驱动波形畸变的问题,特别是在PWM模式下工作时,驱动频率高的话可能会出问题,这些都是需要我们在前期设计就要考虑。

审核编辑:汤梓红

-

并联

+关注

关注

5文章

260浏览量

37398 -

电流

+关注

关注

40文章

7229浏览量

141660 -

MOS管

+关注

关注

111文章

2815浏览量

77980

发布评论请先 登录

MOS管并联的问题以及解决方案

MOS管并联的问题以及解决方案

评论