由于CPU是核心硬件,相信我们在选择CPU的时候都会去关心CPU参数方面,而在CPU核心参数中,我们经常会看到缓存(Cache)这个参数,那么CPU缓存有什么用?下面科普一下关于CPU缓存的作用。

CPU没有存储功能,那么缓存到底是干什么的?CPU缓存是用于减少处理器访问内存所需平均时间的部件,作用类似于CPU内部的内存。

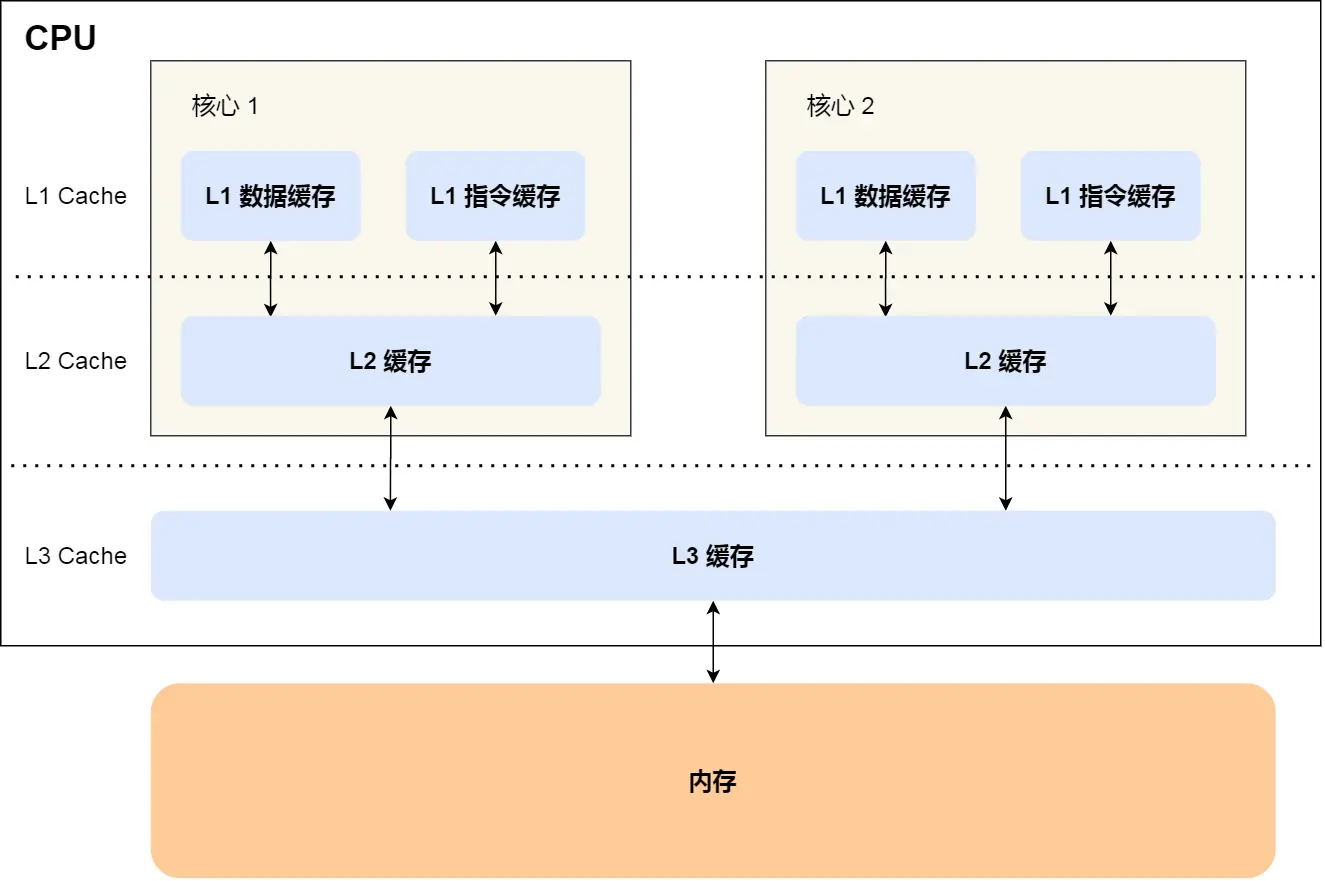

更详细来讲,在计算机系统中,CPU高速缓存在金字塔式存储体系中它位于自顶向下的第二层,仅次于CPU寄存器。其容量远小于内存,但速度却可以接近处理器的频率,比内存快得多。

缓存的出现主要是为了解决CPU运算速度与内存读写速度不匹配的矛盾,因为CPU运算速度要比内存读写速度快很多,这样会使CPU花费很长时间等待数据到来或把数据写入内存。

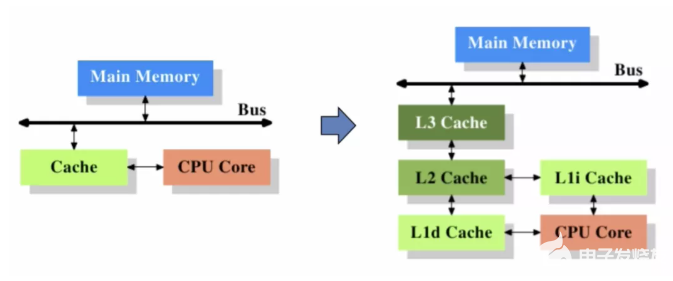

按照数据读取顺序和与CPU结合的紧密程度,CPU缓存可以分为一级缓存,二级缓存,部分高端CPU还具有三级缓存。

之所以CPU需要采用这种层级结构,主要就是是从成本、性能、容量还有面积上来平衡的。

提升命中率:所谓的命中率是在高速缓存中找到内存引用的速率,我们希望能够首先通过缓存中获得信息,以得到速度优势,所以缓存需要最大限度地实现这一目标。对于单个高速缓存,大小、关联性和块大小决定命中率。

降低更低级别内存下的开销:高速缓存是内存层次结构的一部分,其性能会影响其它性能,处理其它内存花费的时间越长,意味着系统性能越低,也就是说尽可能让处理在缓存中完成。

减少错失惩罚:缓存中不能命中是无法避免的事情,但是我们可以减少处理未命中所需的时间以获得更好的处理器性能,通过提升命中率并通过应用不同的优化,能够降低错失惩罚。

高速缓存是CPU中十分重要的部分,占据了大量的资源开销和成本,如果您看过CPU架构图的话,您就会发现缓存占据了至少50%的面积,绝对至关重要。

对于一般用户你只需了解CPU缓存能够提升CPU的工作效率即可,缓存在CPU参数中的作用举足轻重。现在大家知道CPU的缓存有什么作用了吧。

-

处理器

+关注

关注

68文章

20329浏览量

254859 -

cpu

+关注

关注

68文章

11326浏览量

225873 -

缓存

+关注

关注

1文章

248浏览量

27812

发布评论请先 登录

京东缓存中间件架构与缓存内核优化

KeepAlive:组件缓存实现深度解析

REDMI Turbo 5系列搭载MediaTek天玑9500s芯片

C语言的缓冲区(缓存)详解

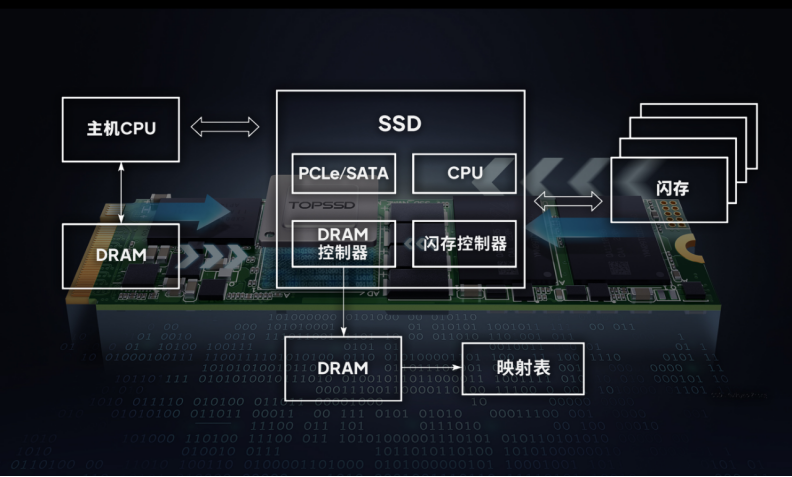

SSD为何需要DRAM缓存?天硕工业级SSD带来深度解析!

串口DMA发送有缓存吗?

探索CPU架构的奥秘,揭秘高性能计算的隐形引擎

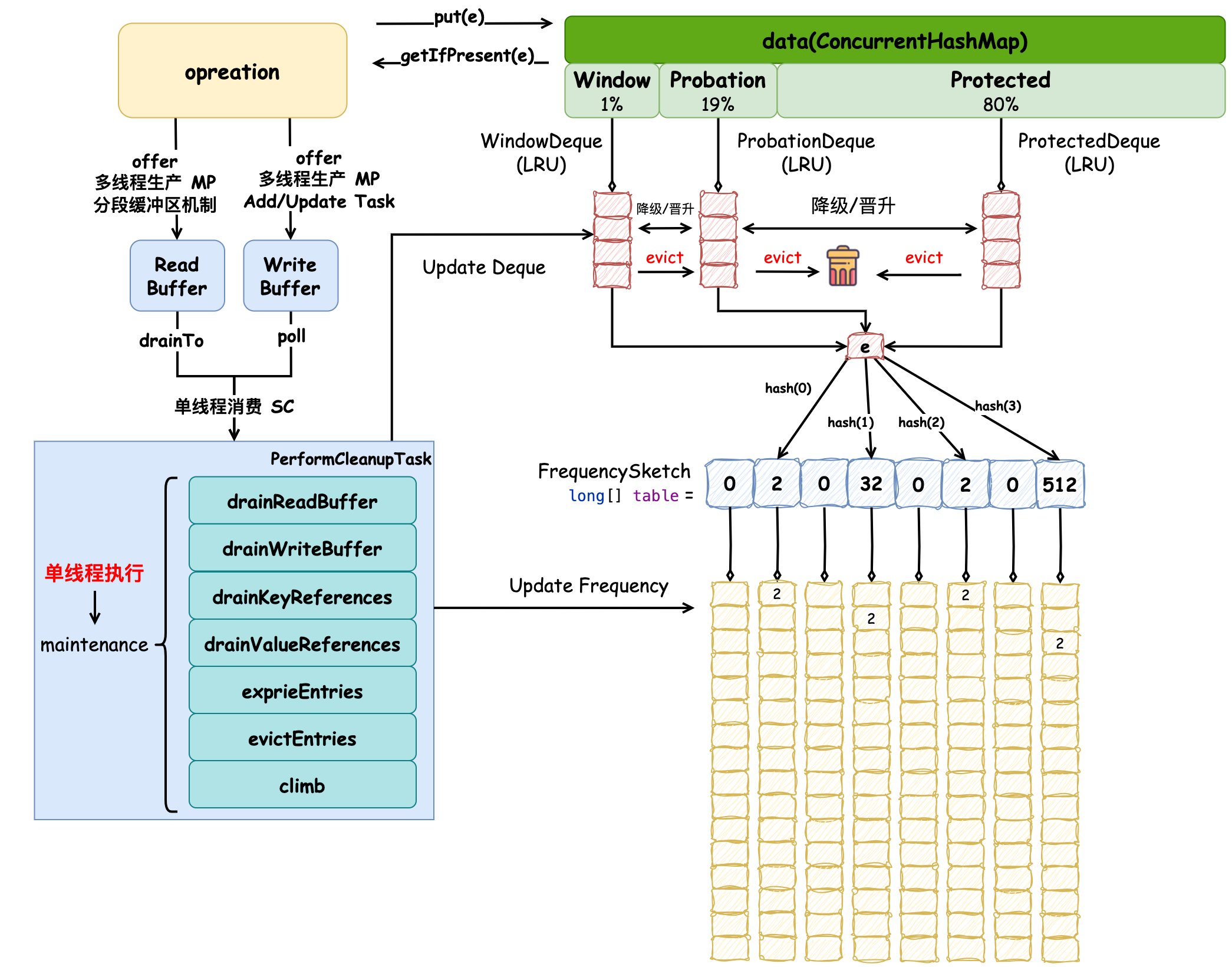

缓存之美:万文详解 Caffeine 实现原理(上)

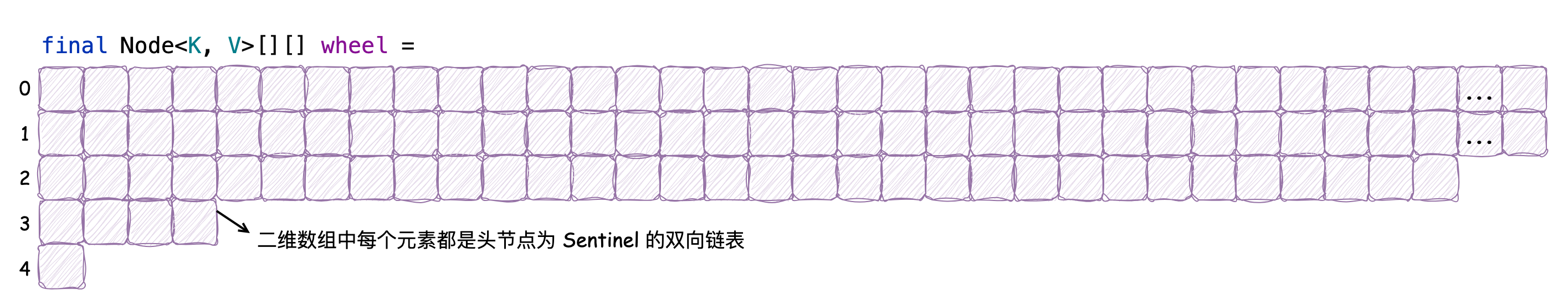

本地缓存 Caffeine 中的时间轮(TimeWheel)是什么?

高性能缓存设计:如何解决缓存伪共享问题

MCU缓存设计

国产电脑CPU性能排行榜TOP7:CPU缓存/主频/多核实测数据分析

关于CPU缓存的作用

关于CPU缓存的作用

评论