本文的关键要点

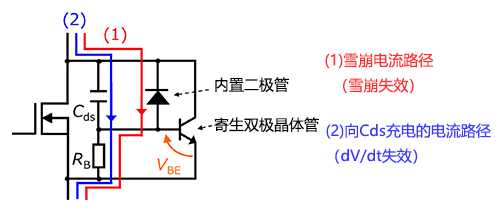

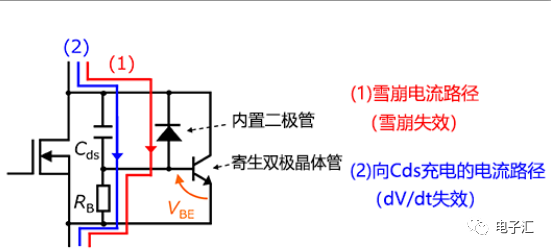

dV/dt失效是MOSFET关断时流经寄生电容Cds的充电电流流过基极电阻RB,使寄生双极晶体管导通而引起短路从而造成失效的现象。

dV/dt是单位时间内的电压变化量,VDS的上升坡度越陡,越容易发生MOSFET的dV/dt失效问题。

一般来说,反向恢复特性越差,dV/dt的坡度越陡,越容易产生MOSFET的dV/dt失效。

什么是dV/dt失效

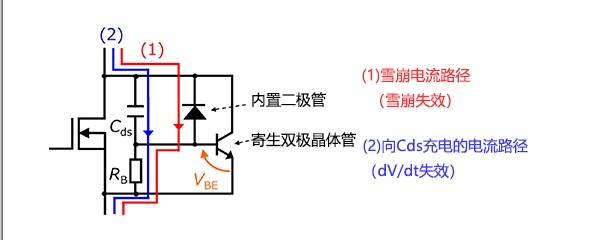

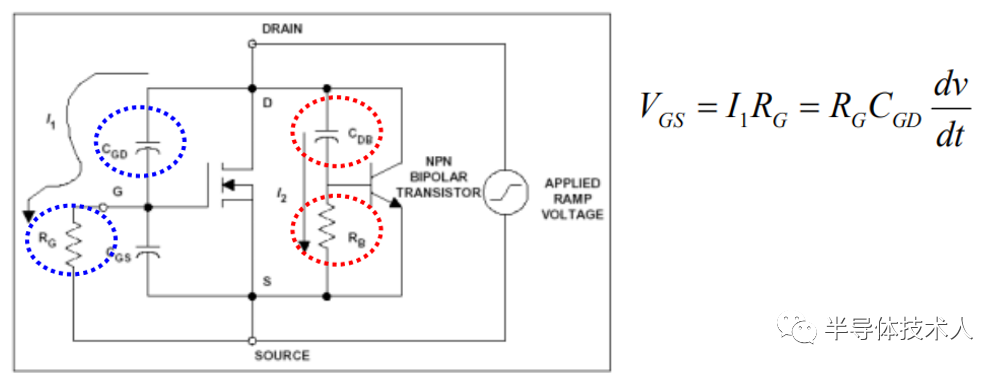

如下图(2)所示,dV/dt失效是由于MOSFET关断时流经寄生电容Cds的瞬态充电电流流过基极电阻RB,导致寄生双极晶体管的基极和发射极之间产生电位差VBE,使寄生双极晶体管导通,引起短路并造成失效的现象。通常,dV/dt越大(越陡),VBE的电位差就越大,寄生双极晶体管越容易导通,从而越容易发生失效问题。

MOSFET的dV/dt失效电流路径示意图(蓝色部分)

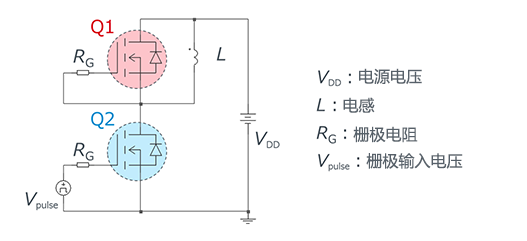

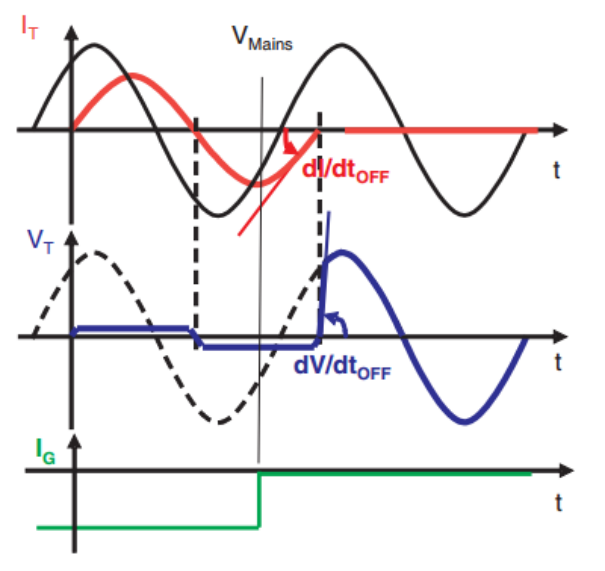

此外,在逆变器电路或Totem-PolePFC等上下桥结构的电路中,反向恢复电流Irr会流过MOSFET。受该反向恢复电流影响的dV/dt,可能会使寄生双极晶体管误导通,这一点需要注意。dV/dt失效与反向恢复特性之间的关系可以通过双脉冲测试来确认。双脉冲测试的电路简图如下:

双脉冲测试的电路简图

关于在双脉冲测试中的详细情况,请参考R课堂基础知识评估篇中的“通过双脉冲测试评估MOSFET的反向恢复特性”。

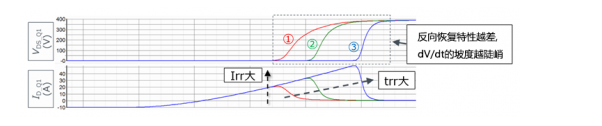

dV/dt和反向恢复电流的仿真结果如下图所示。设MOSFET①~③的栅极电阻RG和电源电压VDD等电路条件相同,仅反向恢复特性不同。图中列出了Q1从续流工作转换到反向恢复工作时的漏源电压VDS和漏极电流(内部二极管电流)ID。

双脉冲测试的仿真结果

一般情况下,与MOSFET①相比,MOSFET③可以说是“反向恢复特性较差(Irr和trr大)”的产品。从这个仿真结果可以看出,反向恢复特性越差,dV/dt的坡度就越陡峭。这一点通过流经电容器的瞬态电流通常用I=C×dV/dt来表示也可以理解。此外,在上述仿真中,Irr的斜率(di/dt)均设置为相同条件,但当di/dt陡峭时,dV/dt也会变陡峭。

综上所述,可以说,在桥式电路中使用MOSFET时,反向恢复特性越差的MOSFET,发生MOSFET的dV/dt失效风险越大。

-

MOSFET

+关注

关注

151文章

10808浏览量

234956 -

寄生电容

+关注

关注

1文章

303浏览量

20372 -

桥式电路

+关注

关注

1文章

26浏览量

11637

发布评论请先 登录

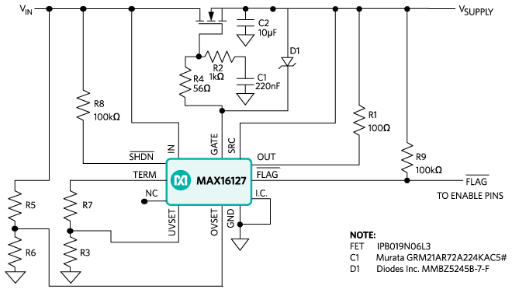

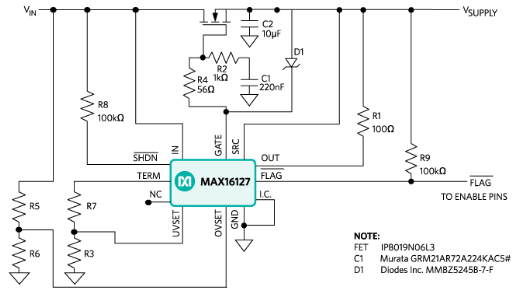

限制稳压器启动时dV/dt和电容的电路

请问开关的电压变化率(dv/dt)和电磁干扰有没有关系?

Analysis of dv/dt Induced Spur

Analysis of dv_dt Induced Spur

电压源型驱动dv/dt的表现

混合动力系统驱动器内dV/dt噪声的来源及解决方案

如何控制电源dV/dt上升时间同时限制通过控制FET的功率损耗

MOSFET的失效机理:什么是dV/dt失效

摆脱高dV/dt电源的优势

“dv/dt”和“di/dt”值:这些值的水平对固态继电器有什么影响?

dV/dt失效是什么意思

dV/dt失效是什么意思

评论