FPGA设计流程

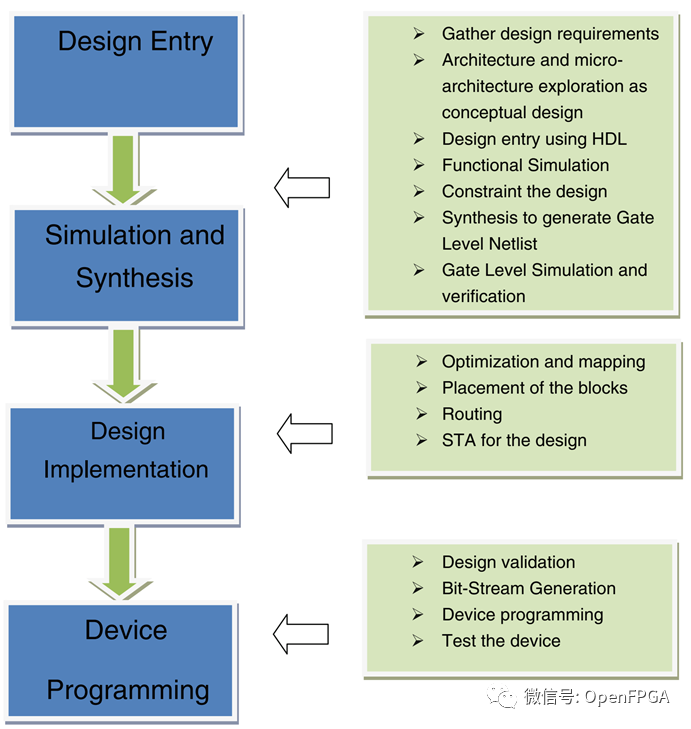

FPGA设计流程包括以下关键步骤,如图9.8所示。

1. 设计输入

2. 设计仿真与综合

3.设计实现

4.设备编程。

图9.8 FPGA设计流程

设计输入

在设计进入之前,需要根据设计规范进行设计规划。设计规范需要转换为体系结构和微体系结构。设计架构和微架构包括将总体设计分解为小模块,以实现预期功能。在架构设计阶段,需要估计内存、速度和功率的需求。根据需要,需要为实现选择FPGA设备。

使用Verilog(.v)或VHDL(.vhd)文件完成设计输入。设计输入后,需要对设计进行仿真,以确保设计的功能正确性。这称为功能仿真。

设计仿真与综合

在功能仿真期间,将输入集应用于设计,以检查设计的功能正确性。尽管在后期的设计周期中可能会出现时间或面积、电源问题,但设计师至少对设计的功能有把握。

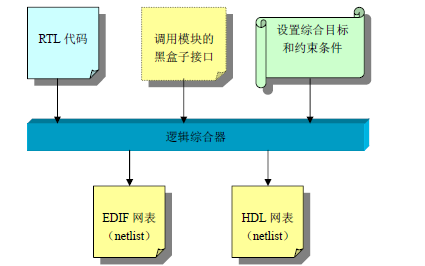

硬件设计工程师的主要目标是生成高效的硬件。综合是将设计抽象的一个层次转换为另一个层次的过程。在逻辑综合中,HDL被转换成网络表。网络列表独立于设备,可以采用标准格式,如电子设计互换格式(EDIF)。

设计实施

该设计经历了translate, map and place and route等步骤。在设计实现过程中,EDA工具将设计转换为所需格式,并根据所需区域将其映射到FPGA。EDA工具通过使用实际逻辑单元或宏单元来执行映射。在映射过程中,EDA工具使用宏单元、可编程互连和IO块。专用模块,如乘法器、DSP和BRAM,也使用供应商工具进行映射。这些块被放置在FPGA内部的预定义几何体上,并通过使用可编程互连来实现预期功能。这一步称为布局和布线。

为了检查设计计时性能以及是否满足约束,将执行时序分析,该分析称为布局后STA。在STA期间,使用与可编程互连相关联的延迟来检查时序路径。提取RC延迟并将其用于时序分析也称为反向注释。

设备编程

FPGA通过使用特定于供应商或专有的位流文件进行编程。位流是需要加载到FPGA中以执行特定硬件设计的二进制数据文件。

如果设计针对特定的FPGA,则EDA工具将生成设备利用率摘要。

用FPGA实现逻辑

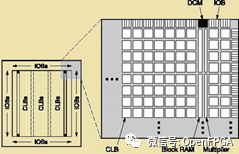

现代FPGA的体系结构包括CLB阵列、块RAM、乘法器、DSP、IOB和数字时钟管理器(DCM)。延迟锁定环(DLL)用于赋值具有均匀时钟偏移的时钟。XILINX SPARTAN系列FPGA的平面图如下图所示。

可配置逻辑块

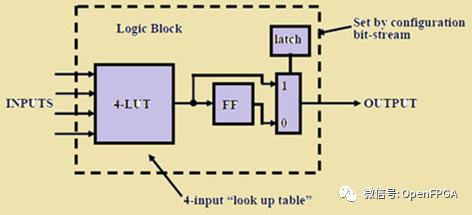

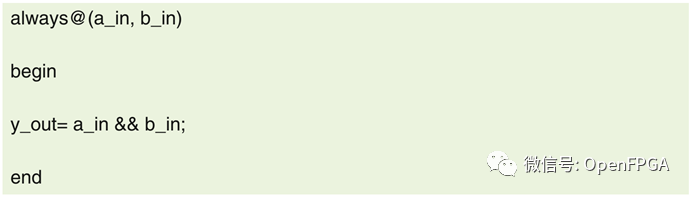

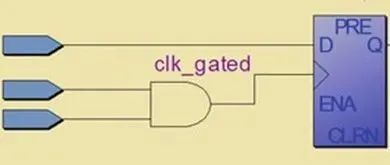

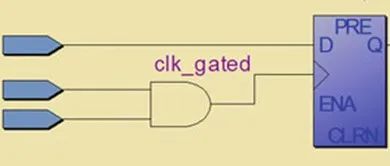

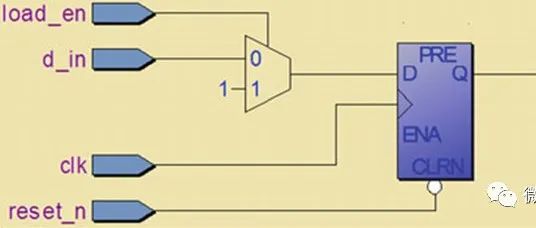

如下图所示,基本CLB由LUT、触发器和多路复用器逻辑组成。配置数据保存在锁存器中。CLB体系结构取决于供应商,由多个LUT、触发器、多路复用器和锁存器组成。下面的Verilog代码是使用单个四输入LUT实现的,称为组合逻辑。

图9.9 Xilinx基本CLB结构

下面的Verilog功能块在实现过程中使用单LUT和单寄存器,因此该逻辑称为时序逻辑。

图9.9所示的CLB也用于实现16位移位寄存器。LUT可以级联以设计较长尺寸的移位寄存器,也可以用于设计的流水线。

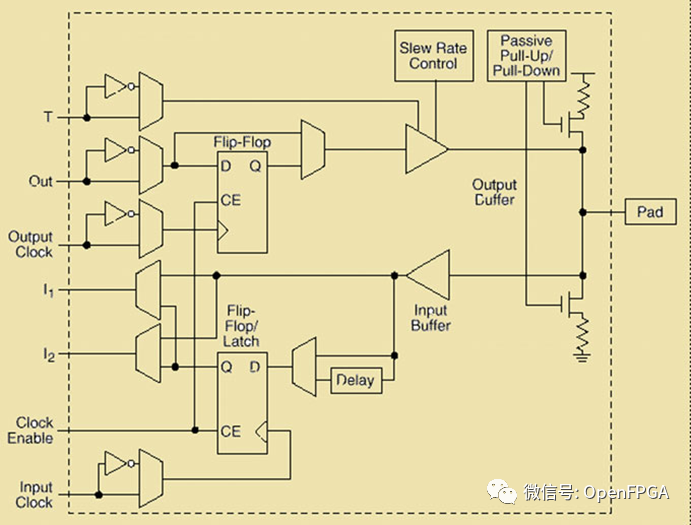

输入-输出块(IOB)

输入-输出块用于建立逻辑与外部世界的接口,由具有三态控制机制的寄存器和缓冲器的数量组成。该块可用于寄存器输入和寄存器输出。

图9.10 Xilinx基本IO块

现代FPGA的IOB结构非常复杂,可以包含许多IO控制支持,其中可能包括DDR、专用高速接口。基本IO块结构如图9.10所示。

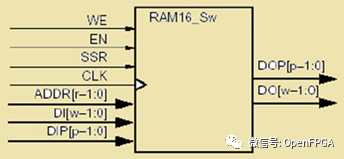

Block RAM

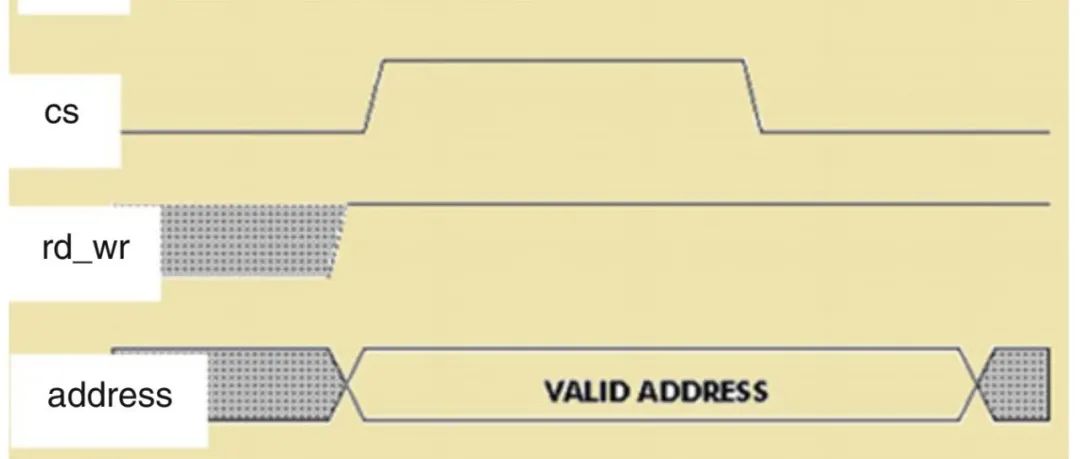

XILINX Spartan-7系列支持可配置18 kbit块的形式组织的200 MHz块RAM。每个块RAM包含18432位,其中16kbit赋值用于数据存储,其余2kbit赋值用于奇偶校验。块RAM可用作单端口存储器或双端口存储器,并具有独立的端口访问。每个端口与独立时钟、时钟启用和写启用同步。读取操作本质上也是同步的,需要启用时钟。块RAM的应用是存储数据、FIFO设计、缓冲区和堆栈,甚至是在设计复杂的状态机时。单端口RAM如图9.11所示。

图9.11 Xilinx单端口Block RAM

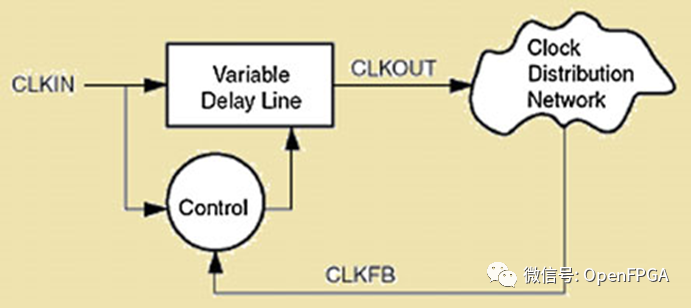

数字时钟管理器(DCM)

Xilinx设备系列使用延迟锁定环(DLL),Altera使用锁相环(PLL)作为时钟管理器。DCM、DLL的作用是提供对相移、时钟偏移和时钟频率的完全控制。DCM、DLL支持以下功能。

相移•时钟偏移消除

频率综合。

DCM由可变延迟线和时钟赋值网络组成,基本框图如图9.12所示。

图9.12 Xilinx基本DLL块

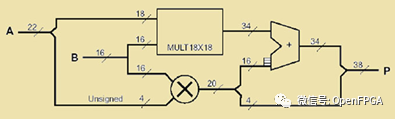

乘法器

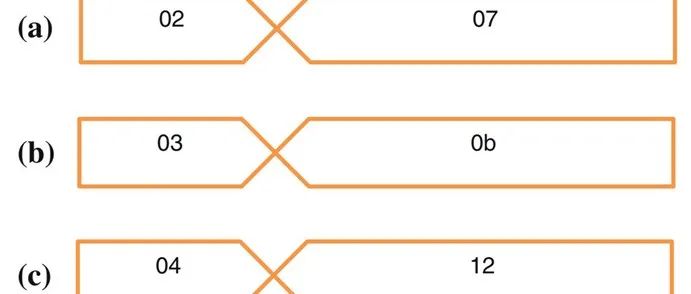

所有Spartan7 FPGA都有两个18位输入,并生成36位输出。乘法器为嵌入式块,每个设备有4~104个嵌入式乘法器块。嵌入式乘法器的主要优点是,与基于CLB的乘法器相比,它需要更少的功耗。它们用于以最小的通用资源实现快速算术函数。可以使用路由资源级联乘法器,下图显示了配置为22位乘以16位的乘法器,以生成38位输出的乘法器可用于有符号或无符号数字乘法。乘法器广泛应用于DSP应用中。基本块如图9.13所示。

图9.13 Xilinx基本乘法器块

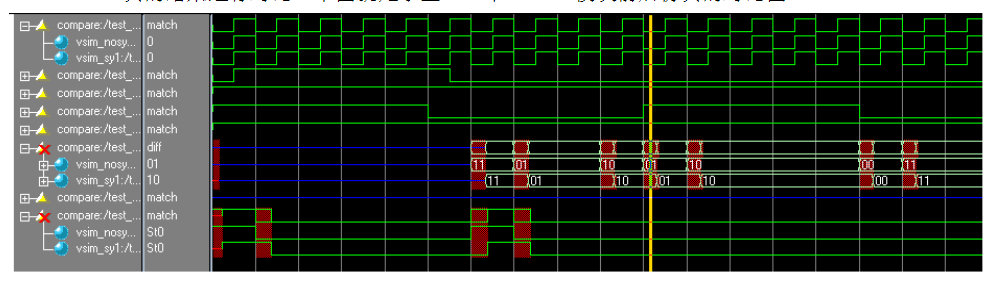

FPGA中仿真概念

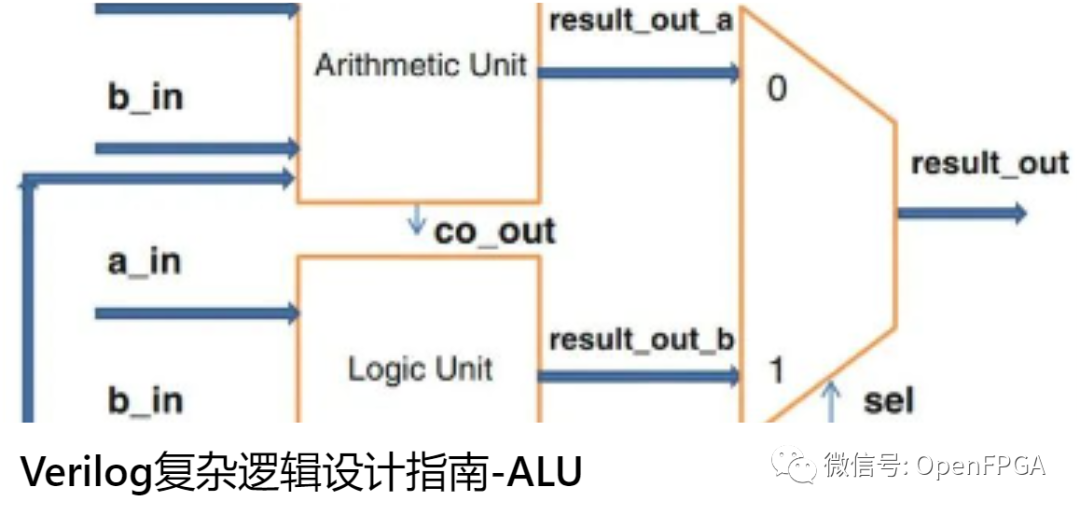

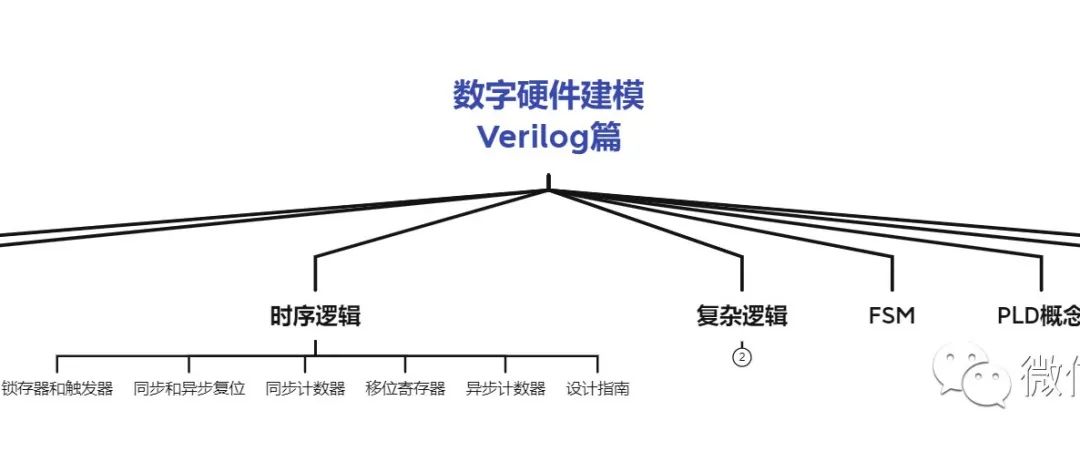

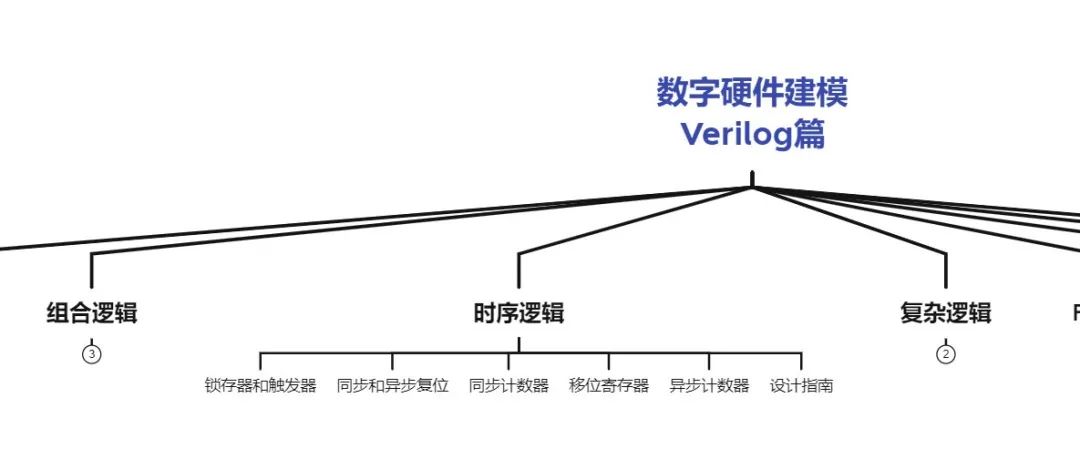

Verilog复杂逻辑设计指南-奇偶校验生成器和校验器及筒式移位器

Verilog时序电路设计指南

Verilog时序逻辑硬件建模设计(五)异步计数器&总结

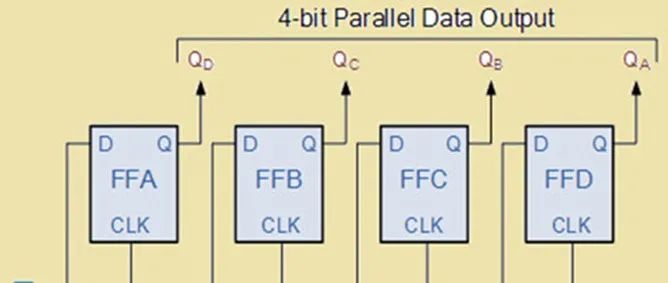

Verilog时序逻辑硬件建模设计(四)移位寄存器

Verilog时序逻辑硬件建模设计(三)同步计数器

Verilog时序逻辑硬件建模设计(二)同步和异步复位

Verilog时序逻辑硬件建模设计(一)锁存器D-latch和触发器Flip-Flop

Verilog组合逻辑设计指南

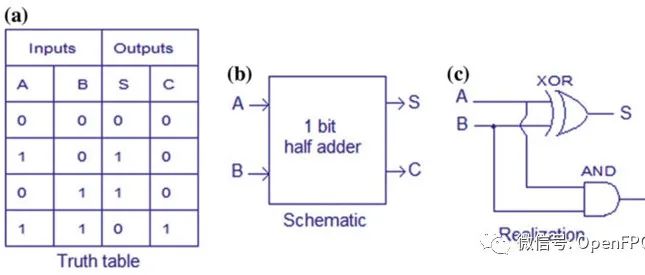

组合逻辑硬件建模设计(二)算术电路

Verilog 里面,always,assign和always@(*)区别

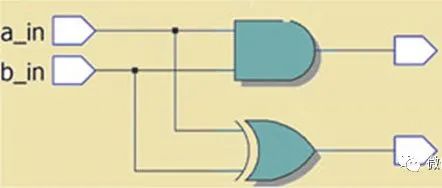

组合逻辑硬件建模设计(一)逻辑门

数字硬件建模-重新从另一方面理解Verilog(二)

数字硬件建模-从另一方面理解Verilog(一)

数字硬件建模综述

审核编辑 :李倩

-

FPGA

+关注

关注

1655文章

22282浏览量

630076 -

仿真

+关注

关注

53文章

4404浏览量

137645

原文标题:FPGA设计流程

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

华为FPGA设计流程指南

华为FPGA设计流程指南

FPGA的设计流程是怎样的

从赛灵思FPGA设计流程看懂FPGA设计

FPGA设计流程“又臭又长”?从eda工具理解超级简单!

FPGA的设计流程是怎么样的?FPGA设计流程指南详细资料免费下载

FPGA设计流程

FPGA设计流程

评论