Vivado自带的仿真,个人觉得跑一些小模块的仿真还是可以的,不过跑大的仿真系统,容易无体验感,建议用第三方工具,这边就直接对ModelSim下手了,接下来介绍下这两者联合仿真的操作。

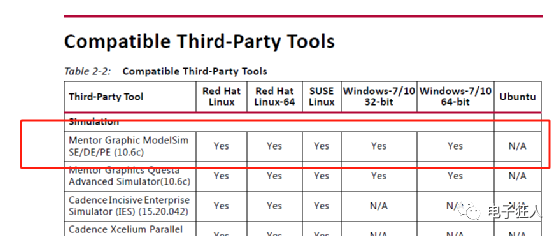

首先确定下自己的Vivado版本和适配的ModelSim版本,可以在ug973中,找到对应的版本,比如我用的Vivado是2018.2的,然后匹配的ModelSim是10.6c的版本。(有时候版本不匹配也能用,不过还是建议尽量匹配版本的好,省得出一些奇怪的问题)

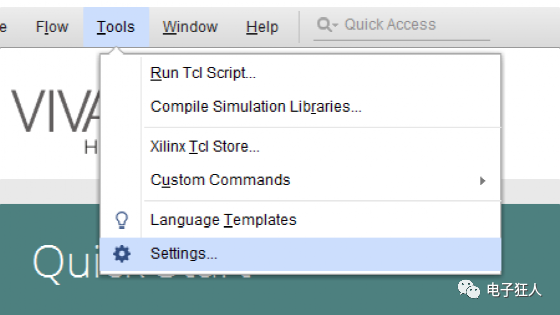

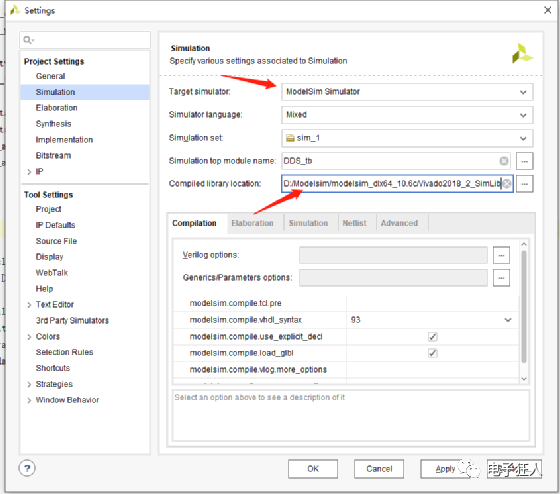

然后准备编译仿真库,打开Vivado,先打开Settings的仿真器配置 (注:我因为装过多个版本,仿真器要换成最16.c的版本,不然编译结果会因为版本不匹配出问题)

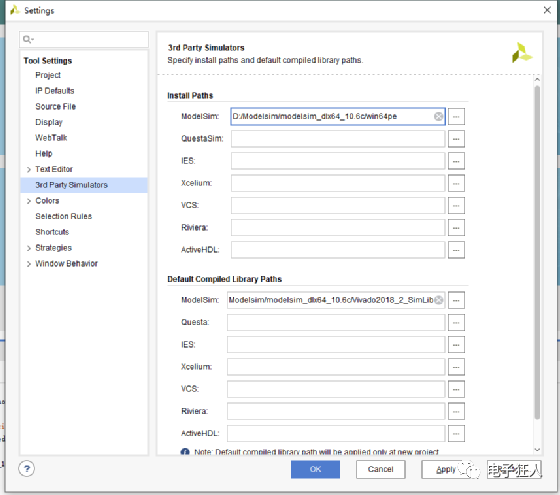

ModelSim的安装路径换成16.c版本的位置,库路径也设置好对应的位置,然后就可以OK保存并关闭了

ModelSim的安装路径换成16.c版本的位置,库路径也设置好对应的位置,然后就可以OK保存并关闭了

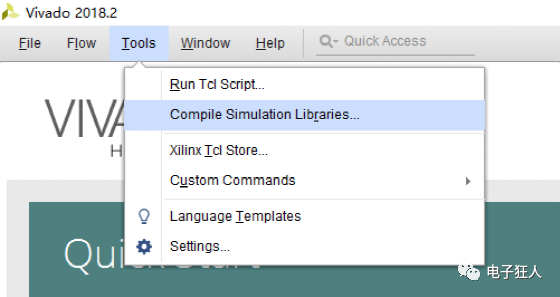

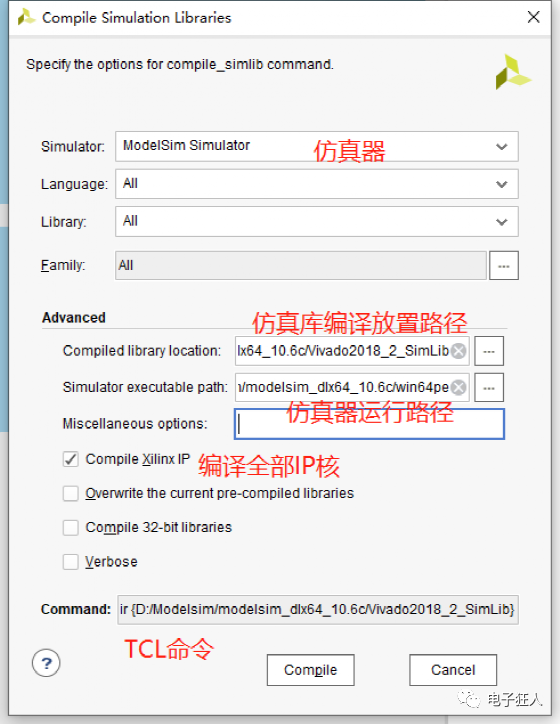

接着在菜单栏中选 Tools > Compile Simulation Libraries

设置项里选好仿真器(此处为ModelSim),编译后的仿真库放置路径(就填上面设置的那个新的仿真库路径),ModelSim程序的路径,IP核编译那项别取消了,是为了编译Xlinx全部IP核的,其他项保持默认即可;TCL的命令就是根据这些配置生成的,然后点Compile就可以开始慢慢等编译结果了。

经过漫长的等待。。。。。。

结果出来了,检查下结果.......

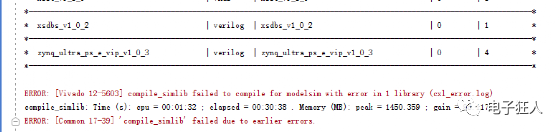

ERROR: [Vivado 12-5603] compile_simlib failed to compile for modelsim with error in 1 library

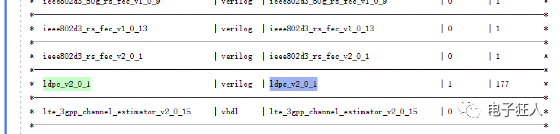

看着红彤彤的ERROR,心里有那么一丝丝小慌,然后往上翻,看看哪ERROR了

查到是ldpc编码的这个IP核出了问题,这个平常也没用到,就直接无视这个错误了(要是你们的没错误,就更好了,这个好像是因为系统是64位导致的,具体就懒得深究了)…… 如果是出现很多errors,就建议先检查下版本是否匹配上了,不然也不会疯狂报错…… 就接着往下说吧~ 打开要仿真的工程,然后对打开Settings,因为创建的工程默认是用的自带的仿真配置,所以需要改下仿真设置,首先将 Target simulator 改为 ModelSim Simulator,其次仿真库的位置也需要检查下是不是刚刚编译好的库对应的路径,检查无误就可以点OK,开始后面的了

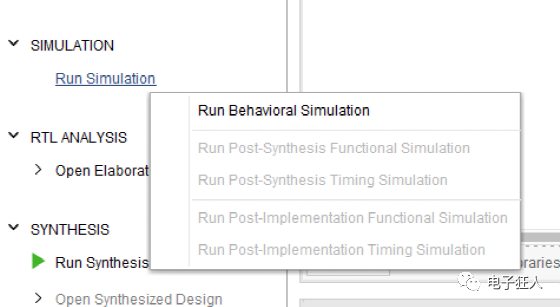

直接运行仿真

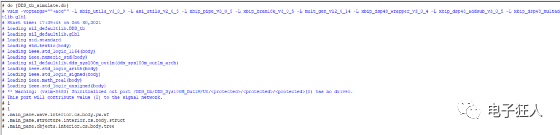

过一小会儿,Modelsim就被Vivado调用了,观察窗口的输出,正常无误

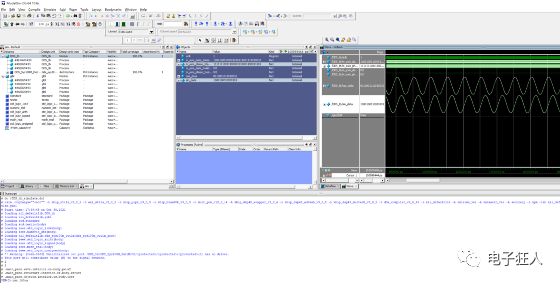

接着运行100us的仿真

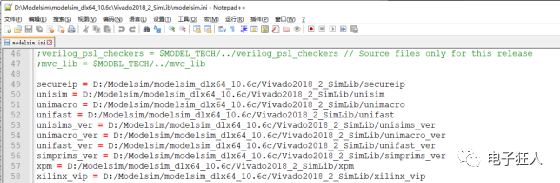

也能正常运行,联合仿真OK~~ 最后补一点,假如自己不想编译库,想直接拿别人编好的,则拷贝好库后,还需要对库的初始化文件做对应的修改,找到库路径下的modelsim.ini(注:不要弄错成ModelSim安装路径下的那个ini了),然后用编辑器打开

可以看到这些库都有以绝对路径的形式链接,所以如果是从别的地方拷过来的,或者你打算换个路径放仿真库,那么就需要将旧的路径改为新的路径,然后其他的使用操作就和上面的一模一样了。

-

仿真

+关注

关注

53文章

4406浏览量

137661 -

ModelSim

+关注

关注

5文章

174浏览量

48876 -

Vivado

+关注

关注

19文章

846浏览量

70463

原文标题:Vivado与ModelSim的联合仿真

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

利用 NucleiStudio IDE 和 vivado 进行软硬件联合仿真

Hbirdv2在vivado2018.3上的仿真工作

Vivado仿真之后没有出现仿真结果的解决方法

利用vivado实现对e200_opensource 蜂鸟E203一代的仿真

Vivado仿真e203_hbirdv2跑whetstone跑分(开源)

在VIVADO中对NICE进行波形仿真的小问题的解决

Nucleistudio+Vivado协同仿真教程

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

NVIDIA助力构建人形机器人全身遥操作仿真平台

【紫光同创盘古100Pro+开发板,MES2L676-100HP教程】盘古676系列——Modelsim的使用和do文件编写

Vivado Design Suite用户指南:逻辑仿真

Vivado与ModelSim的联合仿真操作

Vivado与ModelSim的联合仿真操作

评论