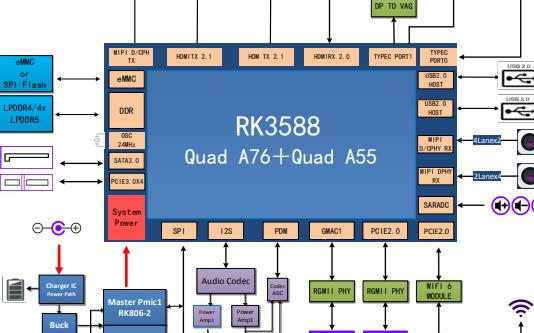

RK3588作为瑞芯微旗舰级SoC,其PCIe控制器凭借灵活的链路拆分能力与丰富特性,成为连接NVMe、WiFi、AI加速卡等外设的核心桥梁。本文融合硬件资源解析、3大拆分方案实战、关键配置步骤及避坑要点,附带可视化脑图,助力开发者快速落地PCIe相关项目。

一、RK3588 PCIe核心硬件资源

1.1控制器与PHY对应关系

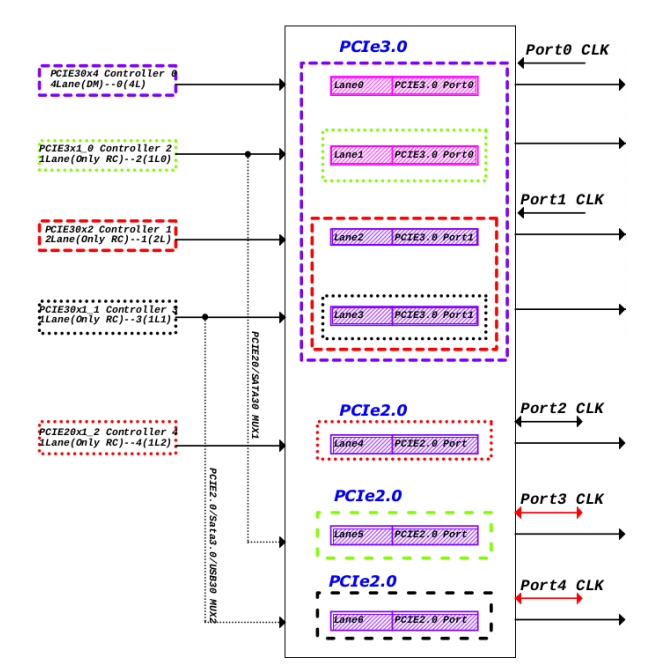

RK3588的控制器与PHY绑定存在固定规则,拆分配置前需明确对应关系:

•pcie3x4(4Lane):仅能配合pcie30phy的Port0(4L/2L/1L模式);

•pcie3x2(2Lane):仅能配合pcie30phy的Port1(2L/1L模式);

•pcie2x1l0/pcie2x1l1:可绑定pcie30phy(拆分后1Lane)或comboPHY;

•pcie2x1l2:仅绑定comboPHY(如combphy0_ps),与SATA复用。

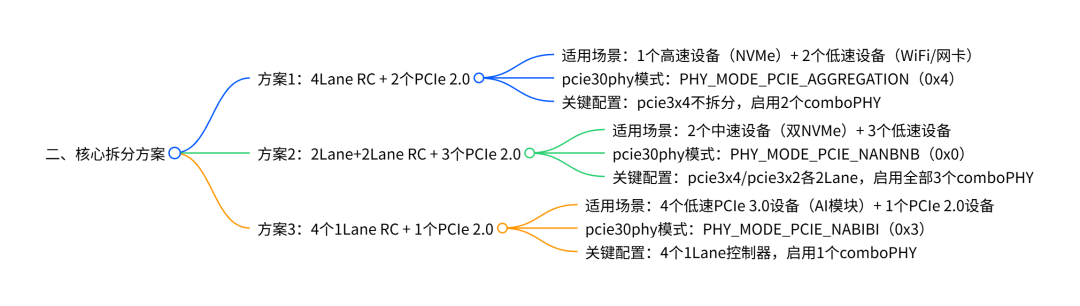

二、3大核心拆分方案

2.1方案1:4Lane RC + 2个PCIe 2.0(基础高速方案)

① pcie30phy与高速控制器配置

// pcie30phy:4Lane聚合模式&pcie30phy {rockchip,pcie30-phymode =; status ="okay";};//pcie3x4:4Lane RC(支持NVMe等高速设备)&pcie3x4 {reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;//PERST#复位信号(必配)vpcie3v3-supply = <&vcc3v3_pcie30>;//3.3V供电(含外置晶振)status ="okay";//若需EP模式,替换compatible:// compatible ="rockchip,rk3588-pcie-ep","snps,dw-pcie";};

②低速控制器与comboPHY配置

// 启用comboPHY(禁用SATA复用)&combphy1_ps { status ="okay"; };&combphy2_psu { status ="okay"; };&sata0 { status ="disabled"; };// 避免与comboPHY冲突// pcie2x1l0:配合combphy1_ps(PCIe模式)&pcie2x1l0 {phys = <&combphy1_ps PHY_TYPE_PCIE>;// 指定PCIe模式reset-gpios = <&gpio4 RK_PA5GPIO_ACTIVE_HIGH>;// 独立复位status ="okay";};// pcie2x1l1:配合combphy2_psu&pcie2x1l1 {phys = <&combphy2_psu PHY_TYPE_PCIE>;reset-gpios = <&gpio4 RK_PA2GPIO_ACTIVE_HIGH>;status ="okay";};

③供电配置(vcc3v3_pcie30)

vcc3v3_pcie30: vcc3v3-pcie30 {compatible ="regulator-fixed";regulator-name ="vcc3v3_pcie30";regulator-min-microvolt = <3300000>;regulator-max-microvolt = <3300000>;enable-active-high;gpios = <&gpio3 RK_PC3GPIO_ACTIVE_HIGH>;// PWREN控制startup-delay-us = <5000>;// 晶振稳定时间(必配,避免时钟异常)vin-supply = <&vcc12v_dcin>;};

2.2方案2:2Lane+2Lane RC + 3个PCIe 2.0(平衡方案)

①核心拆分配置(pcie30phy +双2Lane控制器)

// pcie30phy:2+2拆分模式&pcie30phy {rockchip,pcie30-phymode =; status ="okay";};//pcie3x4:降为2Lane RC&pcie3x4 {num-lanes = <2>;//强制2Lane(必配,拆分后需指定)reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;vpcie3v3-supply = <&vcc3v3_pcie30>;status ="okay";};//pcie3x2:2Lane RC&pcie3x2 {reset-gpios = <&gpio4 RK_PB0 GPIO_ACTIVE_HIGH>;vpcie3v3-supply = <&vcc3v3_pcie30>;status ="okay";};

② 3个PCIe 2.0控制器配置

// 启用全部3个comboPHY&combphy0_ps { status ="okay"; };&combphy1_ps { status ="okay"; };&combphy2_psu { status ="okay"; };// pcie2x1l0~l2分别绑定不同comboPHY&pcie2x1l0 {phys = <&combphy1_ps PHY_TYPE_PCIE>;reset-gpios = <&gpio4 RK_PA5GPIO_ACTIVE_HIGH>;vpcie3v3-supply = <&vcc3v3_pcie30>;status ="okay";};&pcie2x1l1 {/* 同pcie2x1l0,复位GPIO改为RK_PA2 */};&pcie2x1l2 {/* 同pcie2x1l0,phys改为&combphy0_ps,复位GPIO改为RK_PC1 */};

2.3方案3:4个1Lane RC + 1个PCIe 2.0(多设备方案)

① 4个1Lane控制器配置

// pcie30phy:4×1拆分模式&pcie30phy {rockchip,pcie30-phymode =; status ="okay";};//pcie3x4:降为1Lane RC&pcie3x4 {num-lanes = <1>;//强制1Lanereset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;vpcie3v3-supply = <&vcc3v3_pcie30>;status ="okay";};//pcie3x2:降为1Lane RC&pcie3x2 {num-lanes = <1>;reset-gpios = <&gpio4 RK_PB0 GPIO_ACTIVE_HIGH>;vpcie3v3-supply = <&vcc3v3_pcie30>;status ="okay";};//pcie2x1l0/l1:绑定pcie30phy(1Lane)&pcie2x1l0 {phys = <&pcie30phy>;//绑定pcie30phy(非comboPHY)reset-gpios = <&gpio4 RK_PA5 GPIO_ACTIVE_HIGH>;vpcie3v3-supply = <&vcc3v3_pcie30>;status ="okay";};&pcie2x1l1 {/* 同pcie2x1l0,复位GPIO改为RK_PA2 */};

② 1个PCIe 2.0控制器配置

// 启用1个comboPHY(禁用SATA)&combphy0_ps { status ="okay"; };&sata0 { status ="disabled"; };&pcie2x1l2 {phys = <&combphy0_ps PHY_TYPE_PCIE>;reset-gpios = <&gpio4 RK_PC1GPIO_ACTIVE_HIGH>;vpcie3v3-supply = <&vcc3v3_pcie30>;status ="okay";};

三、关键配置与内核选项

3.1 DTS参数详解表

|

参数名称

|

配置位置

|

取值示例

|

核心作用

|

避坑要点

|

|

rockchip,pcie30-phymode

|

pcie30phy节点

|

PHY_MODE_PCIE_AGGREGATION(0x4)

|

定义pcie30phy拆分模式

|

必须与控制器lane数量匹配,不可错配

|

|

num-lanes

|

控制器节点

|

<1>、<2>、<4>

|

指定控制器使用的lane数

|

拆分后需强制配置,如方案3中pcie3x4设为<1>

|

|

reset-gpios

|

控制器节点

|

<&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>

|

外设复位信号

|

每个控制器需独立配置,避免多设备同时复位

|

|

vpcie3v3-supply

|

控制器节点

|

<&vcc3v3_pcie30>

|

控制3.3V供电

|

多控制器共享时,需设为regulator-always-on

|

|

phys

|

控制器节点

|

<&combphy1_ps PHY_TYPE_PCIE>

|

绑定PHY与控制器

|

comboPHY需加PHY_TYPE_PCIE,禁用其他复用

|

|

rockchip,perst-inactive-ms

|

控制器节点

|

<500>

|

调整复位时间

|

外设复位慢时增大(如WiFi模块设为500ms)

|

3.2内核menuconfig必选选项

# 基础PCIe支持CONFIG_PCI=yCONFIG_PCI_DOMAINS=yCONFIG_PCI_MSI=y# 启用MSI中断CONFIG_PCI_MSI_IRQ_DOMAIN=y# RK PCIe驱动CONFIG_PCIE_DW=yCONFIG_PCIE_DW_HOST=yCONFIG_PCIE_DW_ROCKCHIP=y# PHY驱动CONFIG_PHY_ROCKCHIP_SNPS_PCIE3=y# pcie30phy驱动CONFIG_PHY_ROCKCHIP_NANENG_COMBO_PHY=y# comboPHY驱动# 外设支持(按需选择)CONFIG_BLK_DEV_NVME=y# NVMe SSDCONFIG_USB_XHCI_PCI=y# PCIe转USBCONFIG_SATA_AHCI_PLATFORM=y# PCIe转SATA

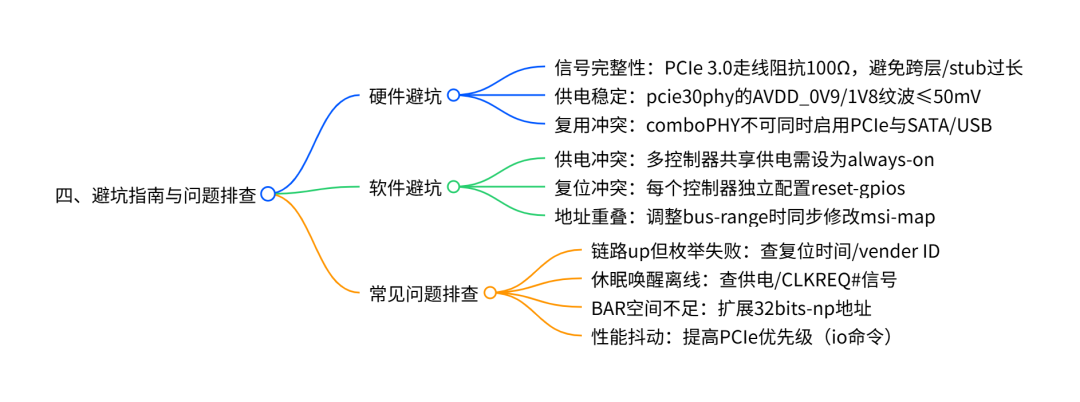

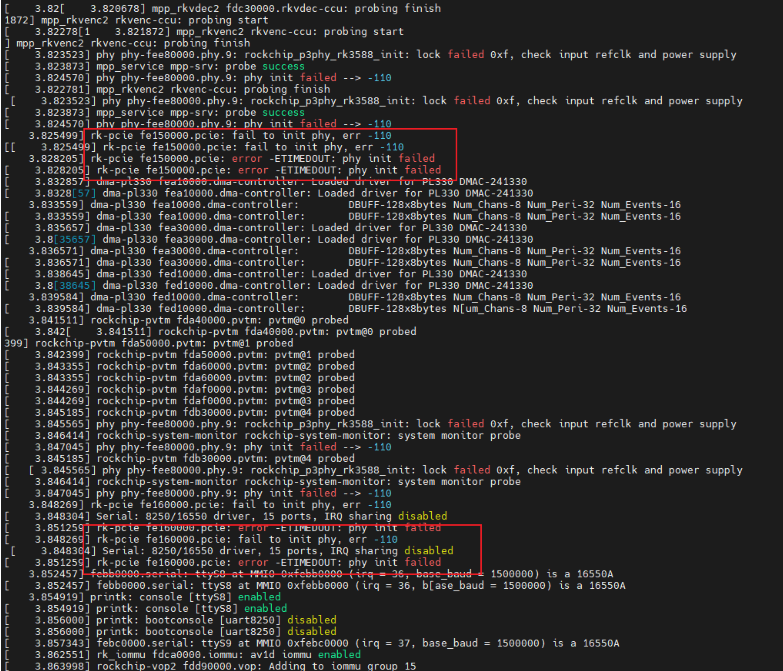

四、避坑指南与问题排查

4.1硬件避坑3大要点

1.信号完整性:PCIe 3.0差分信号走线需控制阻抗(100Ω±10%),长度差≤5mm,避免过孔跨层和过长stub(≤3mm);

2.供电要求:pcie30phy的AVDD_0V9(0.83V~0.99V)、AVDD_1V8(1.62V~1.98V)电压需稳定,纹波≤50mV,避免与其他大电流外设共用电源;

3.复用冲突:comboPHY(如combphy0_ps)支持PCIe/SATA复用,启用PCIe时必须禁用SATA(&sata0 { status = "disabled"; }),反之亦然。

4.2软件避坑4大场景

|

场景

|

常见错误

|

正确做法

|

|

多控制器供电

|

单独给某个控制器配置vpcie3v3-supply

|

共享供电设为regulator-always-on,示例:regulator-always-on;

|

|

拆分后地址重叠

|

未调整bus-range导致地址冲突

|

每个控制器分配独立总线地址,同步修改msi-map:bus-range = <0x30 0x60>;msi-map = <0x3000 &its 0x3000 0x3000>;

|

|

外设复位不充分

|

复位时间不足导致枚举失败

|

增加rockchip,perst-inactive-ms:rockchip,perst-inactive-ms = <500>;

|

|

cache一致性问题

|

使用memcpy访问BAR空间导致异常

|

改用IO专用API:memset_io、memcpy_toio,用户态用循环赋值

|

4.3常见问题排查速查表

|

问题现象

|

可能原因

|

解决方案

|

|

链路up(LTSSM=0x30011)但枚举不到设备

|

1.外设vendor ID为0xffffffff/0x0;2.复位时间不足

|

1.在drivers/pci/probe.c添加vendor ID打印;2.设rockchip,perst-inactive-ms=500

|

|

拆分后部分控制器无响应

|

1.控制器与PHY绑定错误;2.未给pcie30phy未用Port供电

|

1.确认pcie3x4绑定Port0,pcie3x2绑定Port1;2.即使仅用1个Port,另一个Port仍需供电

|

|

休眠唤醒后设备离线

|

1. 3.3V供电休眠时关闭;2.未配置CLKREQ#信号

|

1.供电设为regulator-always-on;2.控制器节点加supports-clkreq属性

|

|

BAR空间分配失败(log含“no space for”)

|

1. 32bits-np地址不足;2. switch无效端口占用资源

|

1.扩展地址(参考文档7.18节修改ranges);2.过滤无效端口(probe.c加黑名单)

|

|

性能抖动(如AI卡帧率波动)

|

PCIe控制器内存优先级低

|

执行命令提高优先级:io -4 0xfdf3a008 0x404(所有控制器通用)

|

通过本文的硬件资源解析、拆分方案实战、配置要点与避坑指南,开发者可快速完成RK3588 PCIe的适配与调试。若需进一步简化配置,可基于本文整理的“拆分方案+参数表”制作项目模板,提高开发效率。

-

Linux

+关注

关注

88文章

11814浏览量

219527 -

PCIe

+关注

关注

16文章

1477浏览量

88906 -

RK3588

+关注

关注

8文章

586浏览量

7552

发布评论请先 登录

实战案例 | RK3588 CAN通信BUG避坑指南

瑞芯微RK3588开发板RK3588 EVB和RK3588S EVB解读

RK3588 EVB开发板原理图讲解【一】

RK3588 EVB开发板原理图讲解【八】 RK3588 power Tree

RK3588 EVB 用户使用指南

rk3588是armv8吗?rk3588硬件资料

Banana Pi BPI-W3 RK3588平台驱动调试篇 [ PCIE篇一 ] - PCIE的开发指南

![Banana Pi BPI-W3 <b class='flag-5'>RK3588</b>平台驱动调试篇 [ <b class='flag-5'>PCIE</b>篇<b class='flag-5'>一</b> ] - <b class='flag-5'>PCIE</b>的开发<b class='flag-5'>指南</b>](https://file1.elecfans.com//web2/M00/AB/FB/wKgaomVC-dmAdRZWAACj2N-ckc0705.jpg)

RK3588 PCIe设备识别失败?一招避坑“非法Class”陷阱

实战复盘:RK3588 SPI+PCIe3x4方案启动修复,从节点配置到驱动适配全解析

一文搞懂 RK3588 PCIe:从硬件资源到拆分配置 + 避坑指南(含脑图)

一文搞懂 RK3588 PCIe:从硬件资源到拆分配置 + 避坑指南(含脑图)

评论