1、综合-优化资源

当选择为none,综合器优化的最少,当选择为full时,综合器优化的最多,选择rebuilt时,工具自动选择一个折中的方案,对当前工程做优化。如果在rebuilt的选项不希望一些信号被优化,则可以调用原语进行约束。

对于模块,想保留该模块的层次结构

(* keep_hierarchy=“yes” )

对于信号,在实际使用中,最好作用于寄存器,有的wire即使约束,也会被优化。

( keep=“true” )

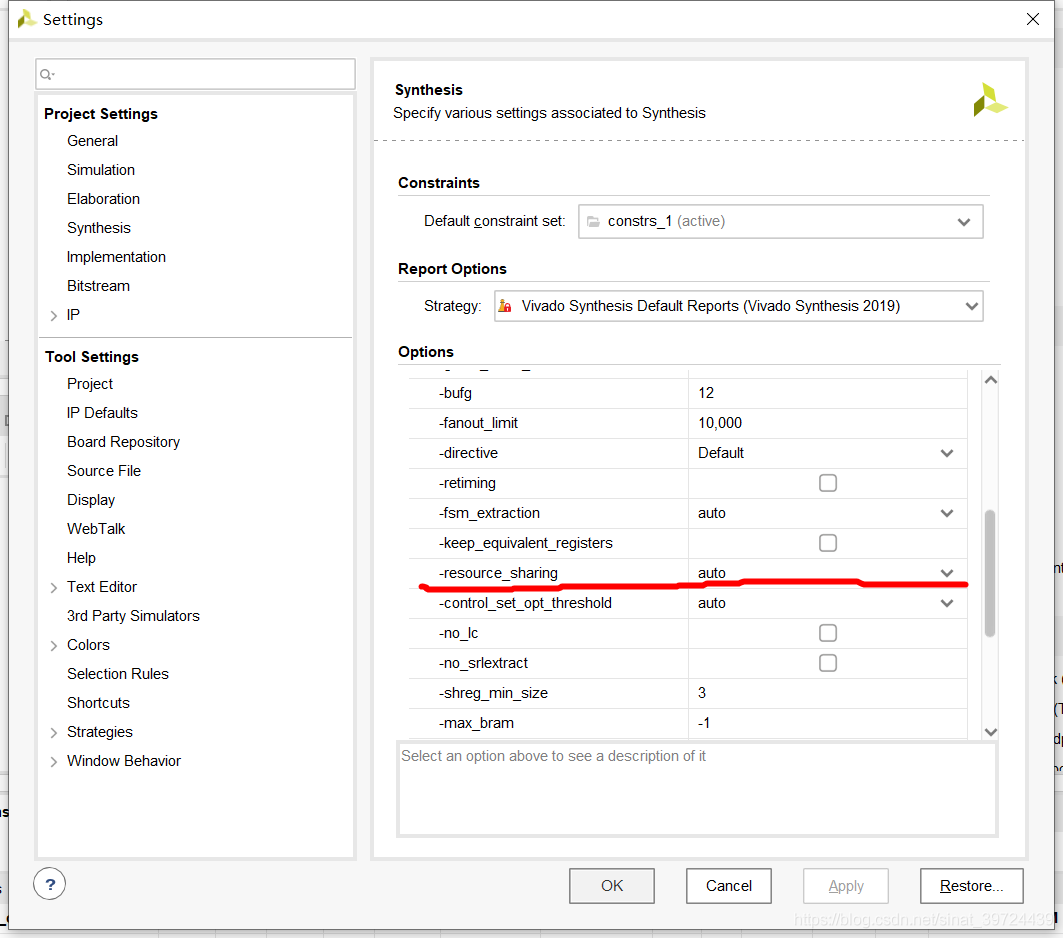

2、综合-资源共享

当选择为on时,使能资源共享,当选择为off时,关闭资源共享,当选择为auto时,综合器会根据时序的余量自动选择是否启动资源共享。

注意,此此选项只对当前代码中加减乘有影响。

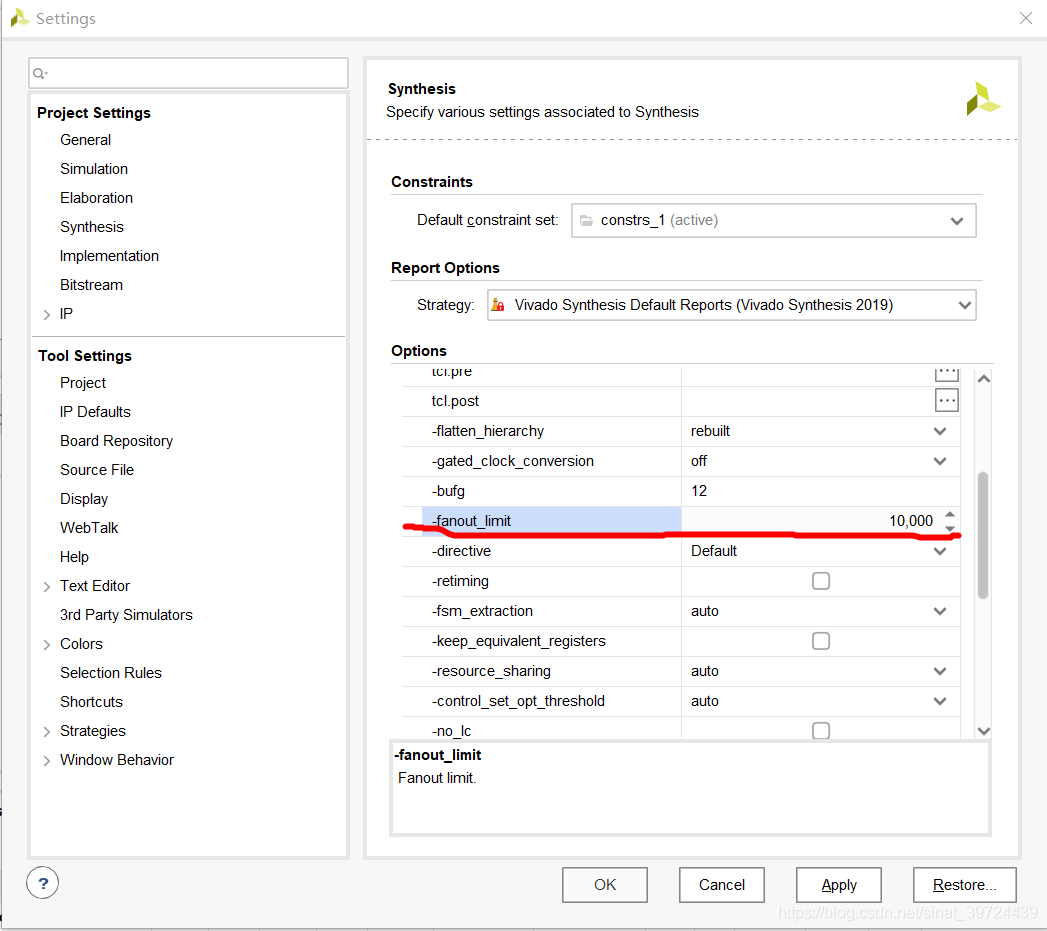

3、综合-扇出限制

默认是10000,这只是一个笼统的全局设置,对复位无效。

对于单一信号的扇出约束,使用约束

( max_fanout= *)

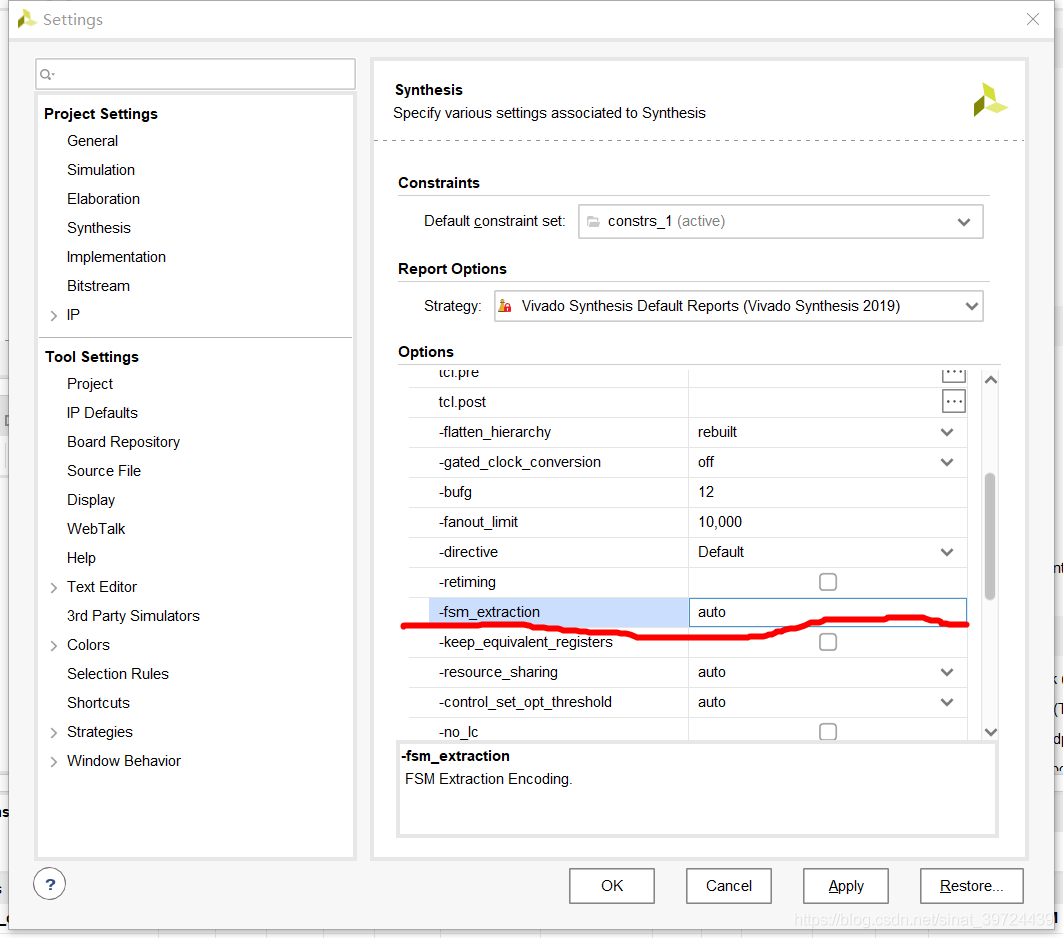

4、状态机的编码方式

当选择为auto时,综合器会根据当前的代码,自动选择最有的编码方式。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Vivado

+关注

关注

19文章

860浏览量

71396

发布评论请先 登录

相关推荐

热点推荐

蜂鸟E203 ARTY综合时出现的unconnected问题怎么解决?

大家好,我尝试用make bit生成bit文件,在vivado综合日志中出现很多模块has unconnected port,只是warning可以成功生成bit文件。在相关模块的例化文件中发现这些模块的对应port没有给出连接,想问下这些port是不必要并不影响模块的使

发表于 11-10 07:28

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

。

vivado加载所有的约束文件,这里需要将旧的文件remove掉,也就是蓝框的两个文件。

进行综合时,如果提示jtag tck的iobuf错误,建议在约束文件中添加如下约束:

set_property

发表于 10-31 08:46

vivado时序分析相关经验

vivado综合后时序为例主要是有两种原因导致:

1,太多的逻辑级

2,太高的扇出

分析时序违例的具体位置以及原因可以使用一些tcl命令方便快速得到路径信息

发表于 10-30 06:58

Windows系统下用vivado将电路烧写到MCU200T板载FLASH的方法

文件自动完成FPGA硬件电路的烧写。这样就不必每次调试软件之前都需要重新打开vivado工程下载bitstream,可以更加方便地进行嵌入式软件开发。

首先打开vivado工程,综合,实现

发表于 10-29 08:21

vcs和vivado联合仿真

我们在做参赛课题的过程中发现,上FPGA开发板跑系统时,有时需要添加vivado的ip核。但是vivado仿真比较慢,vcs也不能直接对添加了vivado ip核的soc系统进行仿真。在这种情况下

发表于 10-24 07:28

FPGA开发板vivado综合、下载程序问题汇总

在做vivado综合时和FPGA下载程序时,我们碰到以下问题,并找出了对应的解决方案。

1.could not open include file”e203_defines.v”问题

在做

发表于 10-24 07:12

Vivado浮点数IP核的一些设置注意点

Vivado浮点数IP核的一些设置注意点

我们在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定义其计算种类及多模式选择。有时多种计算可以用同一个IP核实

发表于 10-24 06:25

Vivado无法选中开发板的常见原因及解决方法

在使用 AMD Vivado Design Suite 对开发板(Evaluation Board)进行 FPGA 开发时,我们通常希望在创建工程时直接选择开发板,这样 Vivado 能够自动配置

关于交流负载模式中的CF值设置(下)

01CF值设置在不同发布平台的关注点(一)学术发布平台在学术平台上,关于交流负载模式中CF值设置的研究成果主要关注理论分析和实验验证。研究人员会深入探讨CF值与负载特性、电路参数之间的数学关系,通过

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

本文讲述了如何使用 One Spin 检查 AMD Vivado Design Suite Synth 的结果(以 Vivado 2024.2 为例)。

关于Vivado综合设置使用总结

关于Vivado综合设置使用总结

评论