一、Aurora配置

开门见山的说,跟DDR/PCIE/GTX这种复杂的IP相比,Aurora配置那是相当的简单。走着。

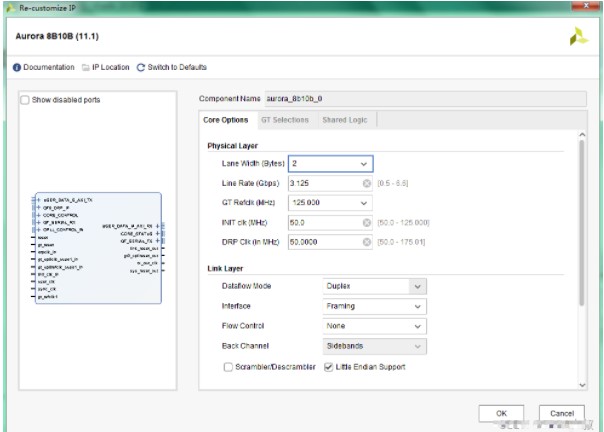

1.1第一页配置

物理层Physical Layer:

Lane Width : 链路位宽,对应用户数据位宽;实际用户数据位宽= Lane Width*Lane的个数(也就是第二页的Lanes)

Lane Rate : 链路数据传输速率,Gbps。我们测试默认3.125G就好。

下面三个时钟在上一篇《时钟和复位》说过,就不再啰嗦了。

链路层Link Layer:

dataflow mode: 数据流模式,可选全双工/ 只接收/ 只发送;根据实际情况选择,为了测试,我们这里选择全双工。

interface:Framing/streaming可选。streaming较简单,大家可以自行去验证。一般使用framing接口,可能是axi4-s接口更方便连接吧。后续介绍都基于Framing接口。

flow control:流控,暂时不选择。

back channel:sidebands/timer 可选,(只有在单工模式才能选择);秋大佬告知这个什么意思,我没用过,先略过。

Scrambler/Descrambler :绕码/解绕,这里不选择

little endian support :小端模式,勾选上就对了。小端模式在不同场合一般有两层意思:①[31:0]这种书写习惯,对应的是[0:31];②假设你的数据是64位,链路宽度是32位,那么一次只能传输32bit,先传输高32bit为大端模式,先传输低32bit为小端模式。

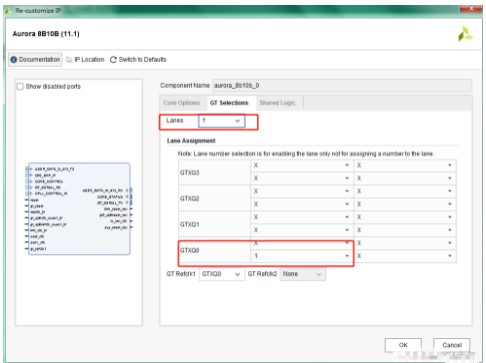

1.2第二页配置

第二页配置主要是对GT的选择。

包括:使用几个GTX,GTX的位置等。根据实际选择,这里做测试默认就好。

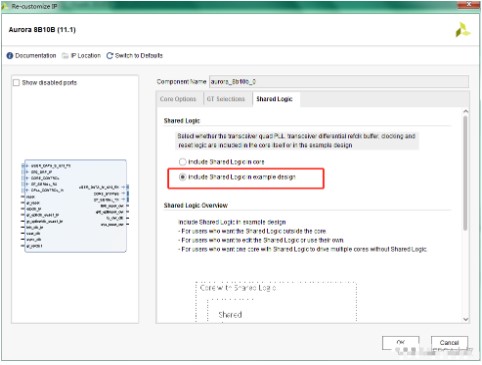

1.3第三页配置

为了学习以及使用的灵活性,我们一般选择将共享逻辑放在example design而不是放入core。

配置部分就介绍完了,使用还是很简单的。再次感谢xilinx!

前面说过,Aurora core支持两种接口模式:framing 和 streaming。

streaming较简单,framing 较通用。

下面我们一起来看下这两种接口。

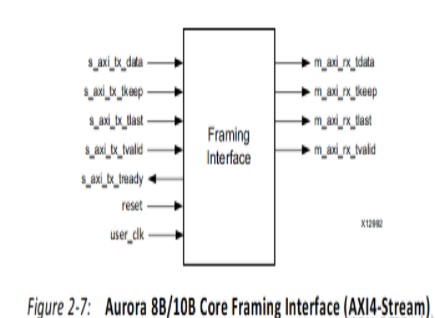

二、Framing接口

2.1 接口信号

发送端:

接收端:

Tips: 其实,在理解了AXI4总线(AXI4-FULL/LITE/STREAM)后,再来看这些信号名,都不需要看文档你就能知道它的意思了。所以,强烈建议把AXI4总线接口先去熟悉一遍。空了,我也将AXI4总线简单整理一下。

2.2理论介绍

传输数据时,用户逻辑需要操纵控制信号让core做以下操作:

1. 当s_axi_tx_tvalid和s_axi_tx_tready都断言时,将需要发送的数据放到数据总线s_axi_tx_tdata。简单来说就是_tvalid和_tready每握手一次,完成一个数据传输。

2. 把数据划分到Aurora 8B/10B channel的各条lane。

3. 使用 s_axi_tx_tvalid 信号来传输数据,用户应用程序可以将_valid信号置为无效来插入空闲字符idles。(用来暂停或停顿。)

4. 暂停数据(即插入空闲)(s_axi_tx_tvalid置为无效)

接收数据:

1. 检测并丢弃控制字节(空闲,时钟补偿,通道PDU(SCP)的开始,通道协议数据单元(ECPDU)的结束和PAD。

2. 置位成帧信号(m_axi_rx_tlast),并指定最后一个数据(m_axi_rx_tkeep)中的有效字节数。

3. 从通道中恢复数据。

4. 通过断言m_axi_rx_tvalid信号来组装数据,以呈现给m_axi_rx_tdata总线上的用户接口。

注意:

仅当同时声明s_axi_tx_tready和s_axi_tx_tvalid(高)时,Aurora 8B / 10B内核才对数据采样。

AXI4-Stream数据仅在帧内时才有效。 帧外的数据将被忽略。 要开始帧,在数据的第一个字位于s_axi_tx_tdata总线上时拉高s_axi_tx_tvalid。 要结束帧,在数据的最后一个字(或部分字)位于s_axi_tx_tdata端口上时拉高s_axi_tx_tlast,并使用s_axi_tx_tkeep指定最后一个数据拍中的有效字节数。

如果帧的长度不超过一个字,则同时使s_axi_tx_tvalid和s_axi_tx_tlast有效。

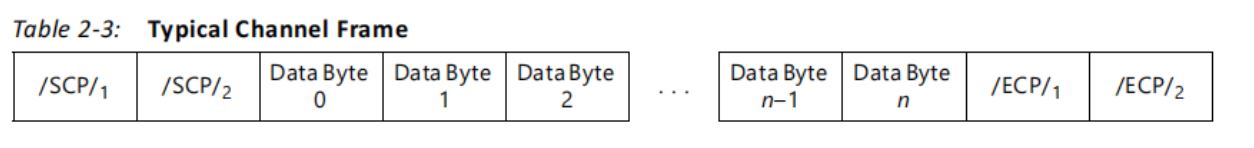

Aurora 8B/10B Frames 帧结构

TX子模块通过TX接口将每个接收到的用户帧转换为Aurora 8B / 10B帧。 通过在帧的开头添加一个2字节的SCP代码组来指示帧的开始(SOF)。 帧的结尾(EOF)通过在帧的末尾添加2字节的通道结束协议(ECP)代码组来表示。 只要没有数据,就会插入空闲代码组。代码组是8B / 10B编码的字节对,所有数据都作为代码组发送,因此具有奇数字节的用户帧在帧末尾附加了一个称为PAD的控制字符,以填充最终的代码组。

Length

用户应用程序通过操纵s_axi_tx_tvalid和s_axi_tx_tlast信号来控制通道帧长度。 Aurora 8B / 10B核分别响应帧开始和帧结束有序集/ SCP /和/ ECP /。

以上基本是对文档的翻译,结合实际使用来看,帧头帧尾部分由核帮你做了。我们只需要将有效数据负载放在s_axi_tx_tdata总线上,通过s_axi_tx_tvalid和s_axi_tx_tlast握手来进行数据传输就好。接收,根据m_axi_rx_tvalid标志来接收有效数据就好。

2.3 接口时序图

接下来,我们再看3个数据发送的例子:

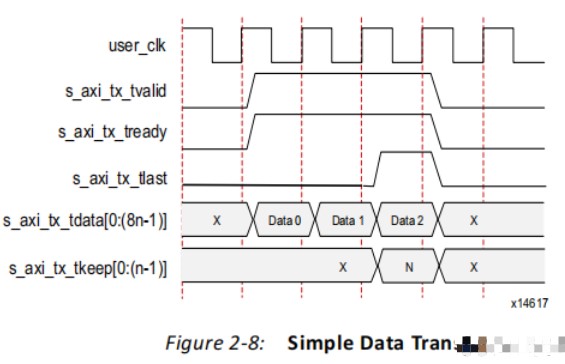

CASE1 : 简单数据传输

如图所示:在s_axi_tx_tvalid和s_axi_tx_tlast同时有效(握手)时,s_axi_tx_tdata总线上的数据传给了Aurora core,再由core发送出去;s_axi_tx_tlast标志着最后一个数据传输;s_axi_tx_tkeep标志着最后一个数据哪些字节是有效的。

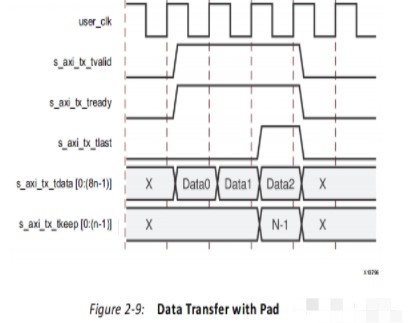

CASE2 : 数据传输with pad(具有奇数字节)

跟case1唯一不同的是,在最后一个数据传输时,由于数据是奇数字节,所以存在无效字节,由tkeep信号来标志有效字节。

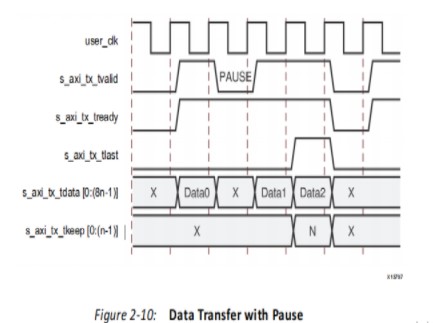

CASE3 : 有中断的数据传输

看图就是了,反正记住一点,在ready/valid握手时,才发生有效数据传输。

如果我们想要暂停数据传输,那么只需要将tvalid信号置为无效,就可以插入空闲字符,其实也就达到了流控的效果。

三、Streaming接口

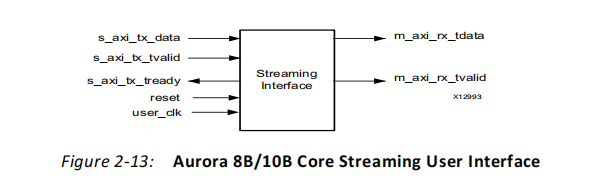

3.1 接口信号

对比framing接口是不是简单很多。

发送:

数据总线s_axi_tx_tdata , 数据有效信号s_axi_tx_tvalid;用户逻辑只需要设计这两个信号就好。同样的,数据传输发生在s_axi_tx_tvalid和s_axi_tx_tready同时有效(握手)时。

接收:

在m_axi_rx_tvalid信号有效时,接收m_axi_rx_tdata数据总线上的数据。

3.3接口时序图

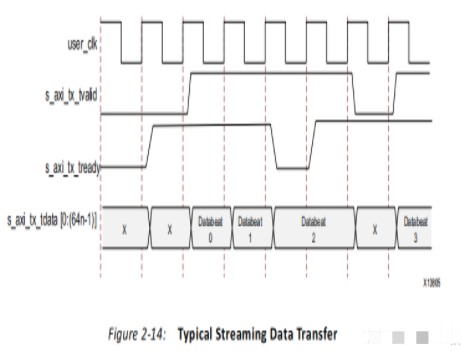

发送:

如下图所示:数据有效传输发生在s_axi_tx_tvalid和s_axi_tx_tready同时有效(握手)时。

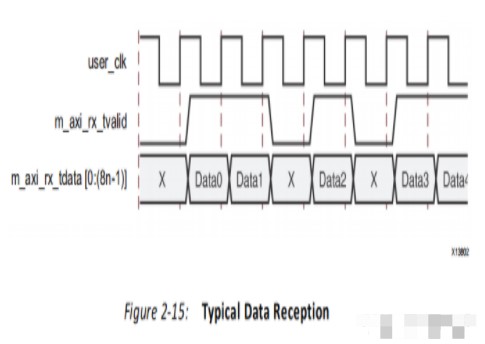

接收:

在m_axi_rx_tvalid信号有效时,接收m_axi_rx_tdata数据总线上的数据。如果来不及使用,必须使用buffer先缓存下来,否则数据丢失。

streaming接口较为简单,就不再啰嗦了。后文介绍基于framing接口。

OK,IP配置完了,下一篇我们介绍example design!

审核编辑:汤梓红

-

接口

+关注

关注

33文章

9444浏览量

156143 -

Xilinx

+关注

关注

73文章

2192浏览量

129929

发布评论请先 登录

睿擎平台网络开发指南:从IP配置到远程控制 | 技术解析

Aurora接口的核心特点和应用场景

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

FPGA利用DMA IP核实现ADC数据采集

借助Cadence工具简化PCB设计流程

Xilinx Shift RAM IP概述和主要功能

详解Xilinx的10G PCS PMA IP

美国多ip服务器租用配置步骤

丰田、Aurora及大陆集团携手NVIDIA,共推高度自动驾驶车型

丰田、Aurora和大陆集团加入NVIDIA合作伙伴行列

SRIO介绍及xilinx的vivado 2017.4中生成srio例程代码解释

Xilinx平台Aurora IP介绍(三)Aurora配置及接口

Xilinx平台Aurora IP介绍(三)Aurora配置及接口

评论