在搭建完Block Design以及硬件代码后,生成bit;

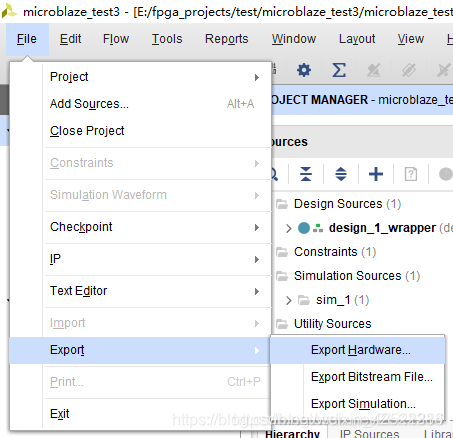

bit文件生成成功后,点击Export Hardware,导出xsa文件:(xsa做连接使用)

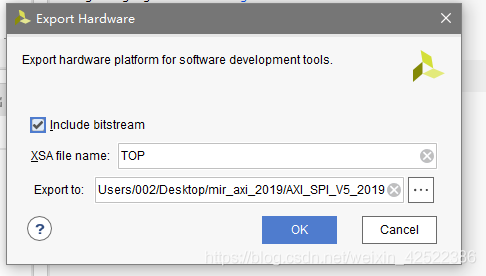

勾选 include bitstream

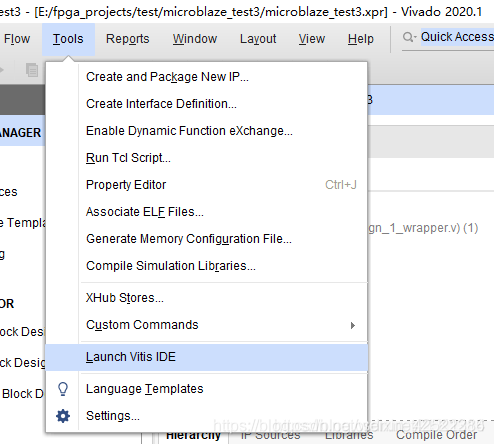

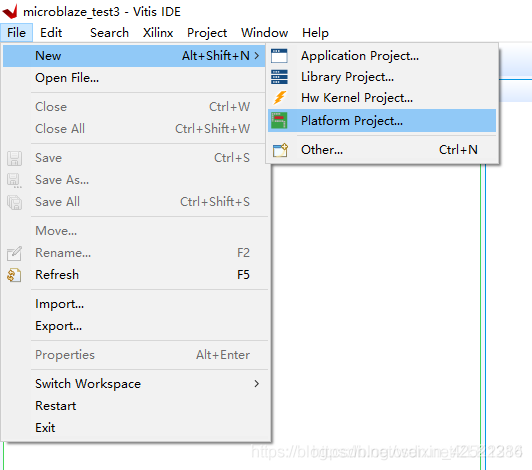

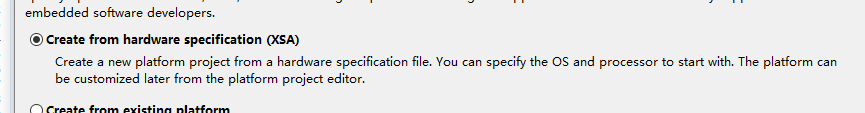

有了xsa文件,就可以启动Vitis 了。

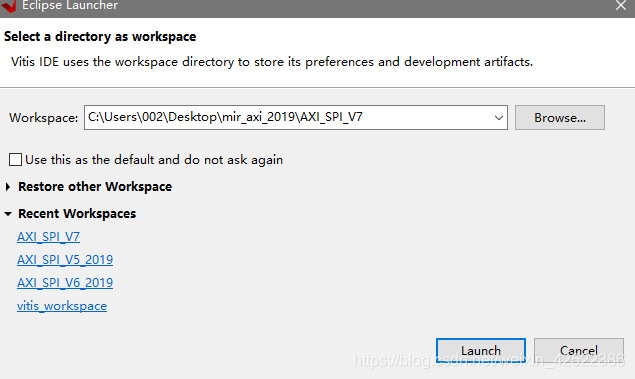

选择工作目录

选择使用xsa后,选择XSA路径即可。完成后bulid project!!!

再建立一个APP project工程,用于代码书写。写完后bulid project!!!

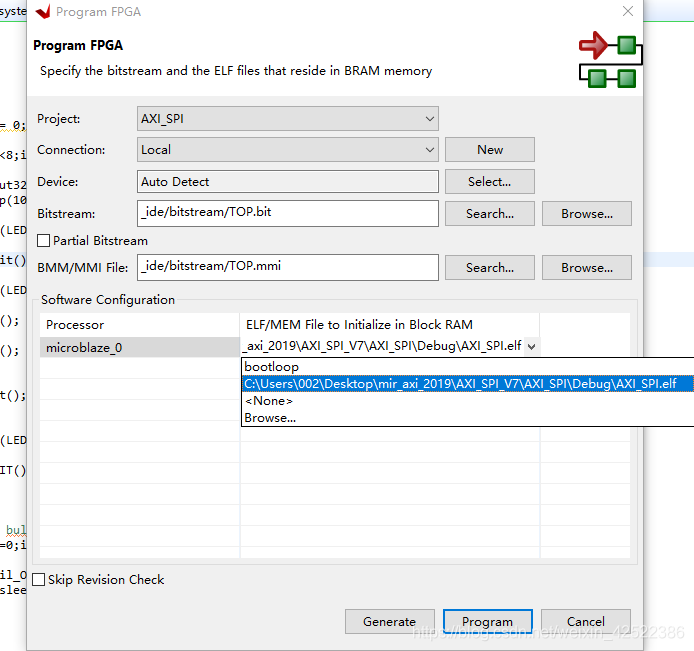

开始固化

固化需要两步。

第一步是在Program FPGA对话框里面,将bit文件和Vitis工程elf文件合并成一个download.bit文件:

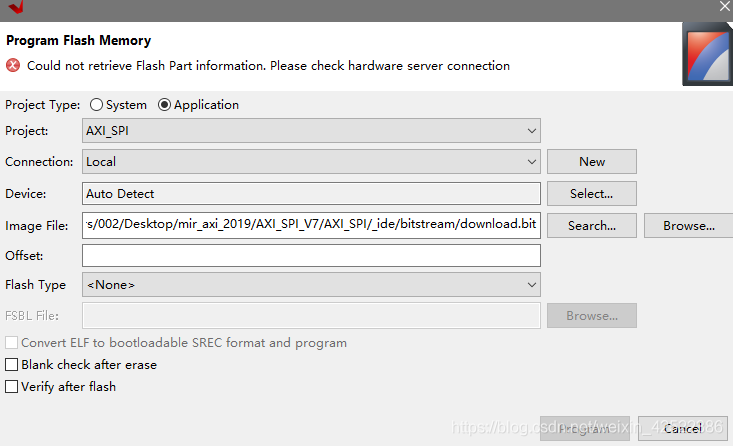

第二步就是在Program Flash对话框中,把合并后的download.bit文件烧写到SPI Flash里面:

选择对应型号flash即可。

若更改vivado代码更改了,新生成了bit文件,然后,整个Vitis工程都必须删了重建!!!!!!

重新建立Platform工程,Build一下,再重新建立Application工程,再Build一下

点Program FPGA生成download.bit,再点Program Flash把download.bit固化到flash

审核编辑:符乾江

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

代码

+关注

关注

30文章

4976浏览量

74388 -

Vitis

+关注

关注

0文章

158浏览量

8427

发布评论请先 登录

相关推荐

热点推荐

3562 单板机 Linux 系统固化完全指南:从 SD 卡启动到 eMMC 永久部署

本文为创龙科技 3562 单板机系统固化操作指南,核心涵盖 SD 启动卡、升级卡制作,以及 eMMC 芯片系统固化与启动验证。文档详细说明专用工具使用、镜像烧录参数配置、多方式启动测试流程

Vivado+Vitis将程序固化的Flash的操作流程

ZYNQ 的程序固化是指将程序代码永久存储到非易失性存储器中,使系统上电后能自动加载运行的过程。主要固化方式:QSPI Flash固化:常用方式,容量小,如启动

基于Vitis Model Composer完成全流程AI Engine开发

基于Vitis Model Composer进行AI Engine(AIE)开发,核心优势体现在AIE专属优化、开发流程简化、灵活的适配性、高效验证及量产适配等方面。

如何在AMD Vitis Unified IDE中使用系统设备树

您将在这篇博客中了解系统设备树 (SDT) 以及如何在 AMD Vitis Unified IDE 中使用 SDT 维护来自 XSA 的硬件元数据。本文还讲述了如何对 SDT 进行操作,以便在 Vitis Unified IDE 中实现更灵活的使用场景。

AMD Vitis AI 5.1测试版现已开放下载

AMD Vitis AI 5.1全新发布——新增了对 AMD Versal AI Edge 系列神经网络处理单元( NPU )的支持。Vitis AI 包含优化的 NPU IP、模型编译工具和部署 API,可在嵌入式平台上实现可扩展的高性能推理。

AMD Vitis AI 5.1测试版发布

AMD Vitis AI 5.1全新发布——新增了对 AMD Versal AI Edge 系列神经网络处理单元 (NPU) 的支持。Vitis AI 包含优化的 NPU IP、模型编译工具和部署 API,可在嵌入式平台上实现可扩展的高性能推理。

E203软核提高CPU时钟频率方法

本文将分享我们团队提高E203软核主频的办法。

查阅芯来科技官方出版的《手把手教你设计CPU——RISC-V处理器篇》教材,我们发现,原本设计的E203主时钟域应该是100MHZ

发表于 10-29 06:19

芯来e203移植开发分享(二)——仿真文件简述与itcm固化程序

根据上次的分享,已经把e203成到verdi与vcs仿真环境下。这次简单介绍一下e203的仿真文件与itcm固化程序的仿真。

仿真文件

简单分析一下e203的自带的仿真文件,跟着上次的分享,我们

发表于 10-27 06:04

ZYNQ UltraScalePlus RFSOC QSPI Flash固化常见问题说明

璞致 ZYNQ UltraScalePlus RFSOC QSPI Flash 固化常见问题说明

发表于 08-08 15:49

•0次下载

如何在Unified IDE中创建视觉库HLS组件

最近我们分享了开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE)和开发者分享|AMD Vitis HLS 系列 2:AM

使用AMD Vitis Unified IDE创建HLS组件

这篇文章在开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE) 的基础上撰写,但使用的是 AMD Vitis Unifie

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此 HLS IP,并使用嵌入式 Vitis 应

中软国际亮相中国核建2025数字生态大会

此前,5月13日至14日,中国核建2025数字生态大会在雄安会展中心隆重召开。大会以“数智赋能新生态,转型共赢创未来”为主题,由中国核学会指导、中国核建成员单位中核华辉承办。中

Vitis软核固化代码流程说明

Vitis软核固化代码流程说明

评论