1、对于AXI4-FULL总线时,握手信号共有5路,包括写地址,写数据,写应答,读地址,读数据。

2、当主机burst写时,每发起一次猝发交易,需要有一笔应答对应。

3、当主机进行读数据时,接受数据即可。

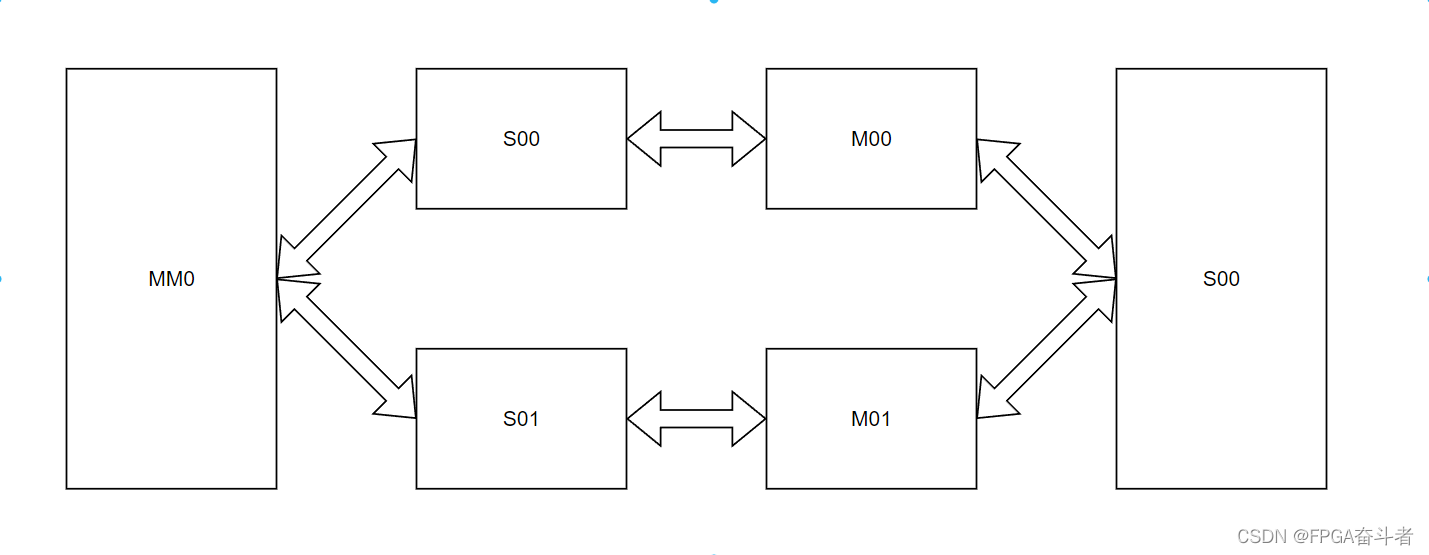

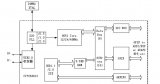

4、具体如图所示

5、共5路信号,每路信号都包括握手信号,ready和valid,当ready和valid都有效时,此时数据才有效,且信号不存在相互等待关系,以免发生死锁现象。

6、包括aw,w,b,ar,r,每路信号都应用FIFO做缓存,使数据对齐。

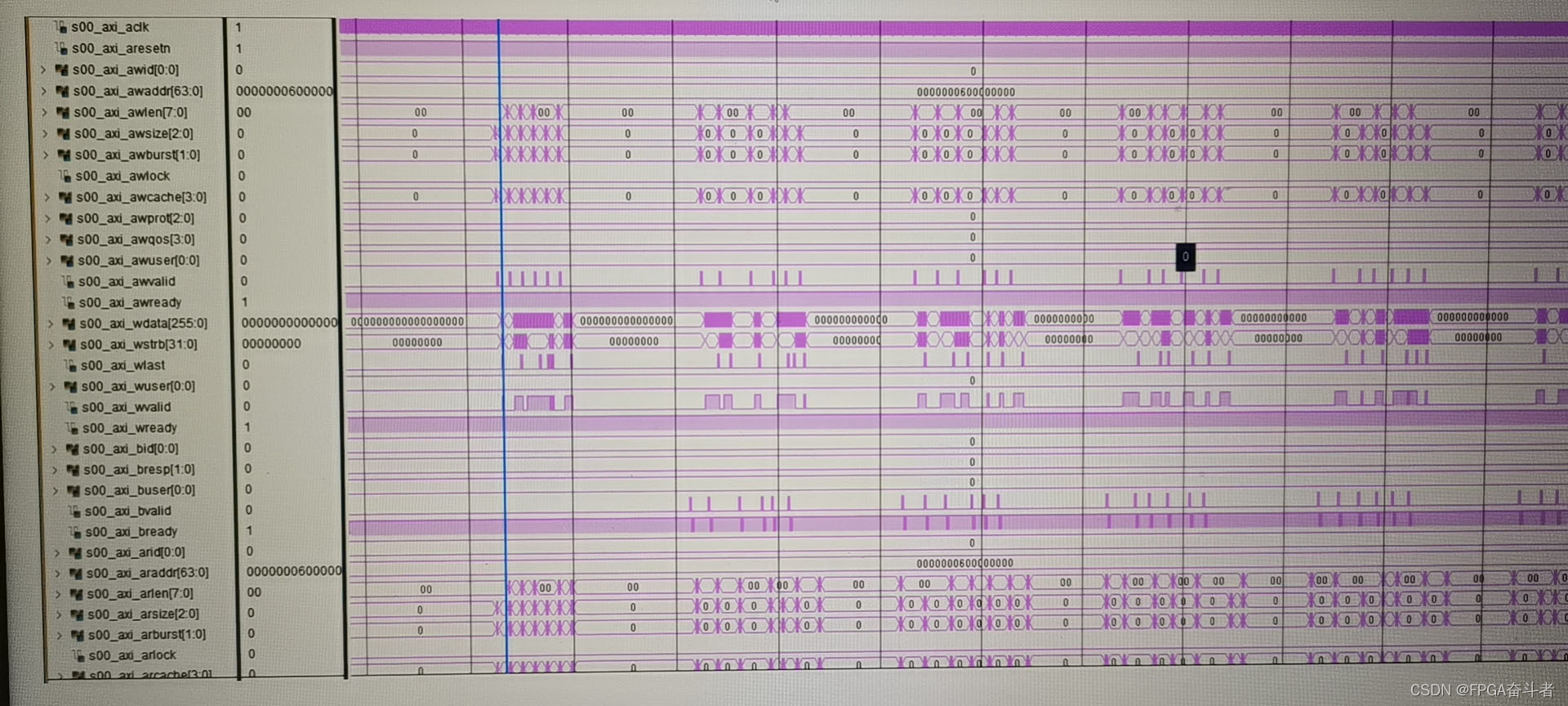

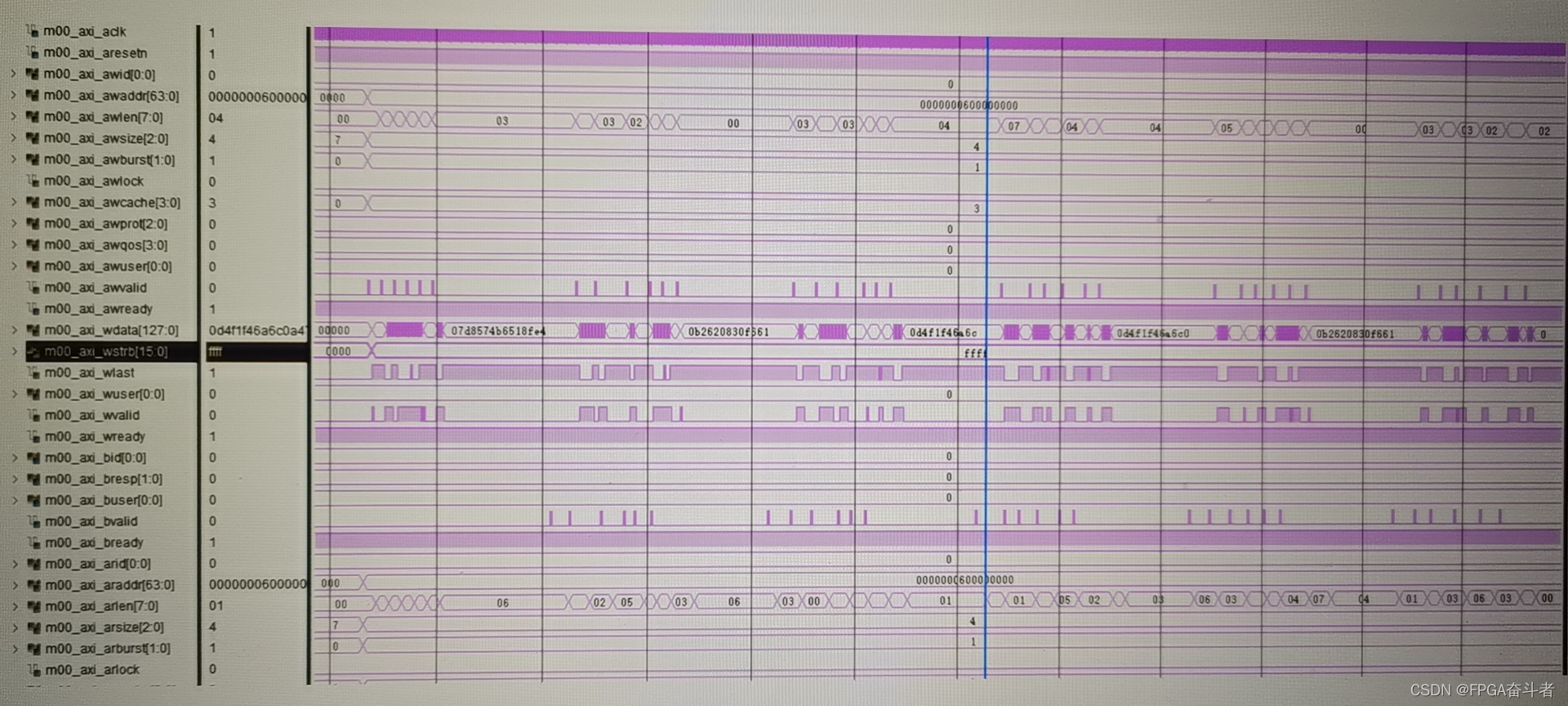

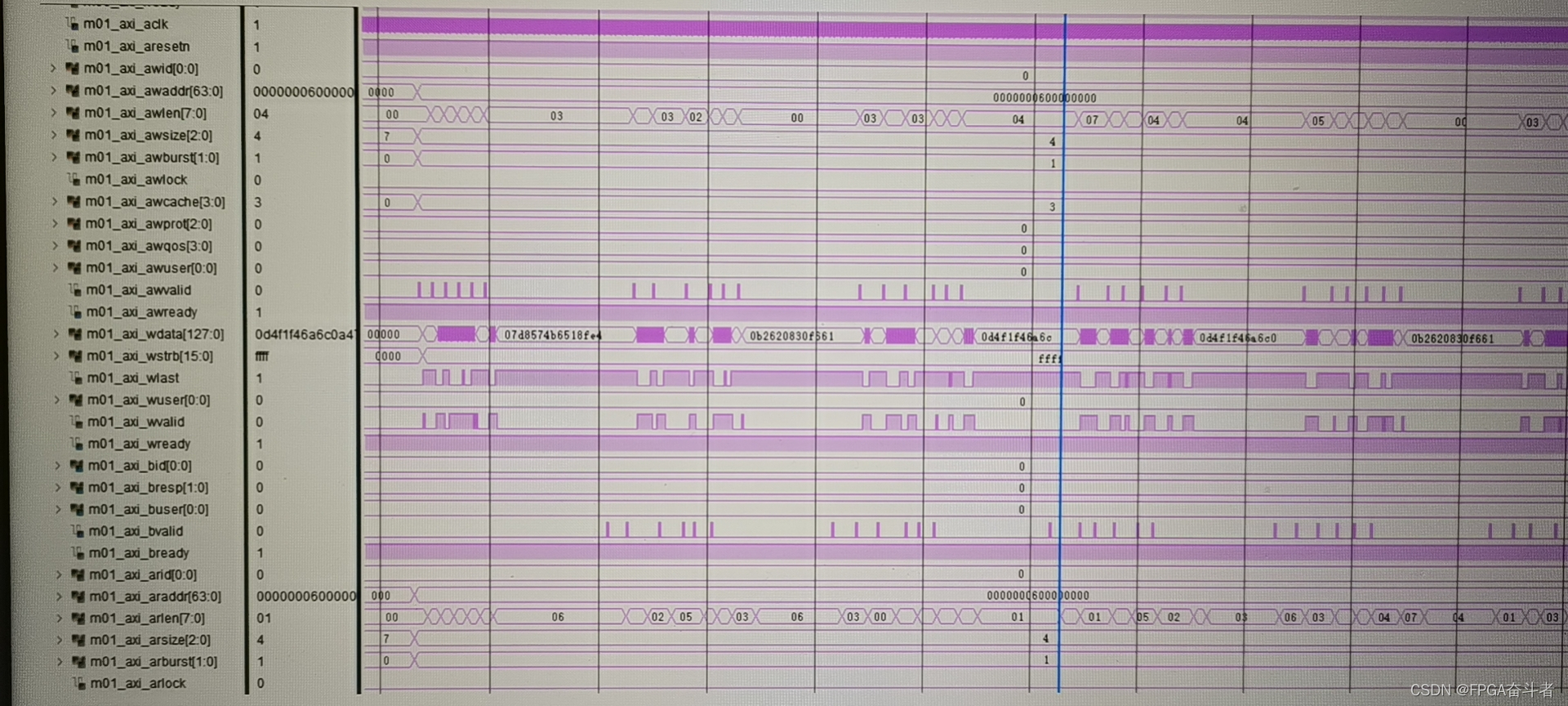

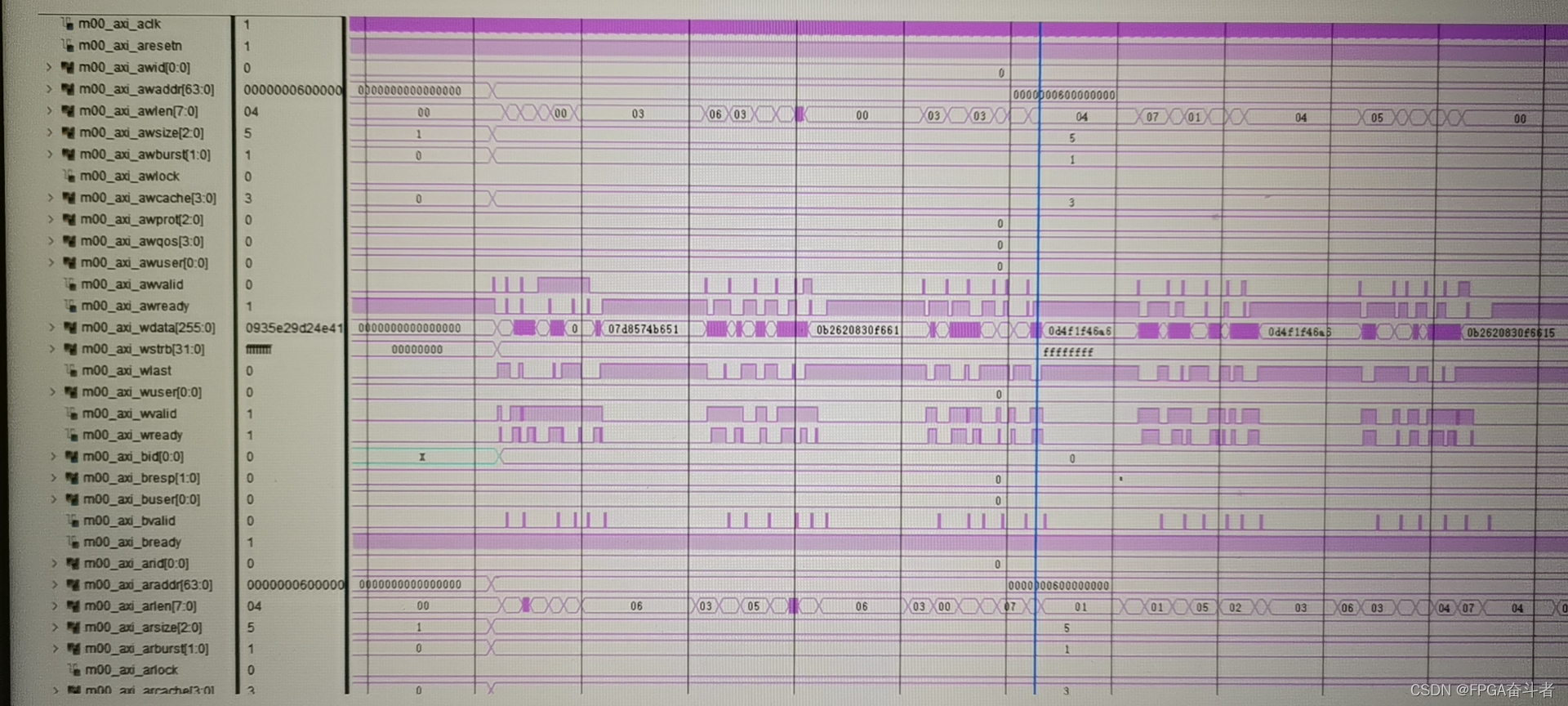

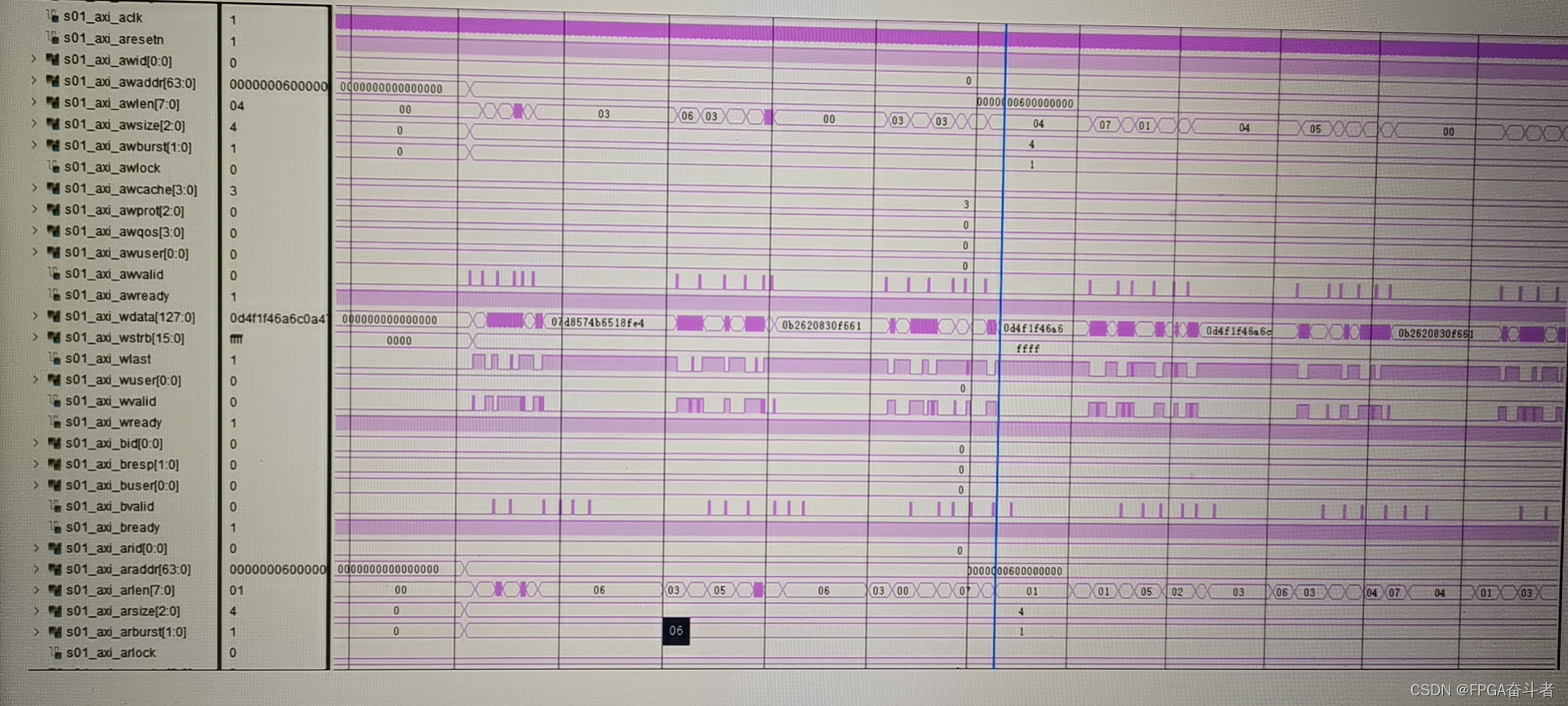

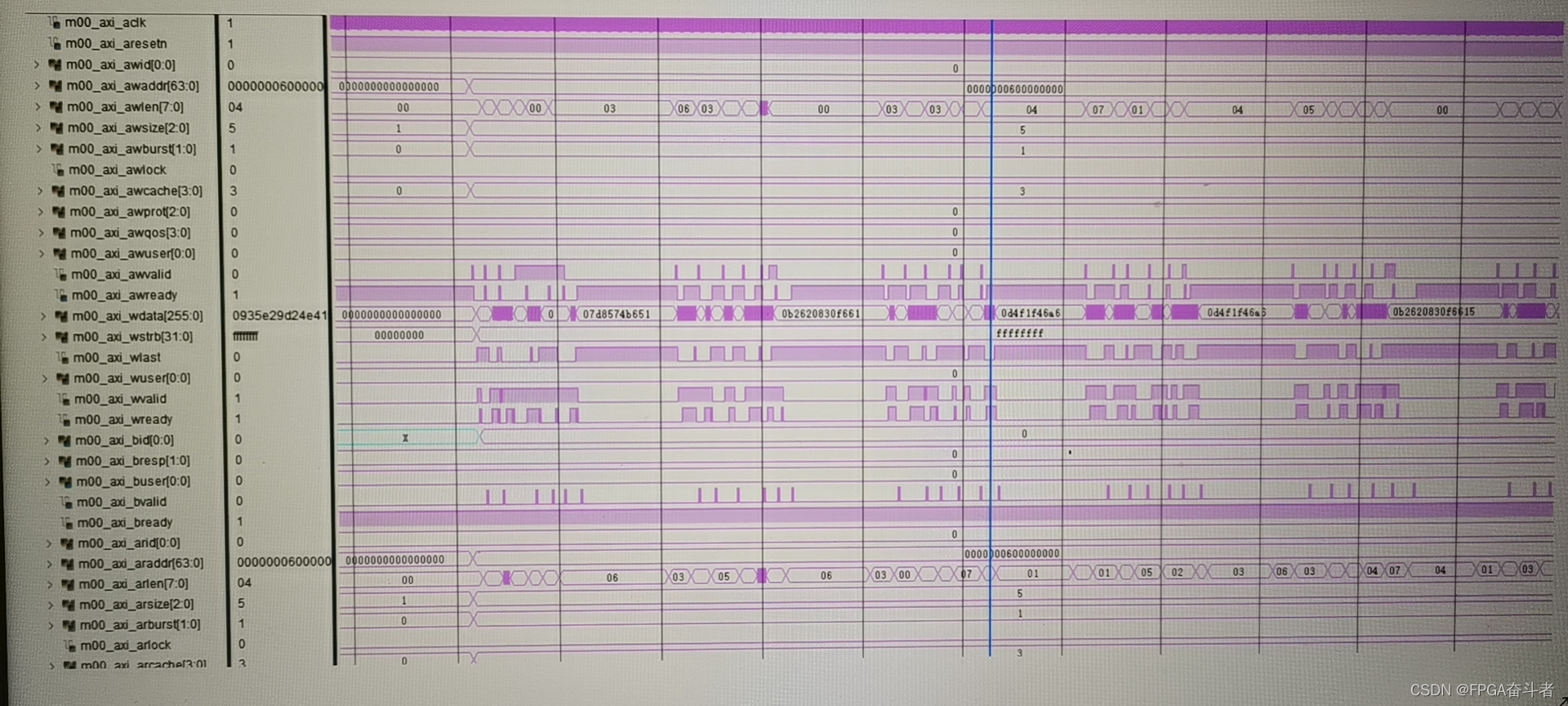

7、代码仿真如下

(1)

(2)

(3)

(4)

(5)

(6)

8、对其中的一组数据加延时,同样也可以使数据对齐,容忍度为FIFO的大小。

审核编辑:符乾江

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

数据

+关注

关注

8文章

7349浏览量

95025 -

总线

+关注

关注

10文章

3060浏览量

91869 -

AXI4

+关注

关注

0文章

21浏览量

9188

发布评论请先 登录

相关推荐

热点推荐

探索DS92LX1621/DS92LX1622:高速数据传输的理想选择

Channel Link III芯片组,为数据传输提供了强大的解决方案。下面,我们就来深入了解一下这款芯片组的特点、功能及应用。 文件下载: ds92lx1621.pdf 芯片

探索DS92LV0411/DS92LV0412:高速数据传输的理想选择

探索DS92LV0411/DS92LV0412:高速数据传输的理想选择 在电子设计领域,数据的高效、稳定传输一直是我们追求的目标。TI推出的DS92LV0411/DS92LV0412芯

探索DS100KR401:高速数据传输的理想中继器

探索DS100KR401:高速数据传输的理想中继器 在高速数据传输的领域中,信号的完整性和低功耗是至关重要的设计指标。今天,我们将深入探讨德州仪器(TI)的DS100KR401,一款专为高速数

高速数据传输利器:DS125DF111多协议2通道重定时器深度剖析

高速数据传输利器:DS125DF111多协议2通道重定时器深度剖析 在高速数据传输领域,信号的完整性和稳定性是至关重要的。今天,我们将深入探讨德州仪器(TI)的DS125DF111

RDMA设计4:技术需求分析2

开发。设计基于纯逻辑电路,可以脱离 MCU 控制独立运行,兼容 SoC 环境与纯逻辑环境。

(4)使用标准 AXI 总线接口,设计使用标准化的 AXI4 及

发表于 11-24 09:09

NVMe协议简介之AXI总线

向高速数据流传输的AXI4-Stream接口。如表1所示展示了三种类型接口的主要特点对比。

表1 三种类型AXI4接口对比

AXI4总线具有

发表于 05-17 10:27

SPI数据传输缓慢问题求解

我遇到了 SPI 数据传输速率问题。 尽管将 SPI 时钟频率设置为 20 MHz,但我只获得了 2 Kbps 的数据传输速率。 我正在以 115200 的波特率通过 UART 监控数据。

我正在 cyfxusbspidmamo

发表于 05-15 08:29

AXI4-FULL总线多通道数据传输,合并生成一组数据的讨论

AXI4-FULL总线多通道数据传输,合并生成一组数据的讨论

评论