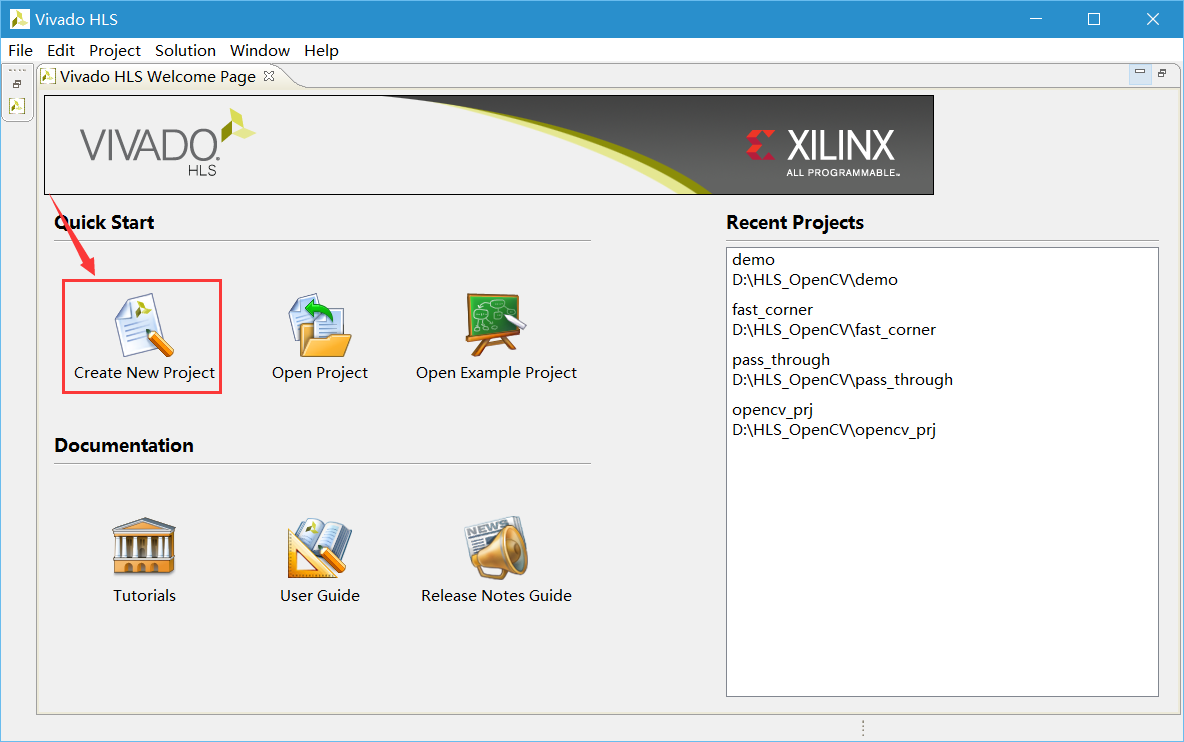

先从运行一个创建一个项目开始吧。

首先打开Vivado设计套件Vivado HLS 2015.4;

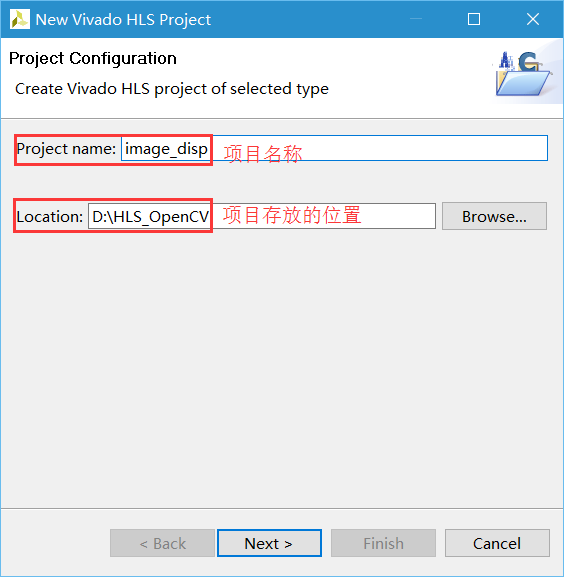

输入项目的名称和存放的位置;

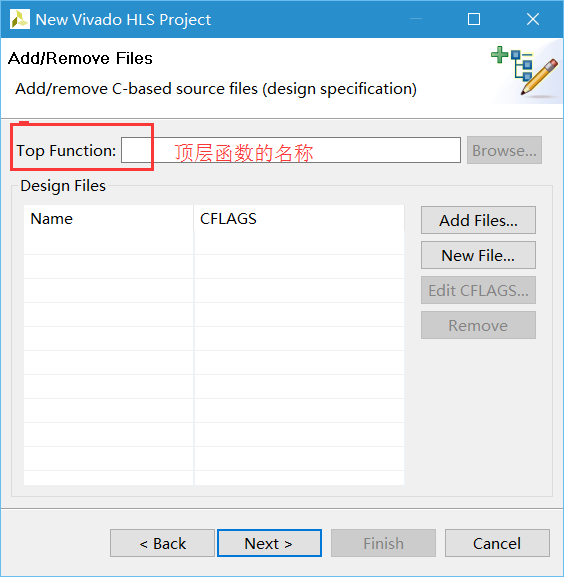

点击下一步,输入设计顶层函数的名称,接着下一步;

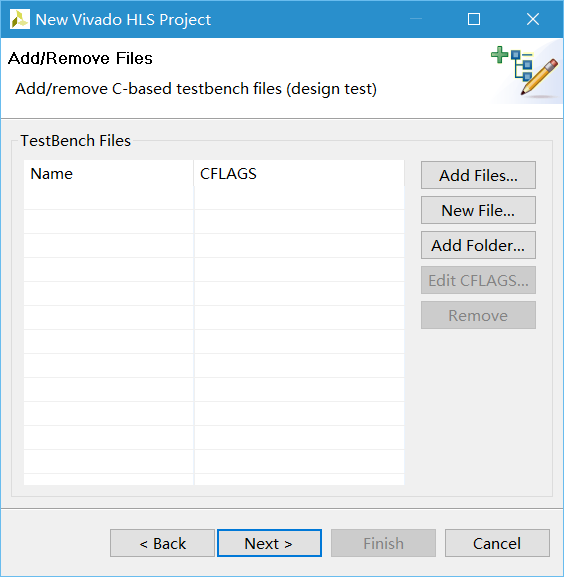

暂时不需要填写,直接下一步;

解决方案的名字默认 (solution1)就好, 时钟周期根据需要自己设,这里我设(10 ns), 时钟的不确定性一般为12.5%,接着选择器件,最后“finish”。

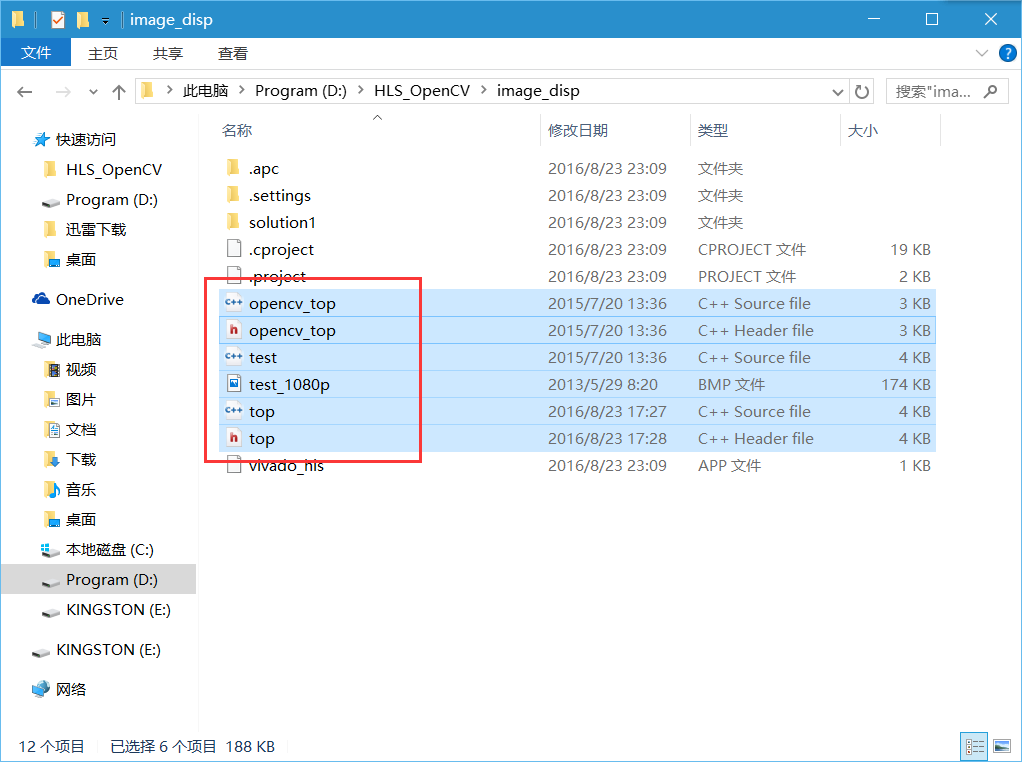

将该例程的设计文件和testbench全部复制到刚才创建的项目目录下:

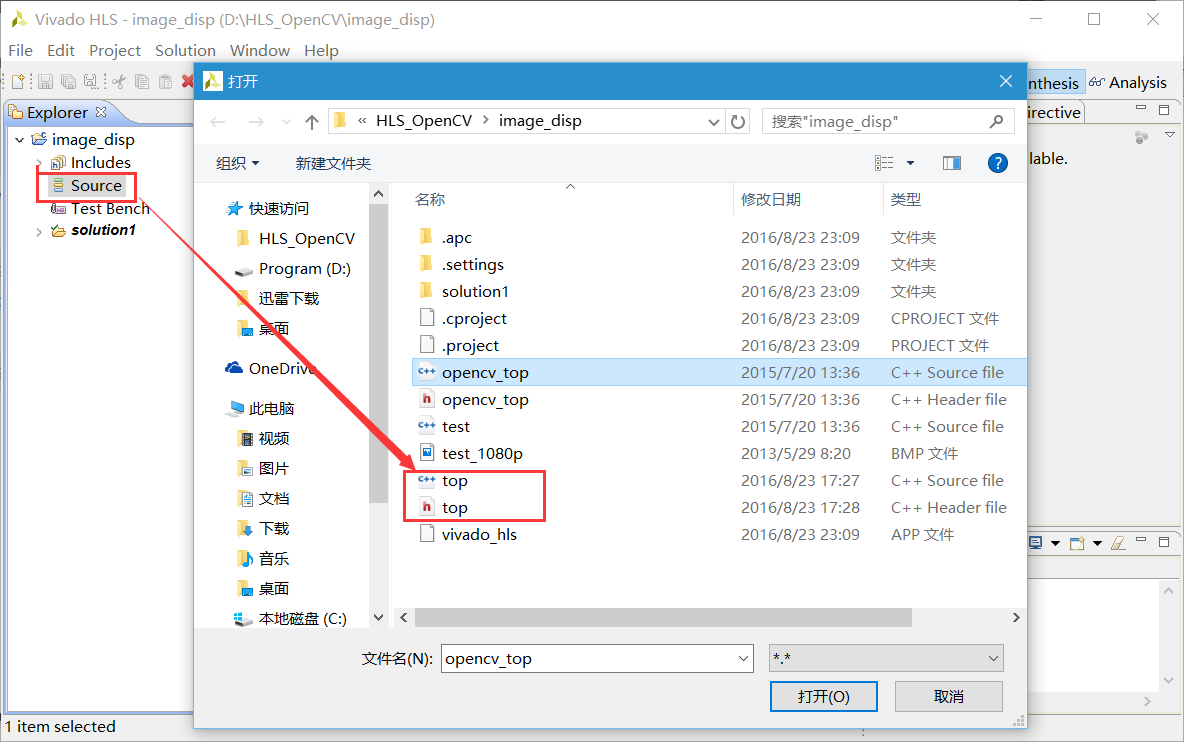

在设计资源窗口右击“Source”,添加设计文件;

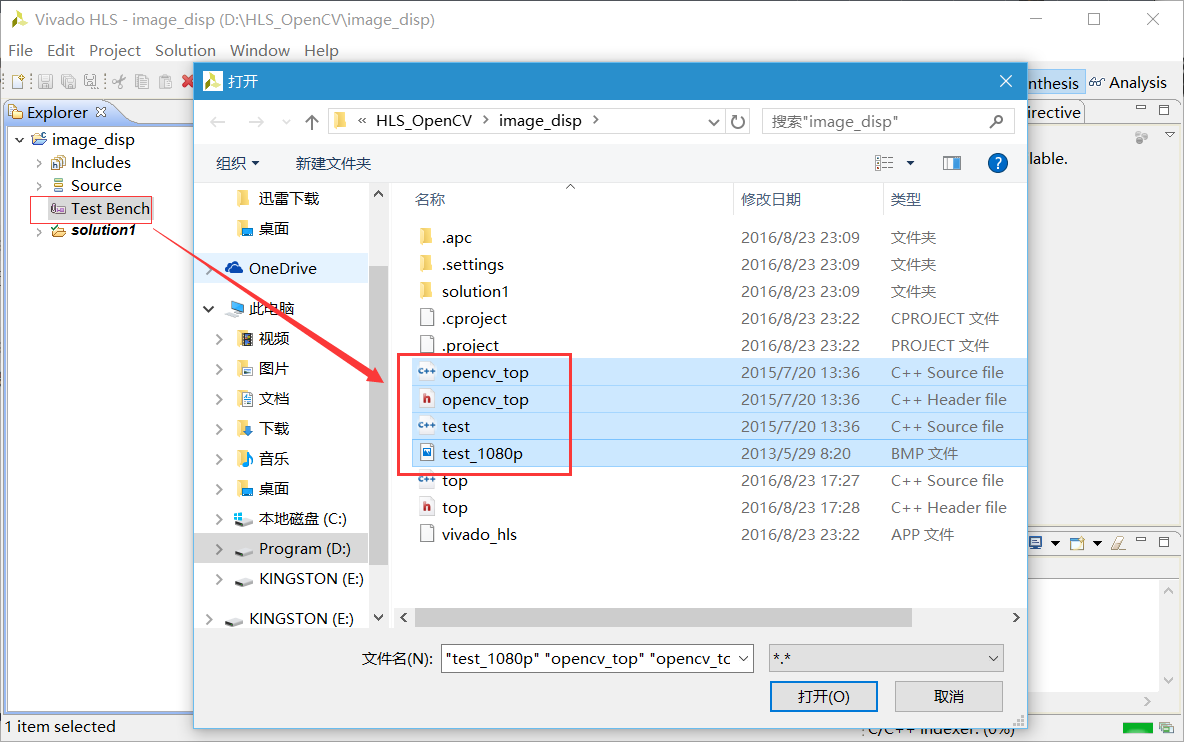

再接着右击“Test Bench”,添加文件;

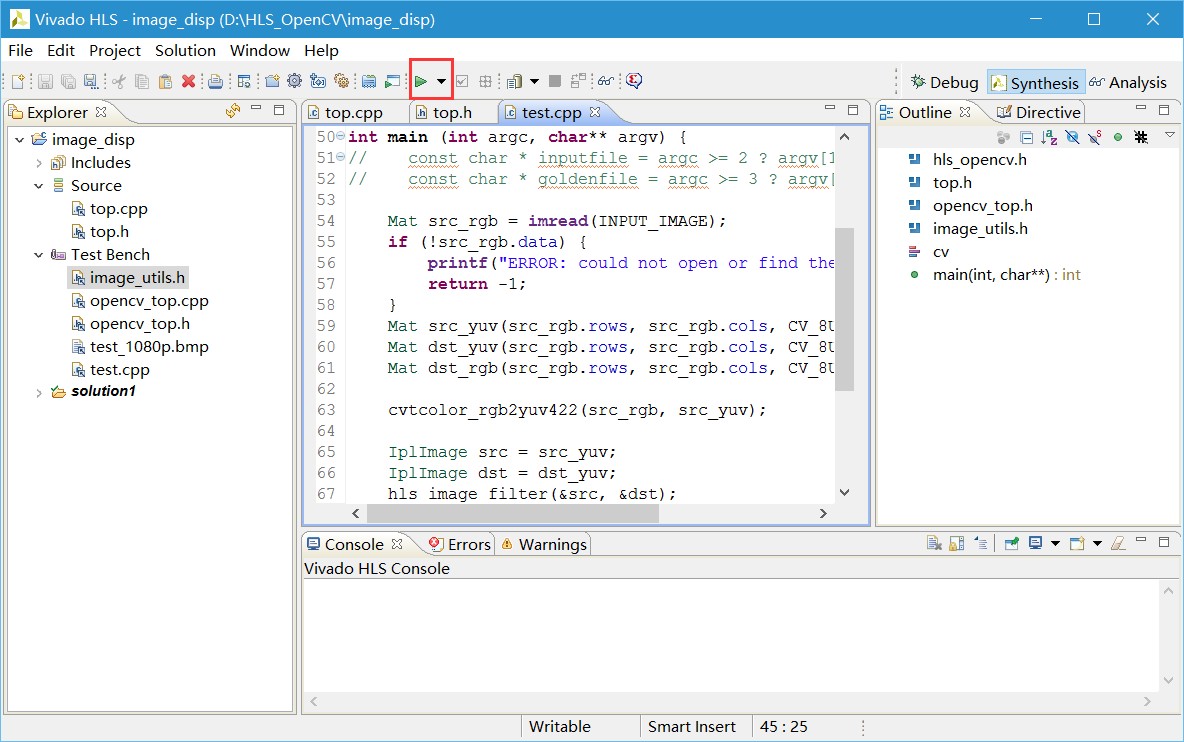

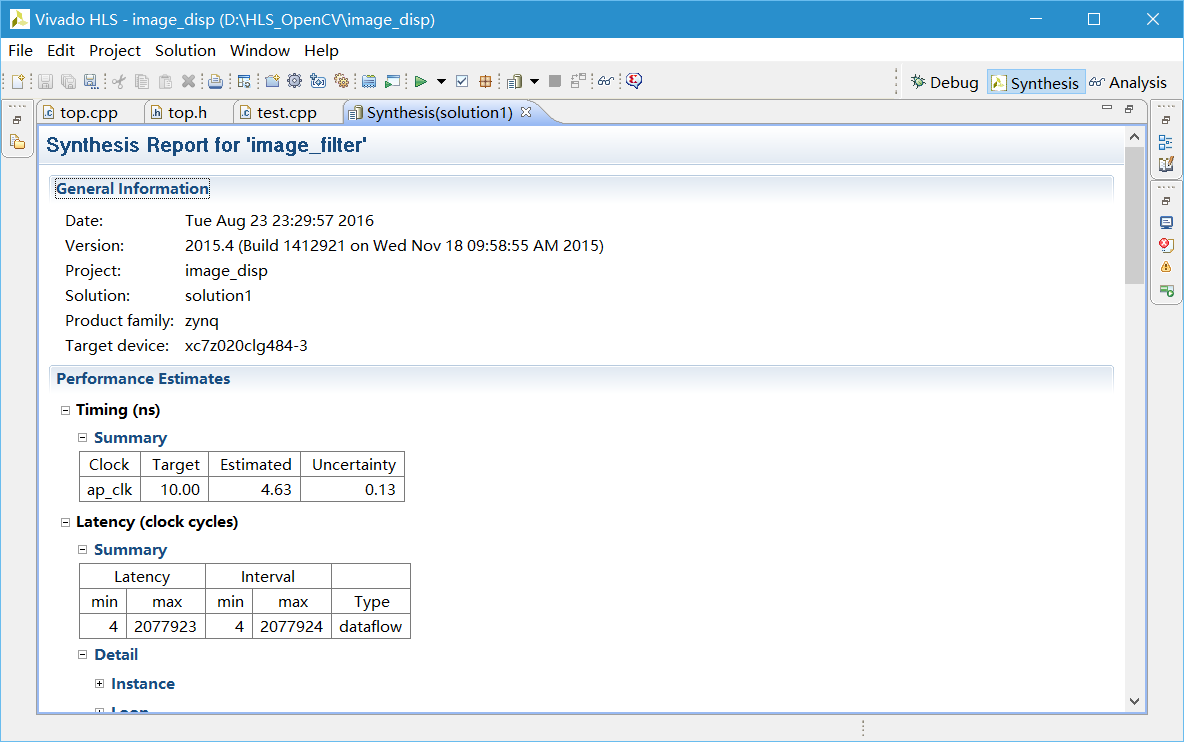

至此,项目建设完成。接着进行综合仿真,验证设计。 点击“Run C Snthry”。

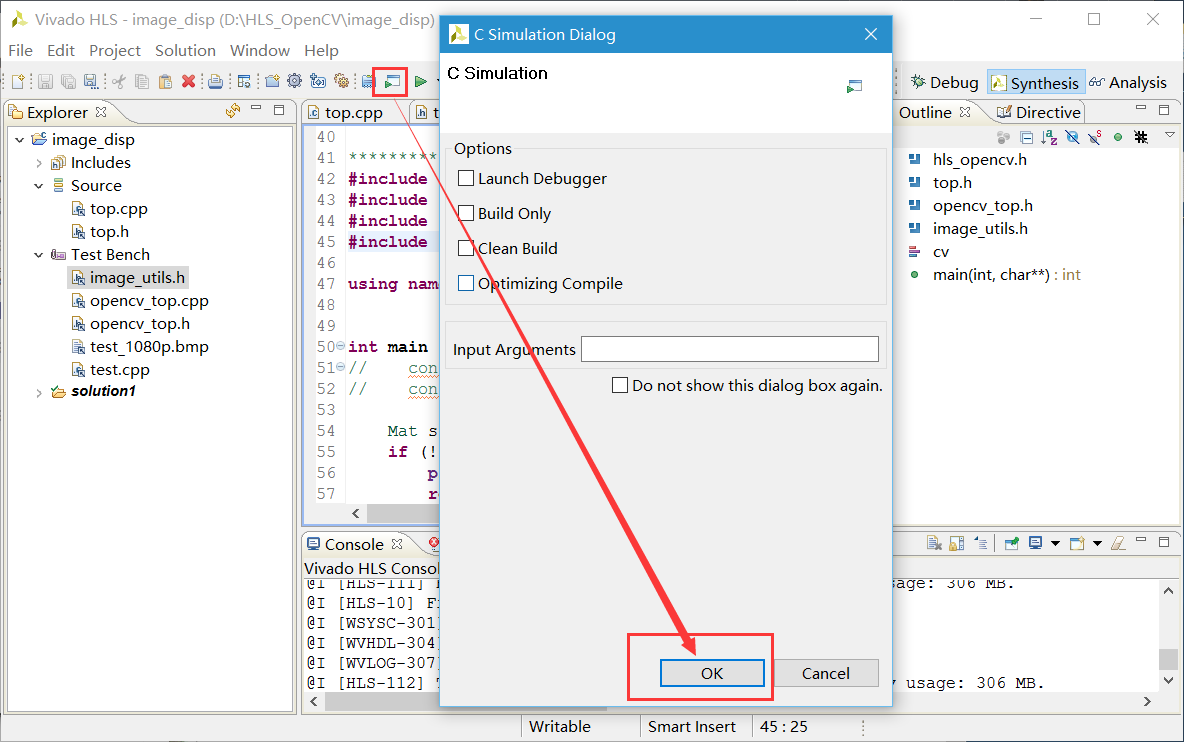

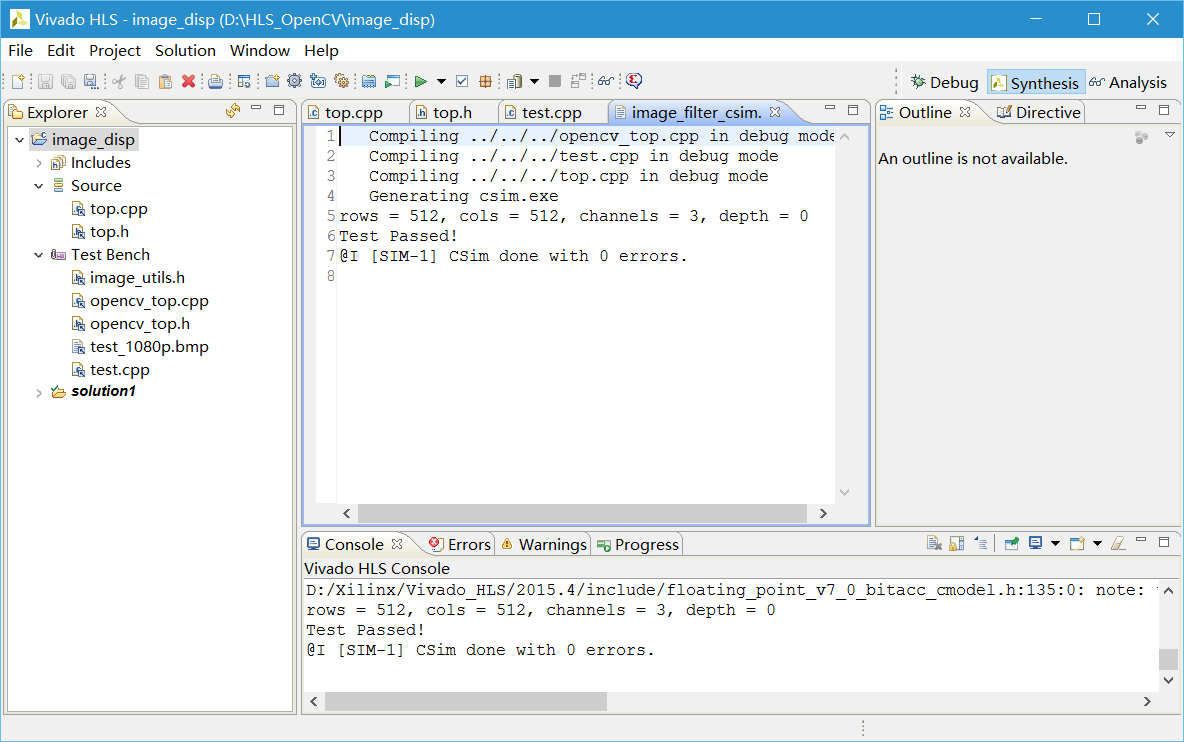

点击“Run C Simulation”,接着点击“OK”;

至此,此项目在没有硬件调试的前提下算是成功运行了。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

HDL

+关注

关注

8文章

332浏览量

49047 -

模型

+关注

关注

1文章

3819浏览量

52270 -

Vivado

+关注

关注

19文章

860浏览量

71402

发布评论请先 登录

相关推荐

热点推荐

功率循环基础篇(三)——从LESIT到CIPS,功率模块寿命预测的演进

功率循环(Power Cycling, PC)测试结果经过长期积累后,人们逐步建立了基于经验数据的寿命模型(Empirical Lifetime Models)。这些模型不是从物理机理出发推导的,而是通过大量实测数据统计拟合得出

HLS设计中的BRAM使用优势

高层次综合(HLS)是一种将高级编程语言(如C、C++或SystemC)转换为硬件描述语言(HDL)的设计方法。在FPGA设计中,设计者可以

端侧大模型上车:从“语音助手”到“车内 AI 智能体”的跃迁革命

2025年,智能汽车的座舱不再只是“语音助手”的舞台,而是一个搭载生成式AI和大语言模型(LLM)的智能体。从云端示范到车内落地,这一跨越不仅改变了人机交互的边界,更重构了汽车作为“第三

从数据到模型:如何预测细节距键合的剪切力?

预估其剪切力?行业内的研究数据为我们揭示了可能性。今天,科准测控小编将带您了解如何基于实验数据建立并应用预测模型,实现从“测量”到“预估”的关键跨越。

一、从平方定律到经验公式

直观上

发表于 01-08 09:45

RA8P1部署ai模型指南:从训练模型到部署 | 本周六

在嵌入式边缘AI中,如何把“训练好的模型”稳定地“跑在板子上”,决定了项目能否落地。我们带你基于RA8P1平台,跑通从数据准备、模型训练、量化转换,到工程部署的整个流程,帮助你快速实现

vcs和vivado联合仿真

文档中明确描述vivado2021.2版本对应VCS的版本是2020.12,由于license问题所以选择vcs2018的版本;虽然目前与官方的版本不匹配,但是不影响正常使用;

使用tcl界面

发表于 10-24 07:28

如何在vivadoHLS中使用.TLite模型

, output_stream); // 从输出流中读取输出数据到缓冲区 // 根据模型的输出形状进行相应的读取和处理}5. 数据处理

根据模型的输出形状,

发表于 10-22 06:29

干货分享 | TSMaster MBD模块全解析:从模型搭建到自动化测试的完整实践

在汽车电子MBD开发中,TSMasterMBD模块深度集成于TSMaster先进的总线分析、仿真与测试平台,旨在为工程师提供一套从模型自动编译、代码集成到自动化测试的端到端无缝解决方案

如何在Unified IDE中创建视觉库HLS组件

Vivado IP 流程(Vitis Unified),在这篇 AMD Vitis HLS 系列 3 中,我们将介绍如何使用 Unified IDE 创建 HLS 组件。这里采用“自下而上”的流程,

使用AMD Vitis Unified IDE创建HLS组件

这篇文章在开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE) 的基础上撰写,但使用的是 AMD Vitis Unified IDE,而不是之前传统版本的 Vitis HLS

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado

从FA模型切换到Stage模型时:module的切换说明

module的切换

从FA模型切换到Stage模型时,开发者需要将config.json文件module标签下的配置迁移到module.json5配置文件module标签下,具体差异

发表于 06-05 08:16

Vivado HLS从HDL到模型和C的描述

Vivado HLS从HDL到模型和C的描述

评论